Patents

Literature

98 results about "General purpose computation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

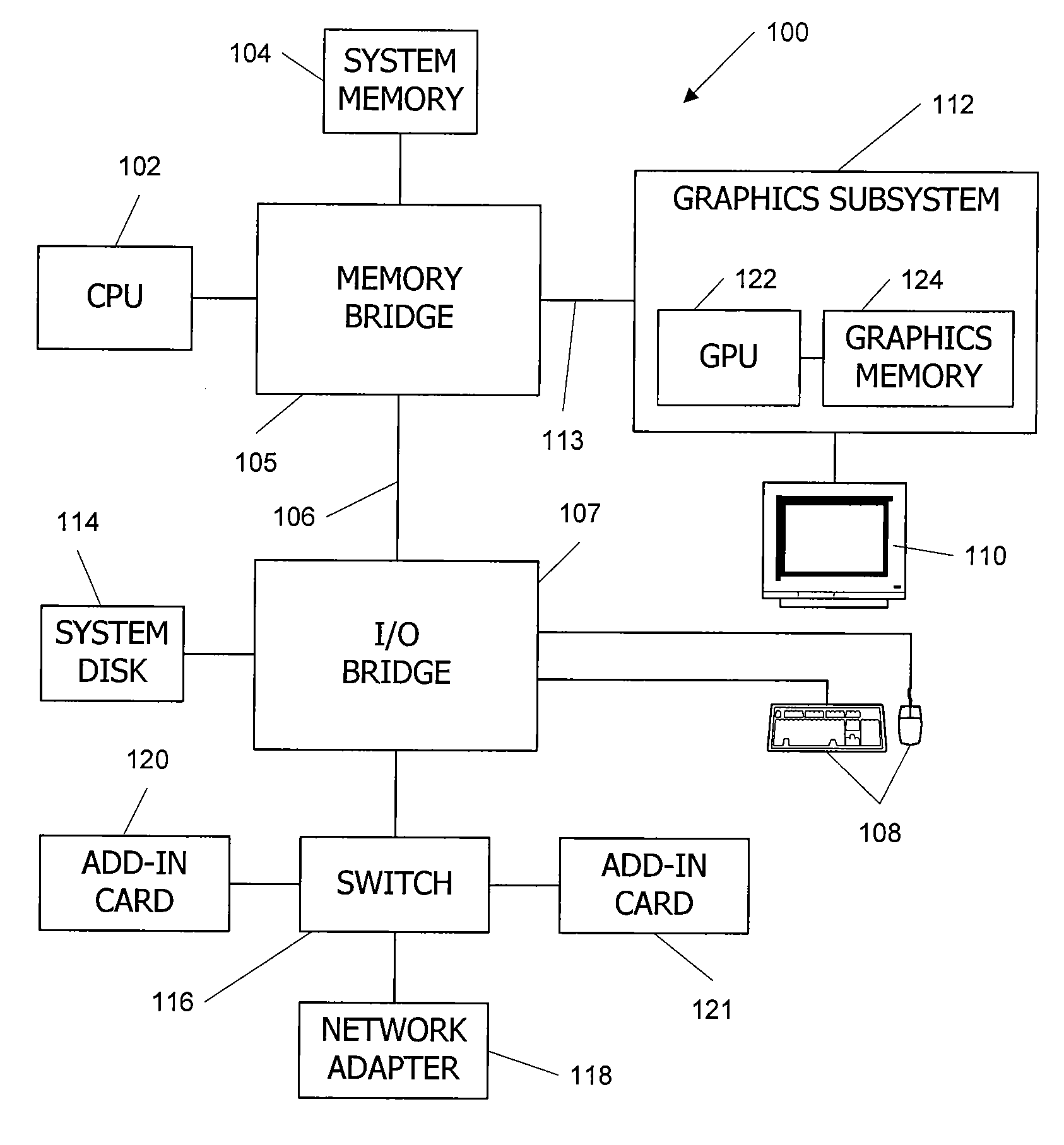

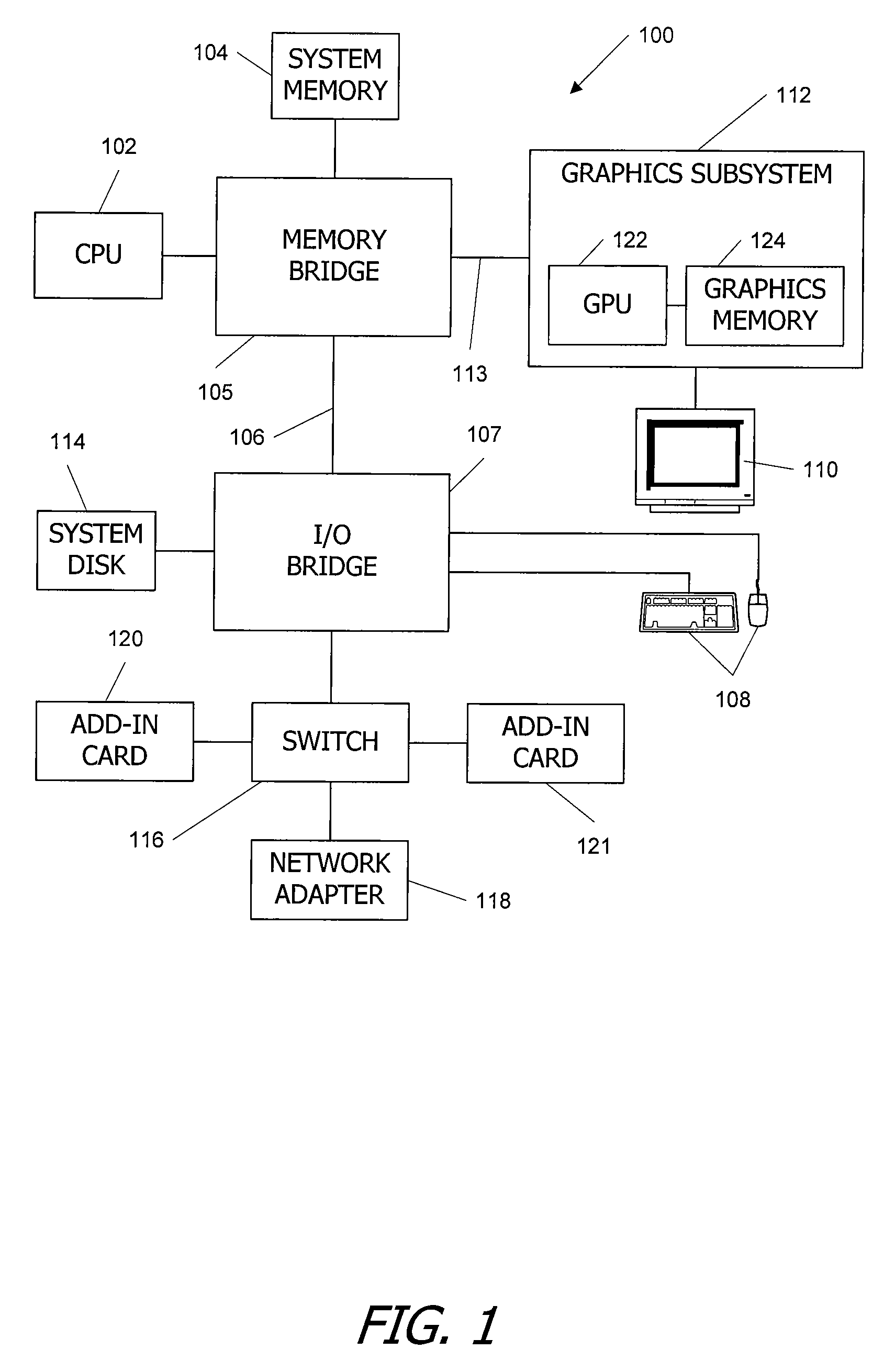

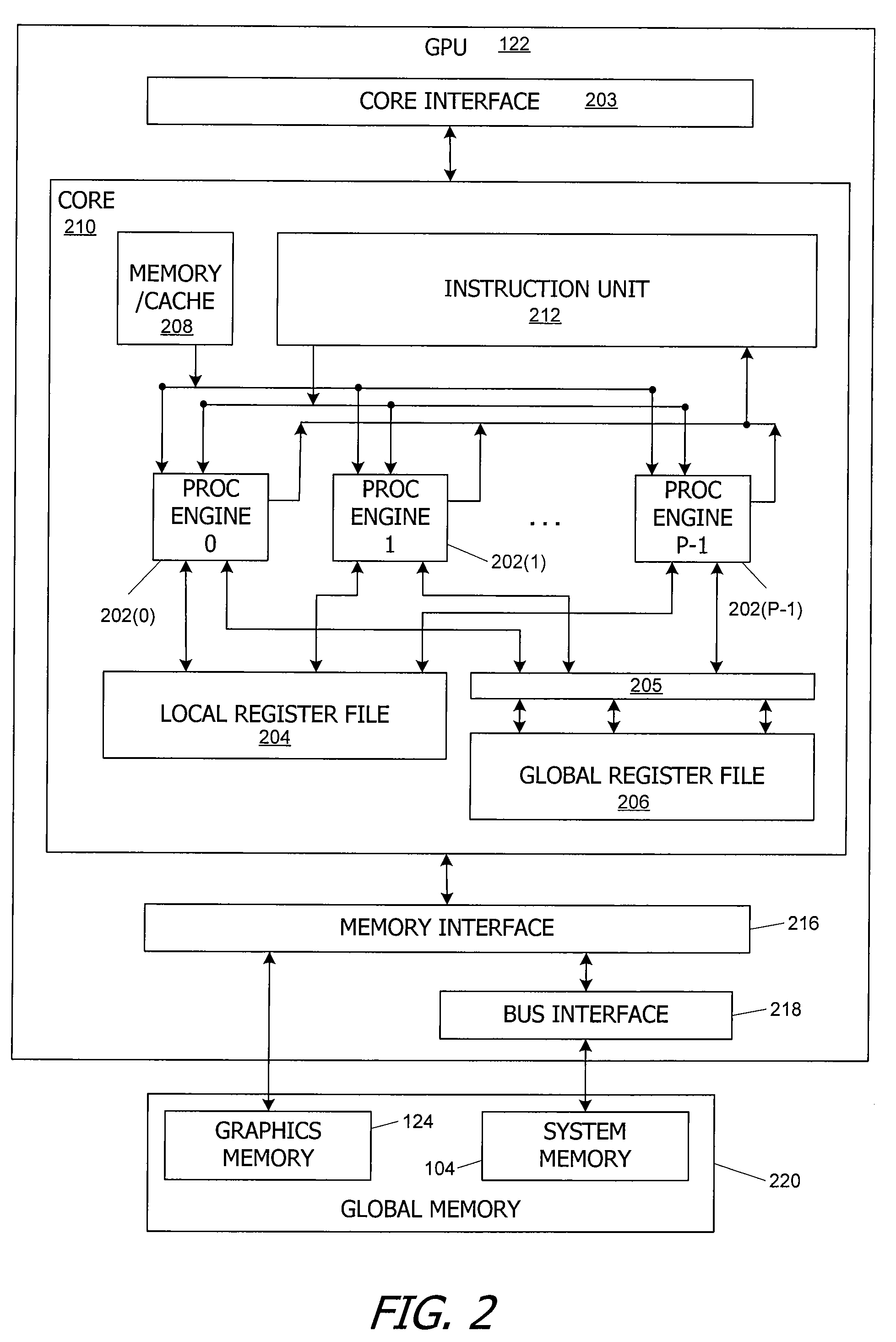

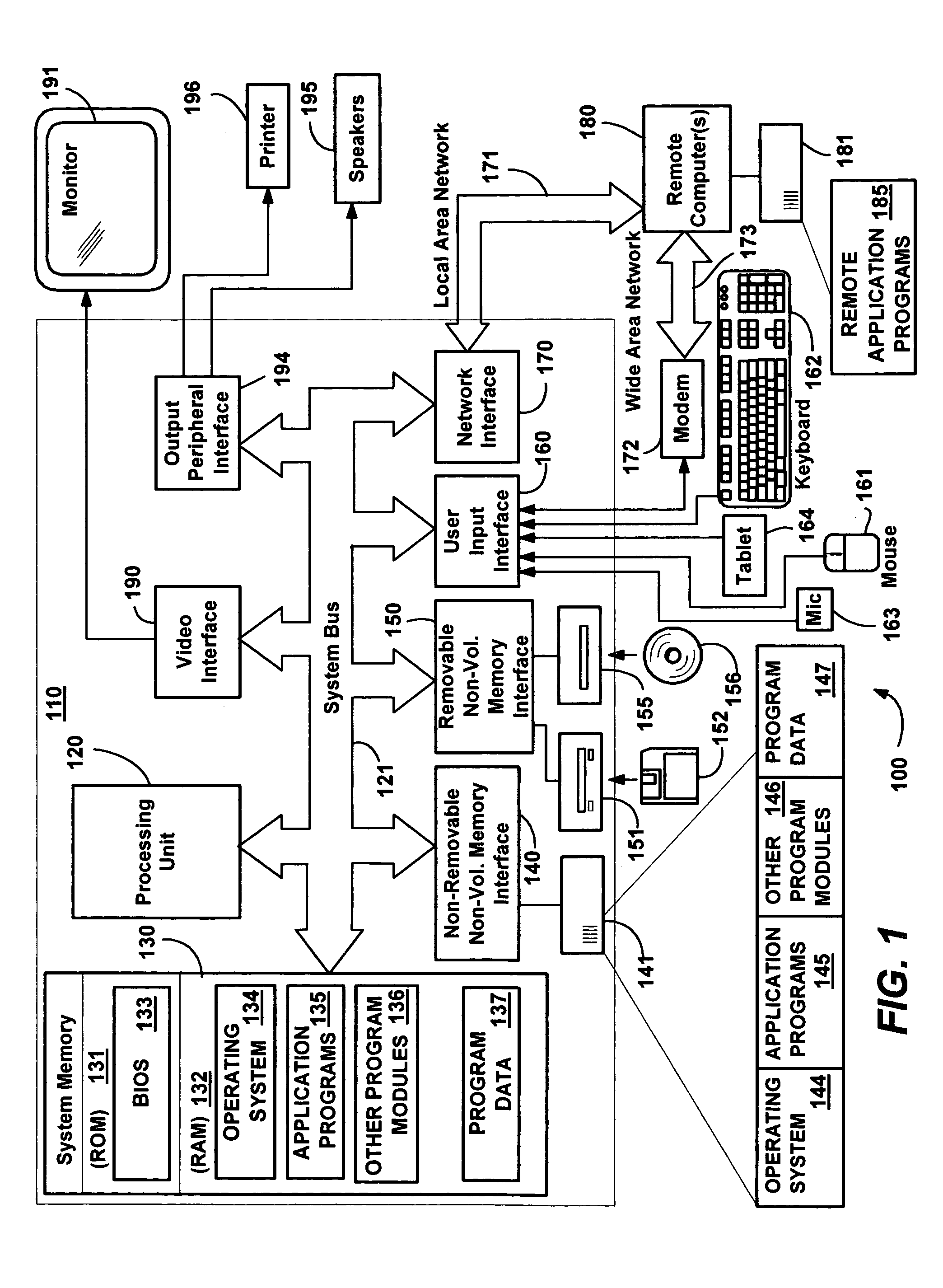

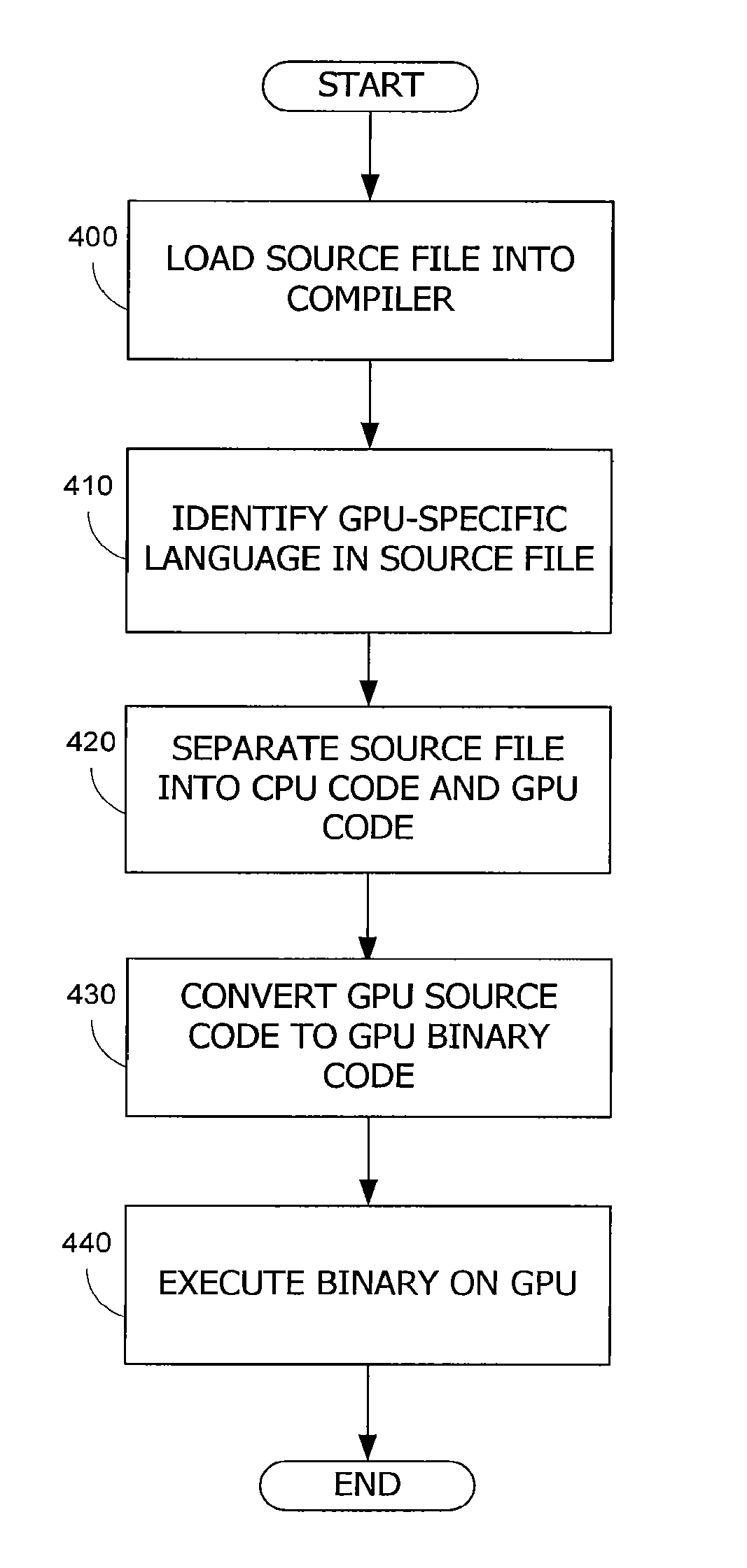

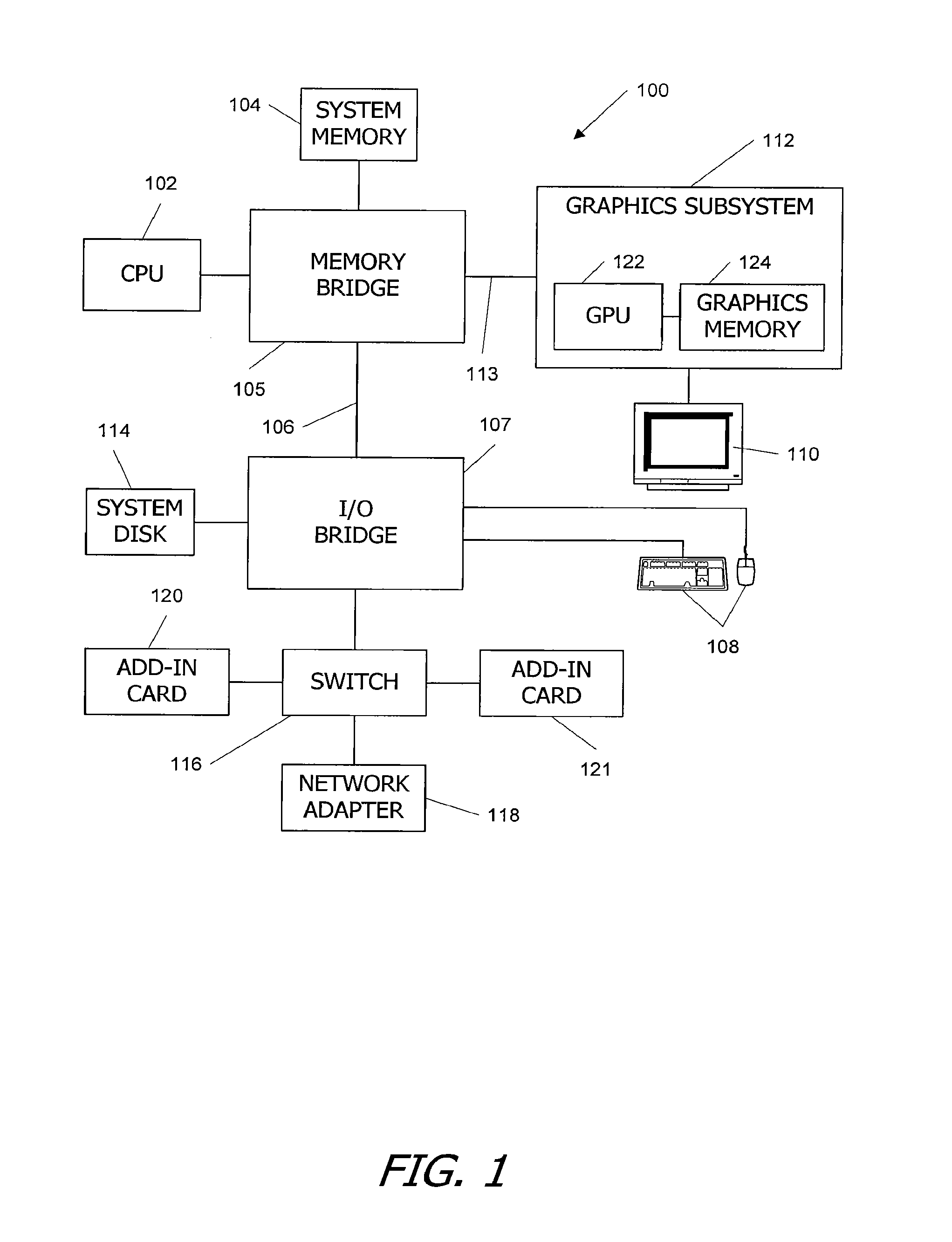

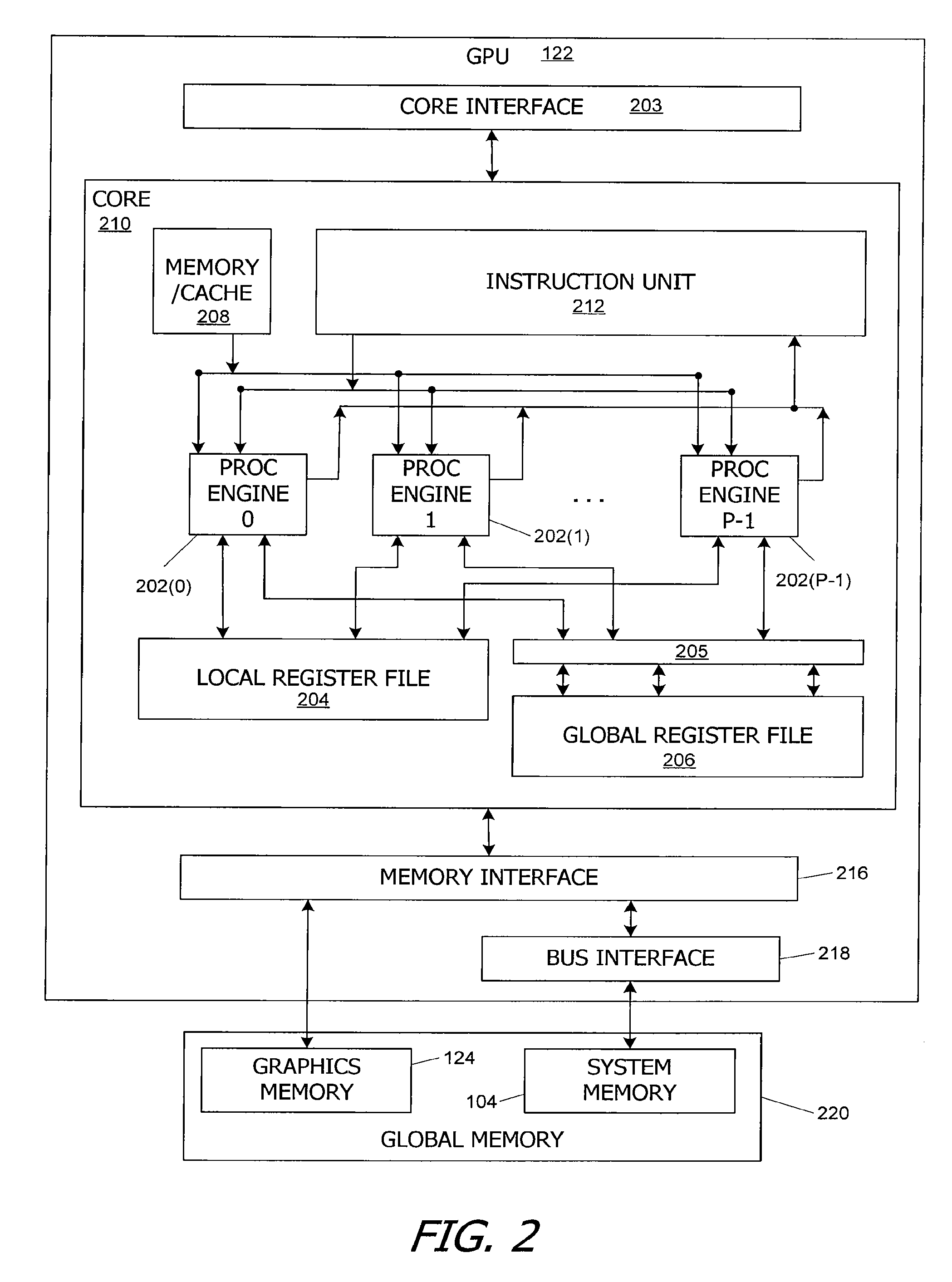

C/c++ language extensions for general-purpose graphics processing unit

A general-purpose programming environment allows users to program a GPU as a general-purpose computation engine using familiar C / C++ programming constructs. Users may use declaration specifiers to identify which portions of a program are to be compiled for a CPU or a GPU. Specifically, functions, objects and variables may be specified for GPU binary compilation using declaration specifiers. A compiler separates the GPU binary code and the CPU binary code in a source file using the declaration specifiers. The location of objects and variables in different memory locations in the system may be identified using the declaration specifiers. CTA threading information is also provided for the GPU to support parallel processing.

Owner:NVIDIA CORP

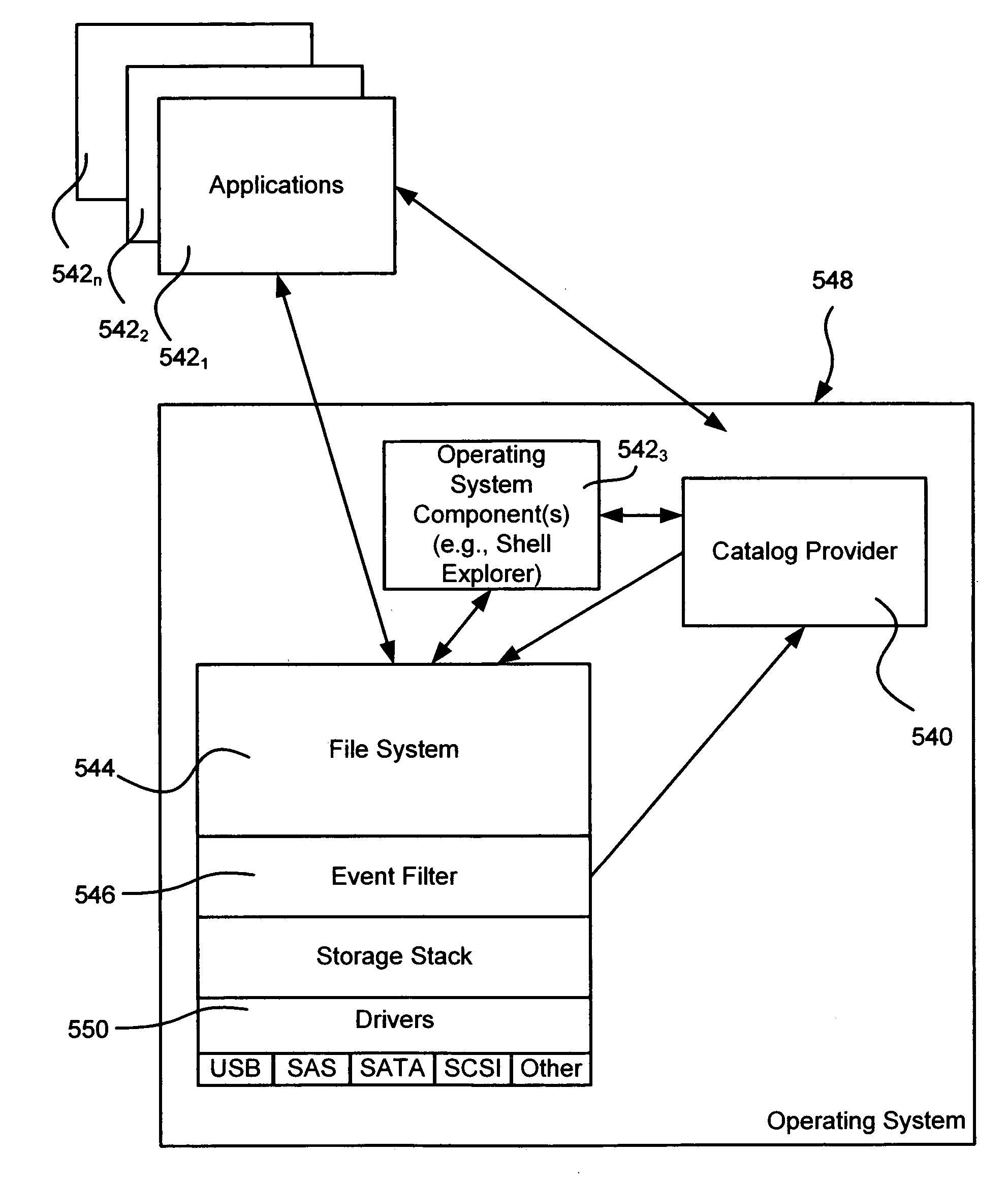

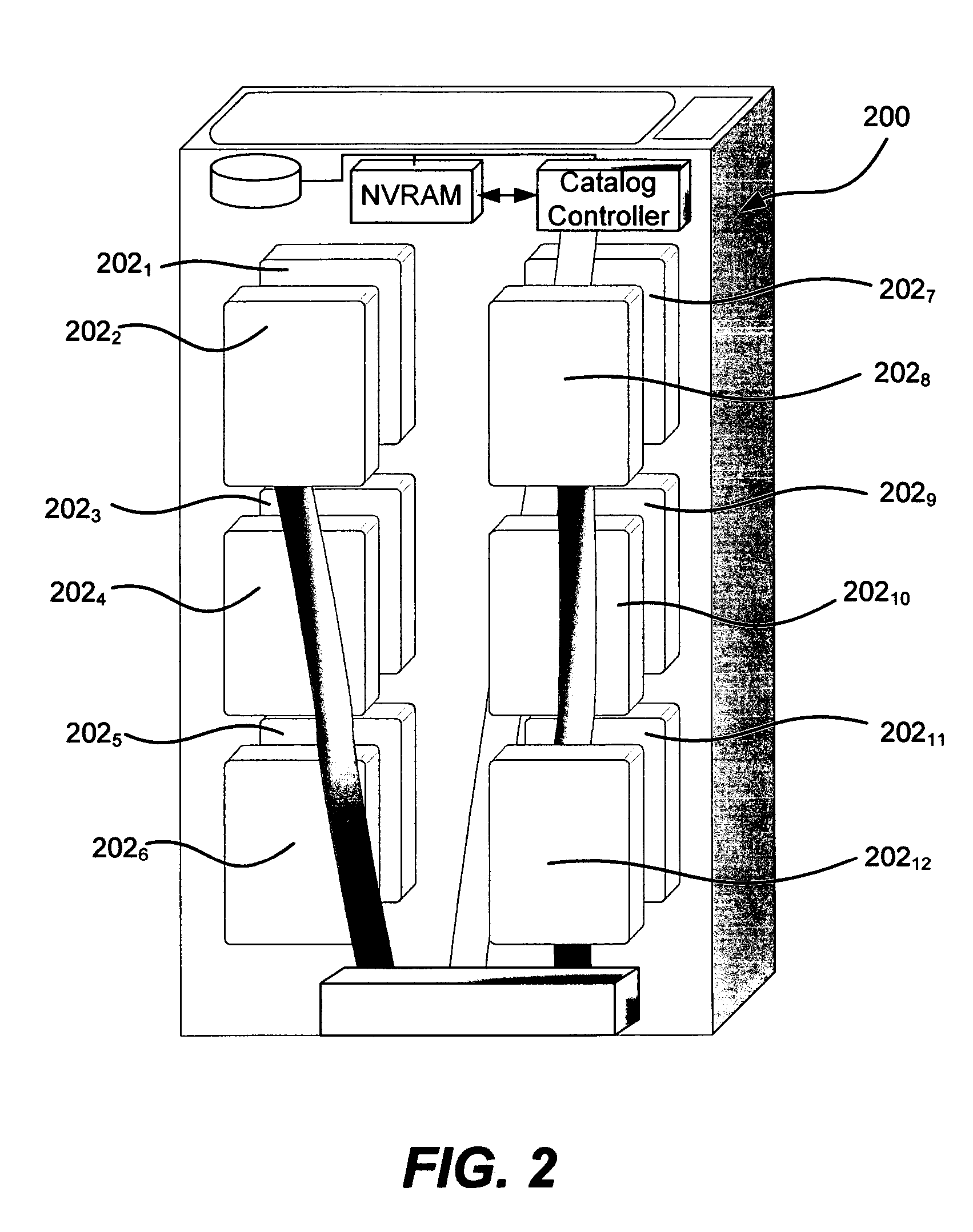

Electronic labeling for offline management of storage devices

InactiveUS20060080359A1Function increaseDigital data processing detailsSpecial data processing applicationsFile systemDisplay device

A system and method using hardware and software components enable a storage module to maintain information about an associated storage device and its content such that the information is accessible when the storage device is offline or in a low power configuration. A general-computing host system connects to the storage module via a pluggable interface to provide information to a nonvolatile memory cache on the storage module. The storage module includes a separate power source, an output display, input buttons, and a module controller. The host system includes an application and host platform for processing file-system related events to send records to the module controller to automatically update a catalog representing storage device information in the nonvolatile memory. When offline, the user may display the catalog information and use the buttons to navigate among it. The host system may also allow the user to interactively review and modify the catalog.

Owner:MICROSOFT TECH LICENSING LLC

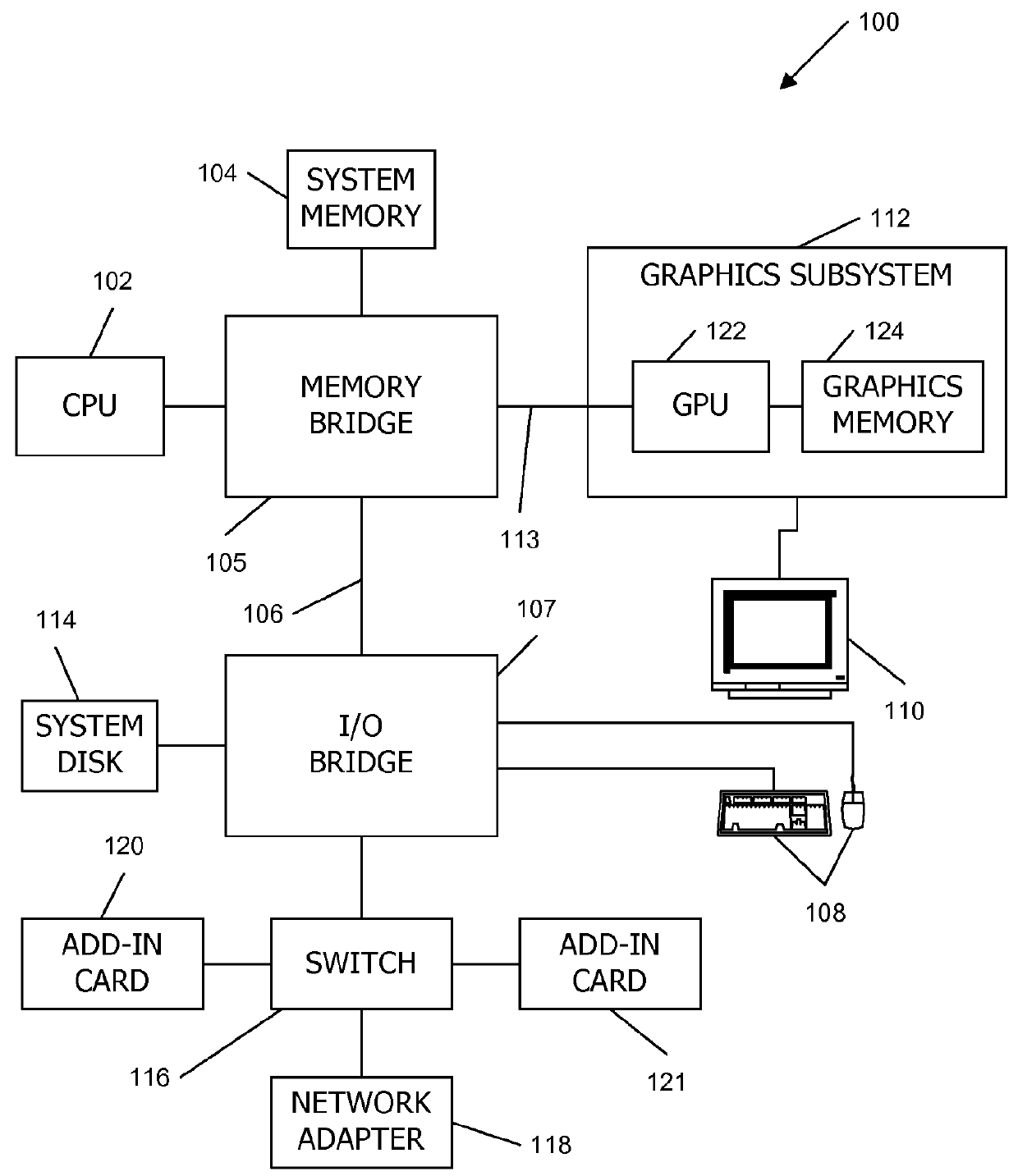

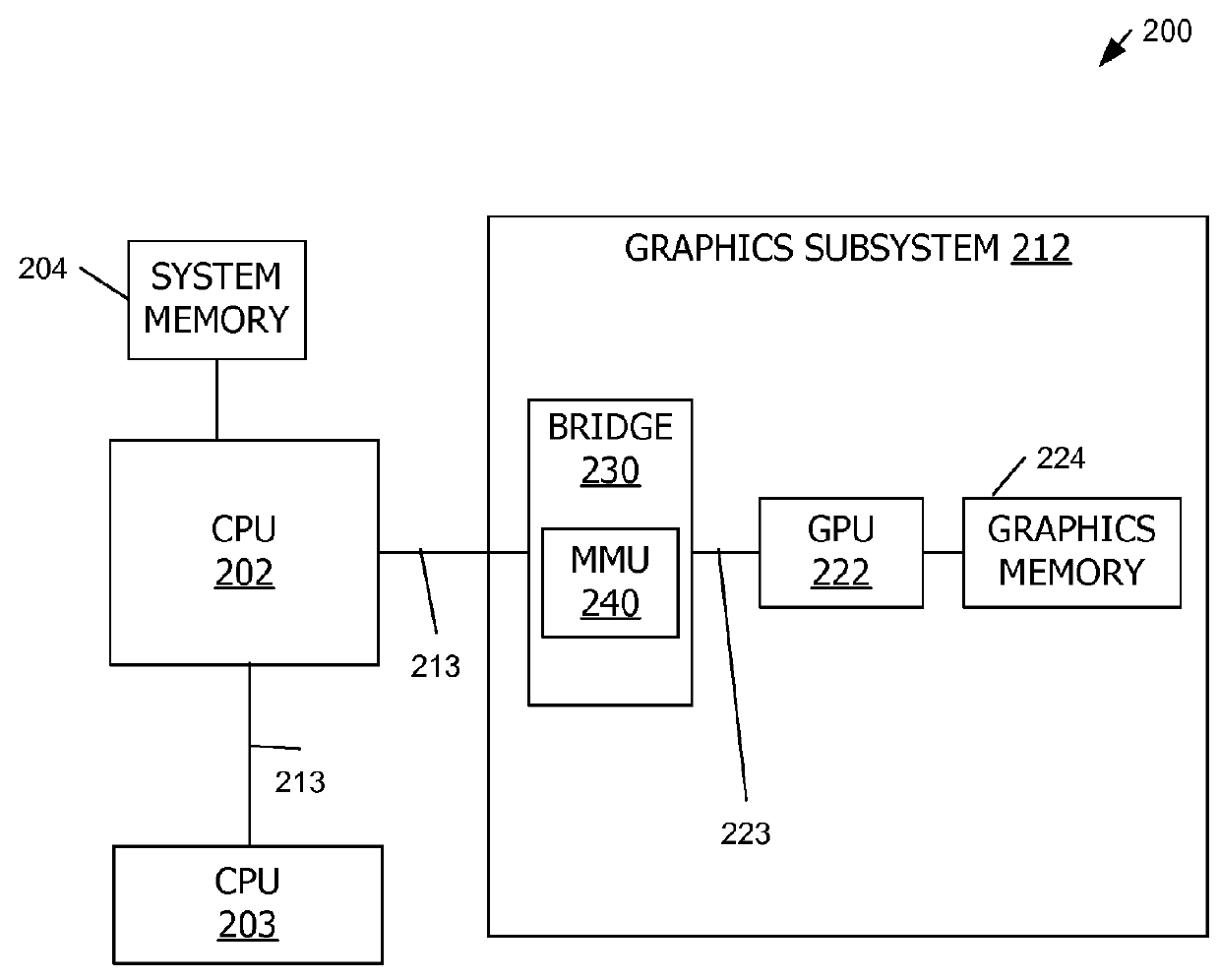

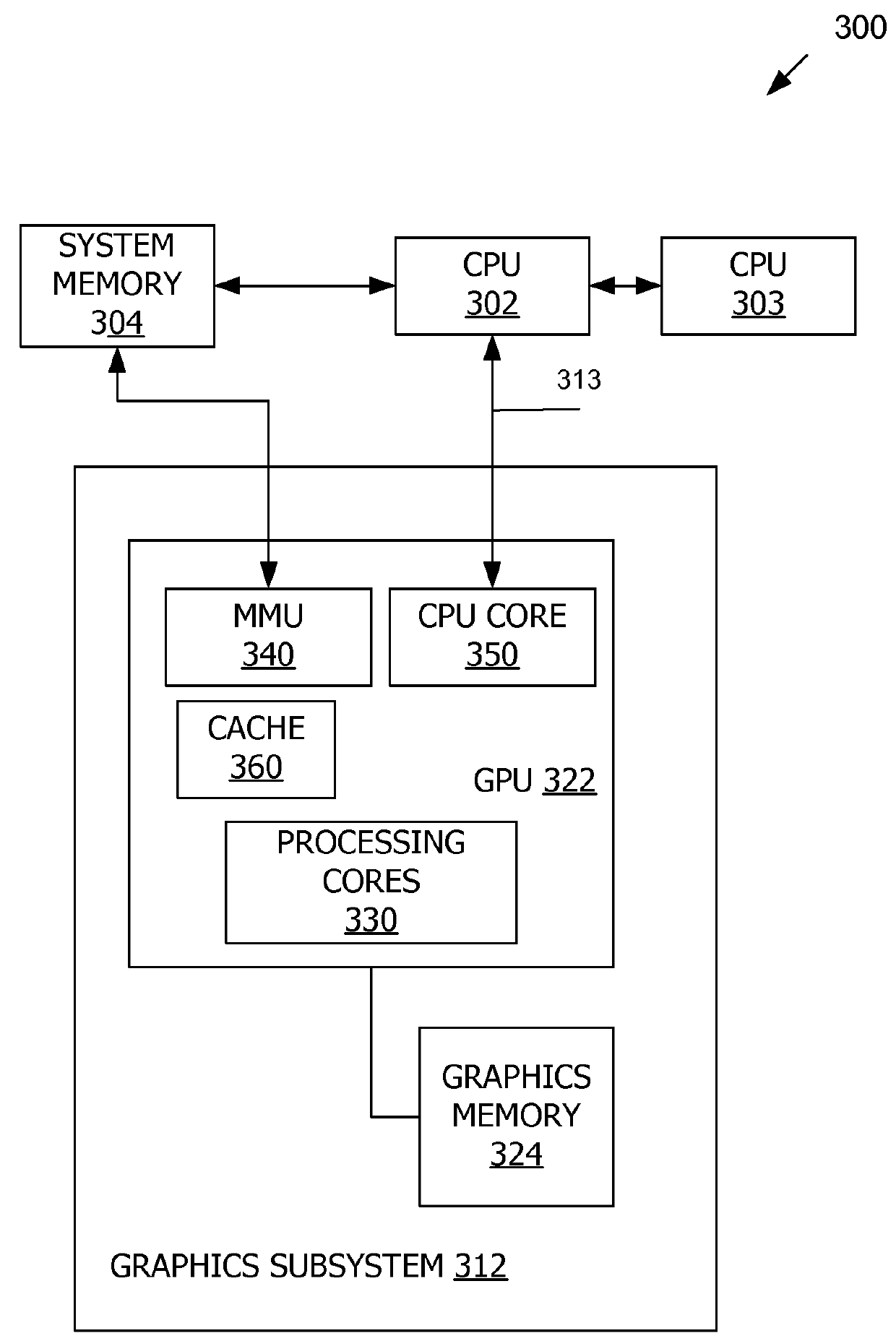

Graphics processor with memory management unit and cache coherent link

ActiveUS8860741B1Increase chanceIncrease clock speedMemory architecture accessing/allocationResource allocationGeneral purposeGraphics

Owner:NVIDIA CORP

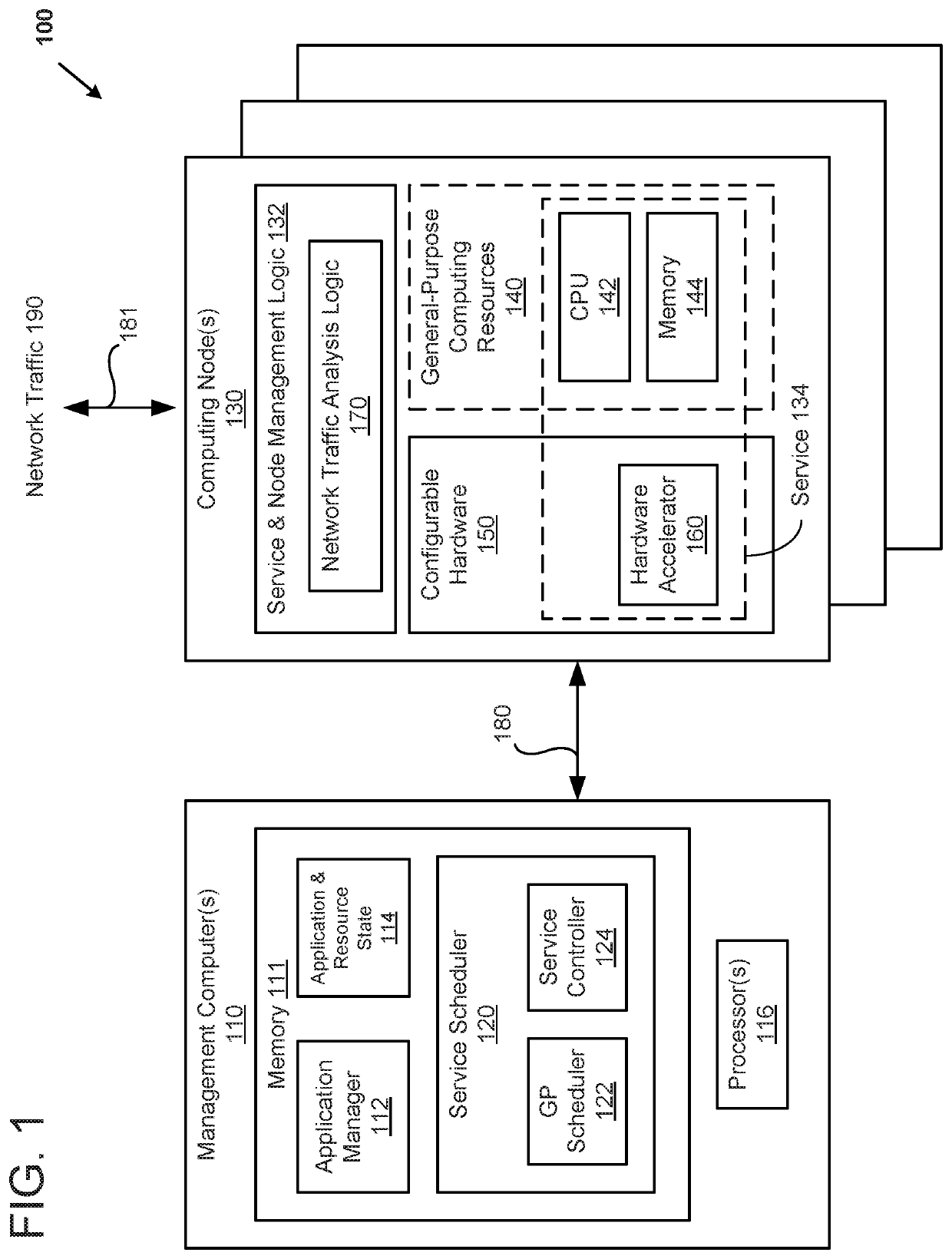

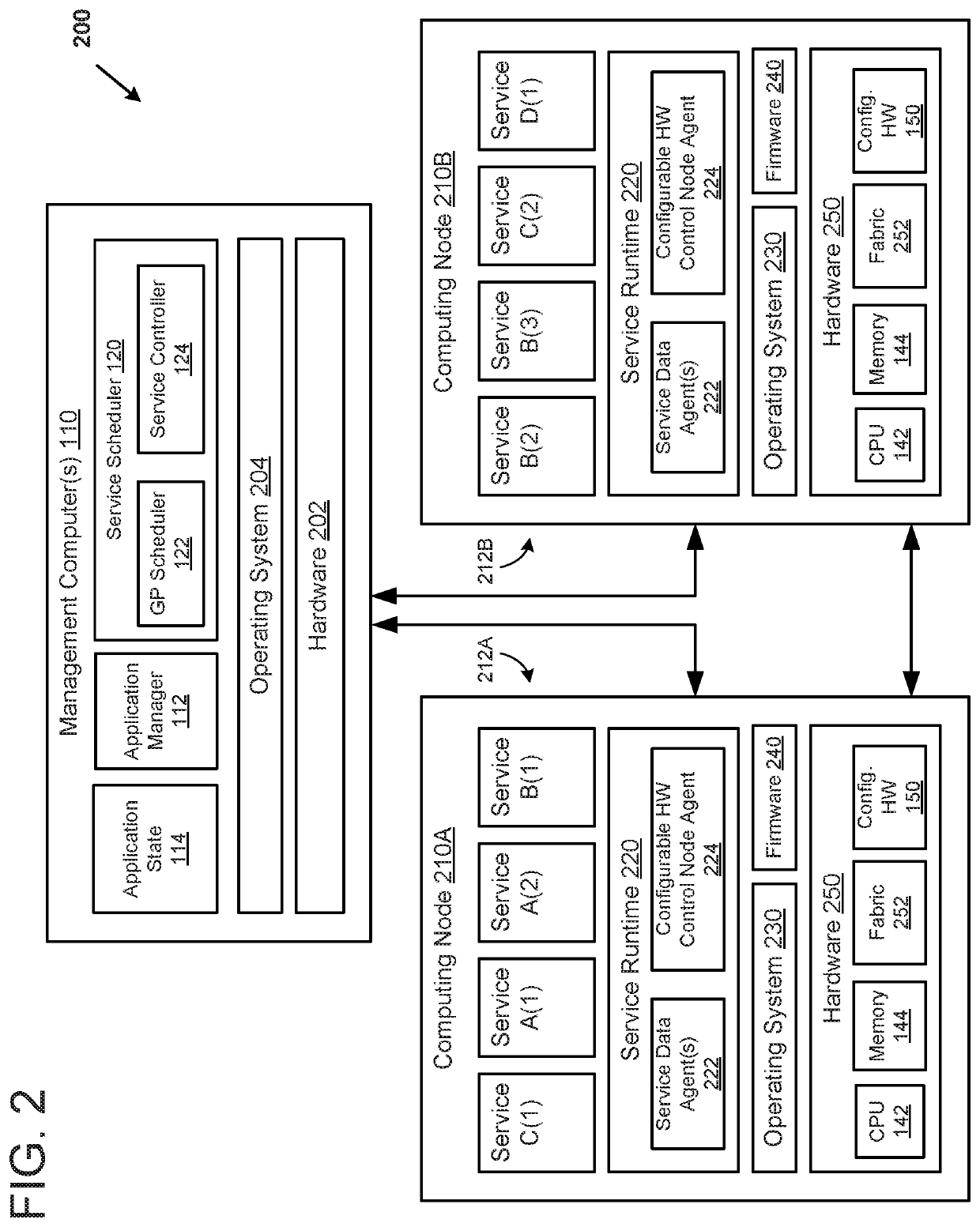

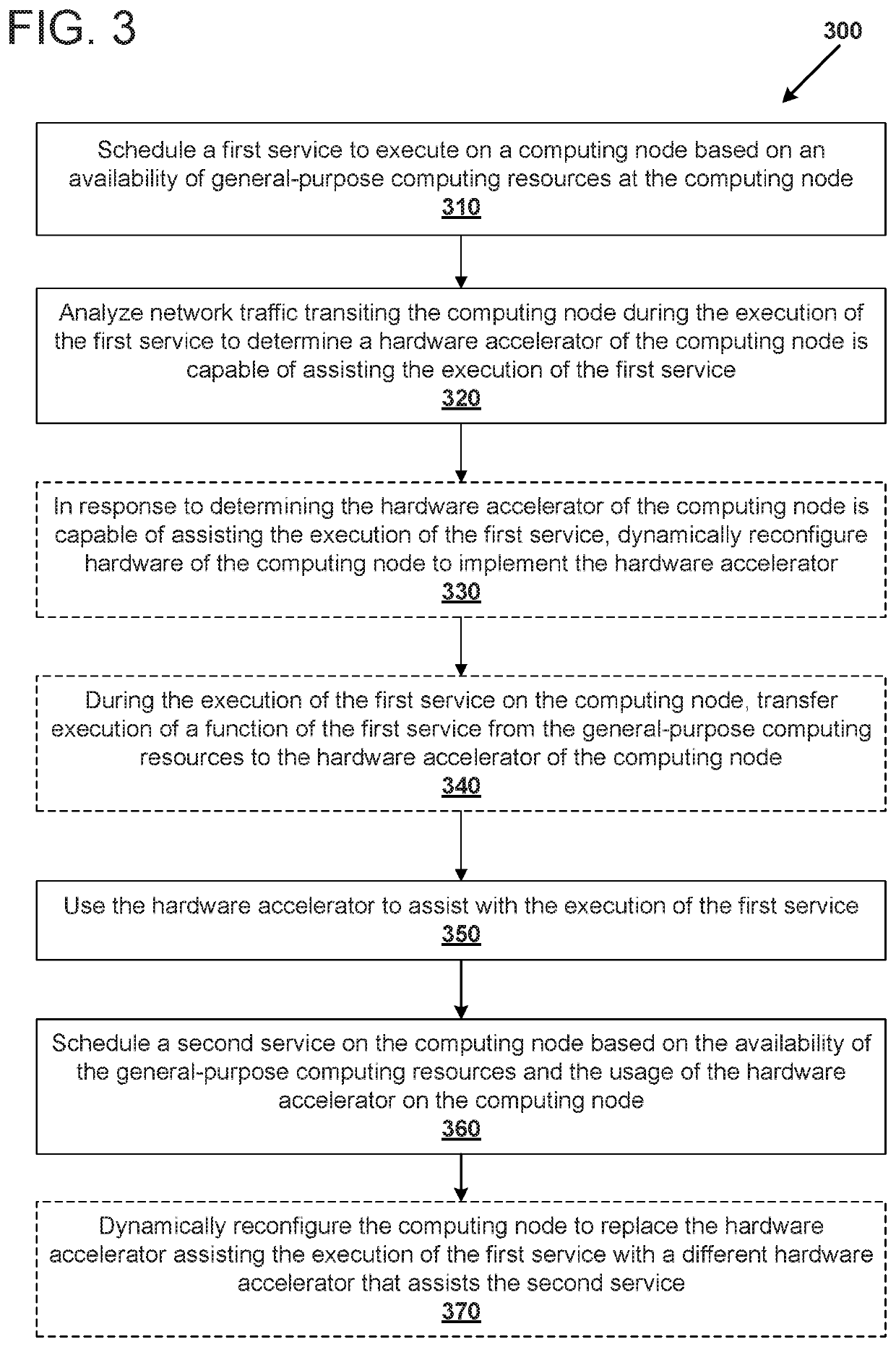

Scheduling services on a platform including configurable resources

ActiveUS20210152659A1Program initiation/switchingResource allocationInternet trafficOperating system

Owner:F5 NETWORKS INC

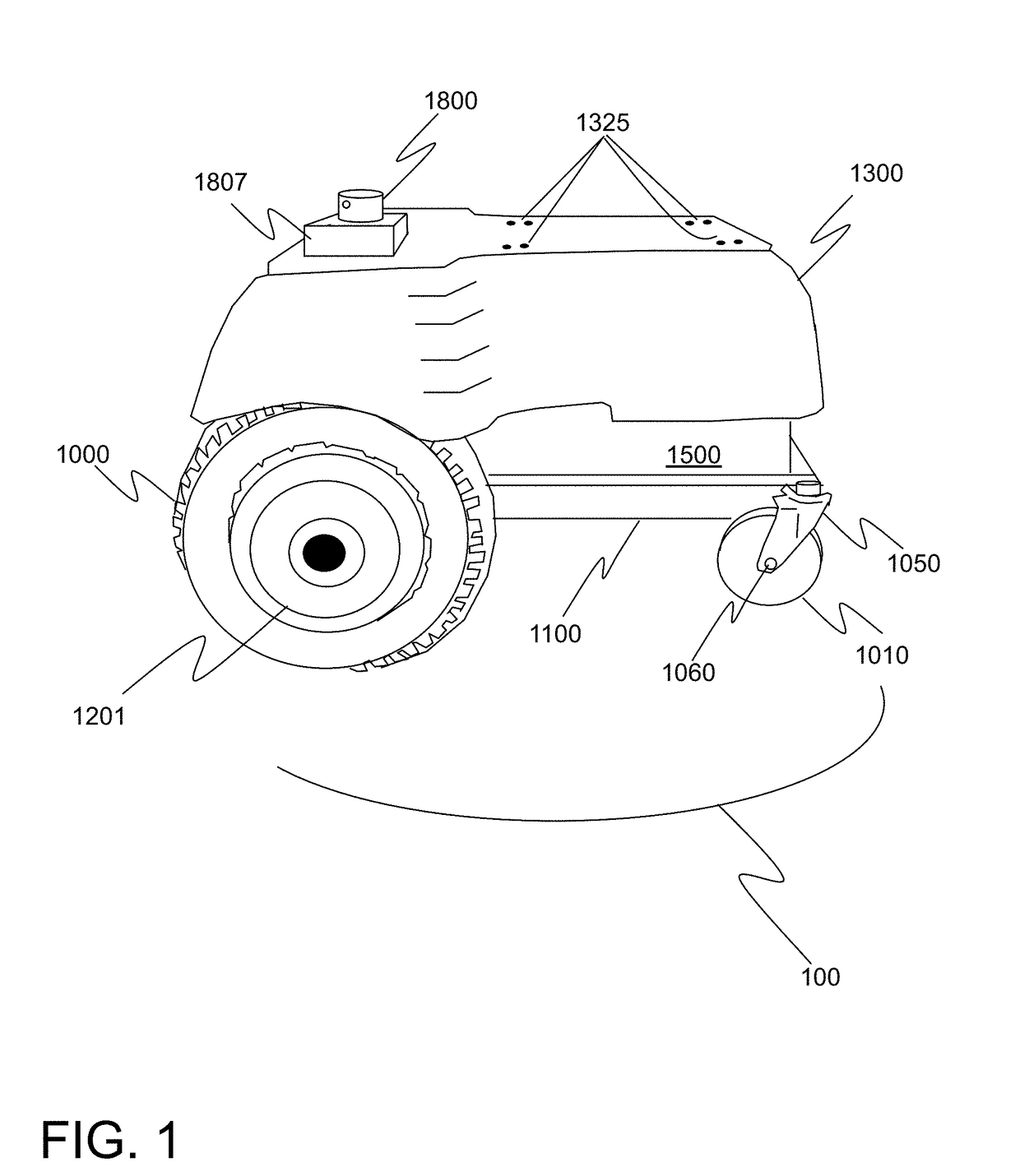

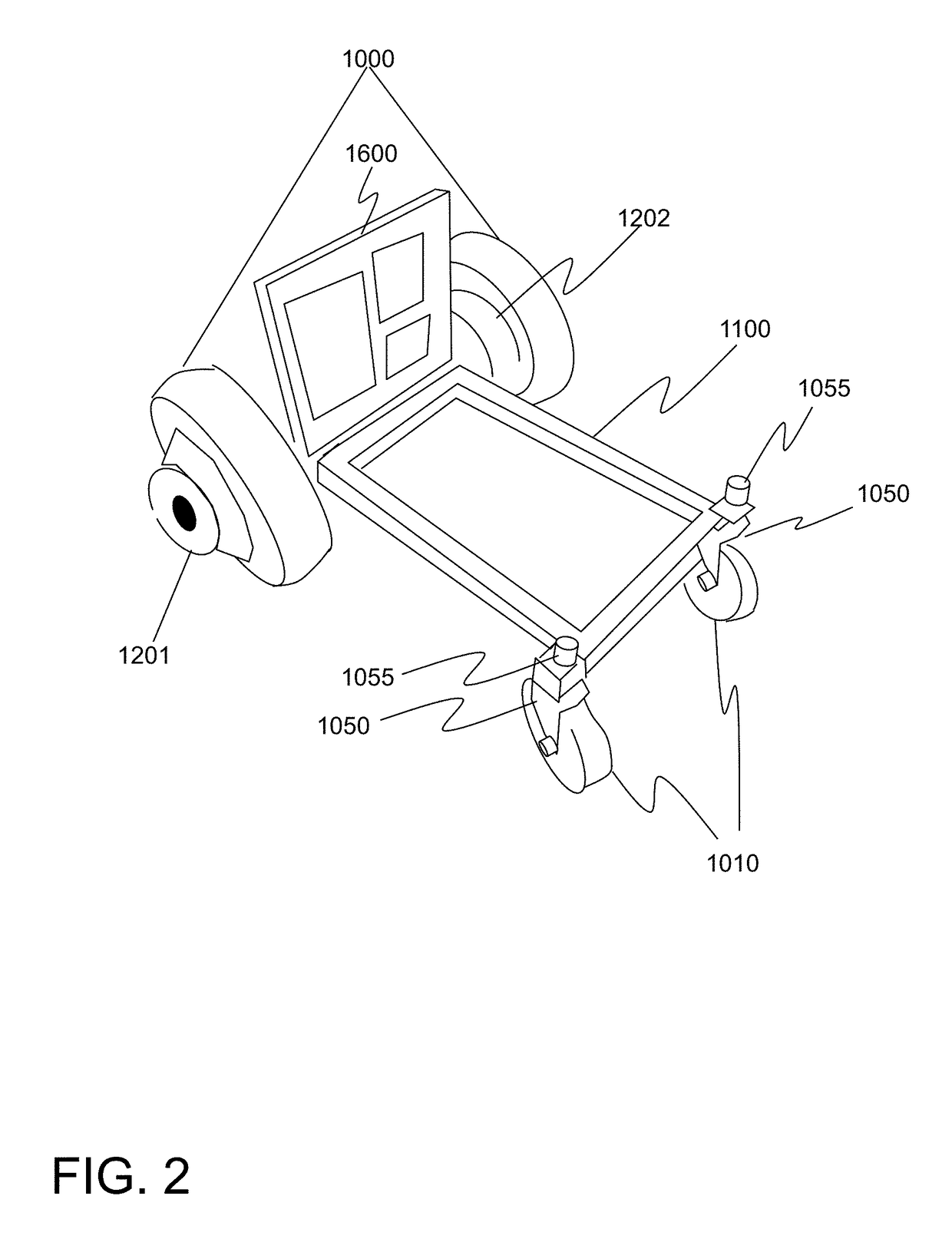

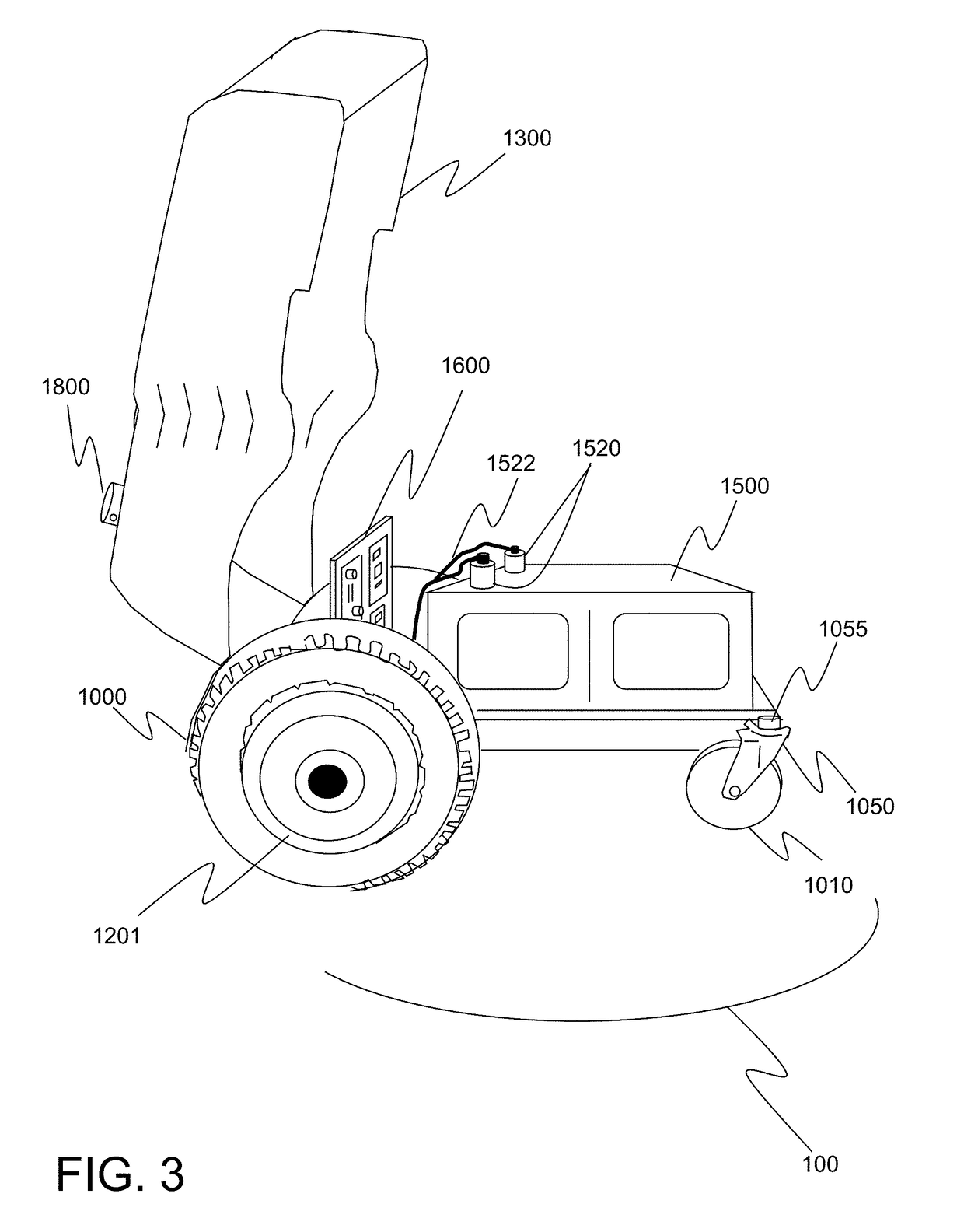

Versatile autonomous mobile platform with 3-d imaging system

ActiveUS20190079532A1Programme-controlled manipulatorElectromagnetic wave reradiationComputer hardwareStructure of Management Information

An autonomous mobile system comprising: a means of achieving mobility, a means of navigating, a means of providing autonomous power, and a means of providing general purpose computing. In some embodiments, the system comprises a base unit capable of sensing its environment and computing navigation instructions to direct the system to move to particular locations and execute functions as directed by a set of programmed instructions. In some embodiments, two or more time-of-flight (TOF) imaging systems are attached to measure distance to objects in the environment, which may in turn be used by the means of navigating. In some embodiments, a coupling exists on the base unit to attach additional structures and mechanisms. These structures may comprise a means for carrying packages or other items, robotic manipulators that can grab and move objects, interactive audio and video displays for telepresence applications, a means for serving food and drink, etc.

Owner:UBIQUITY ROBOTICS INC

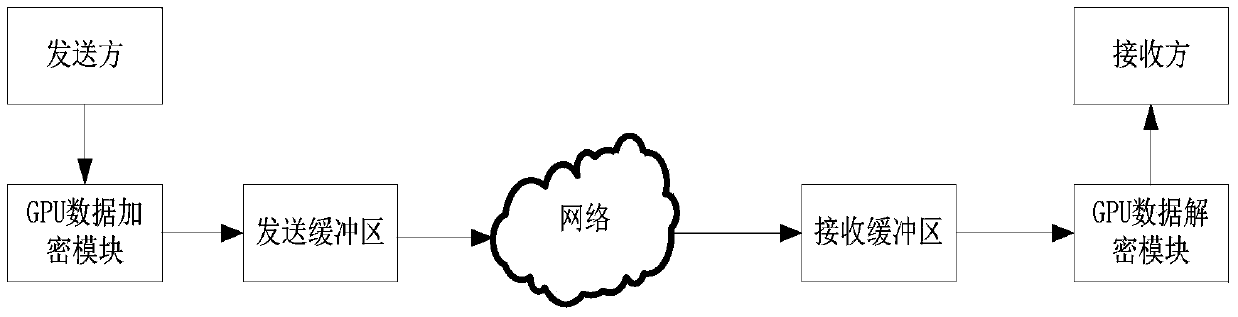

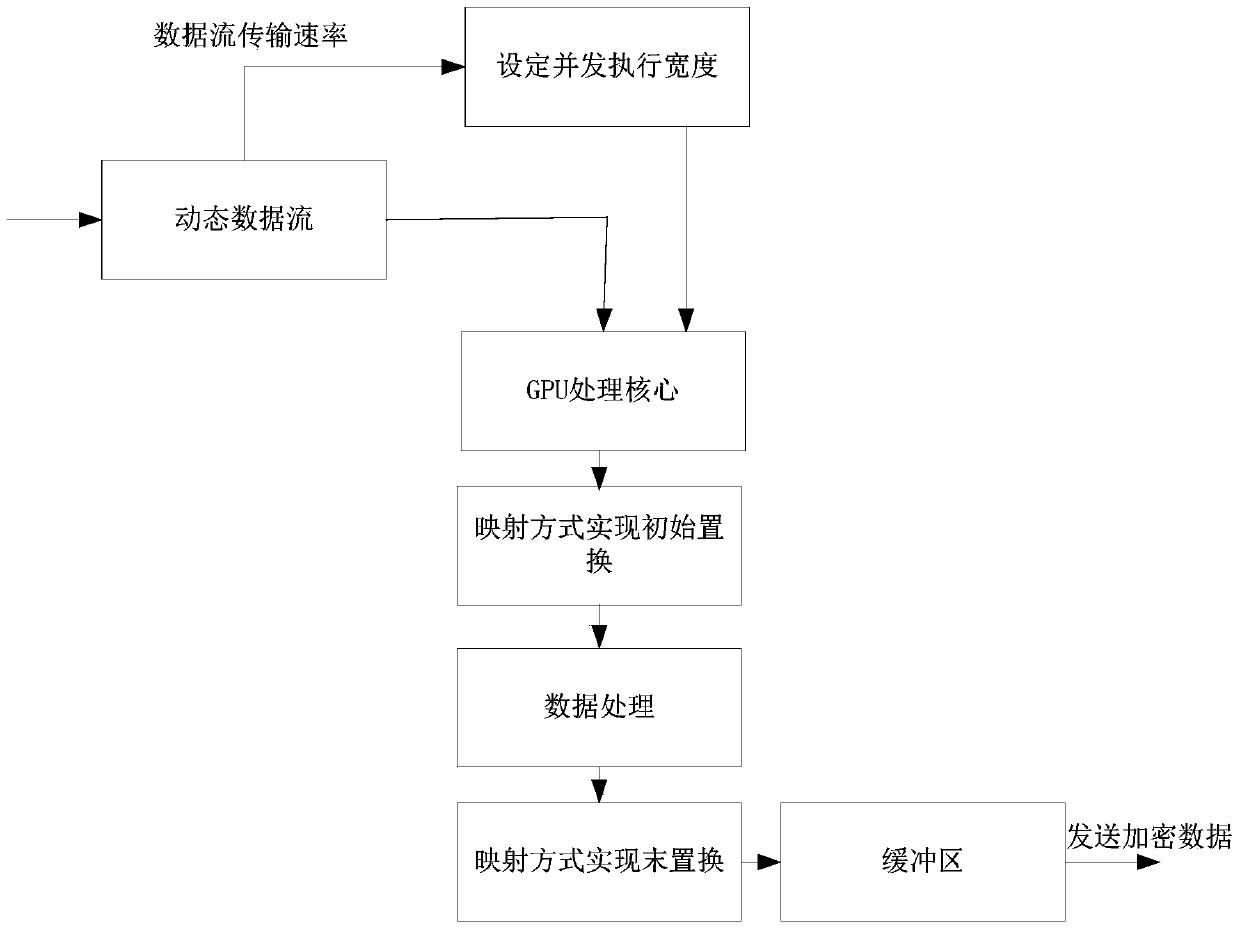

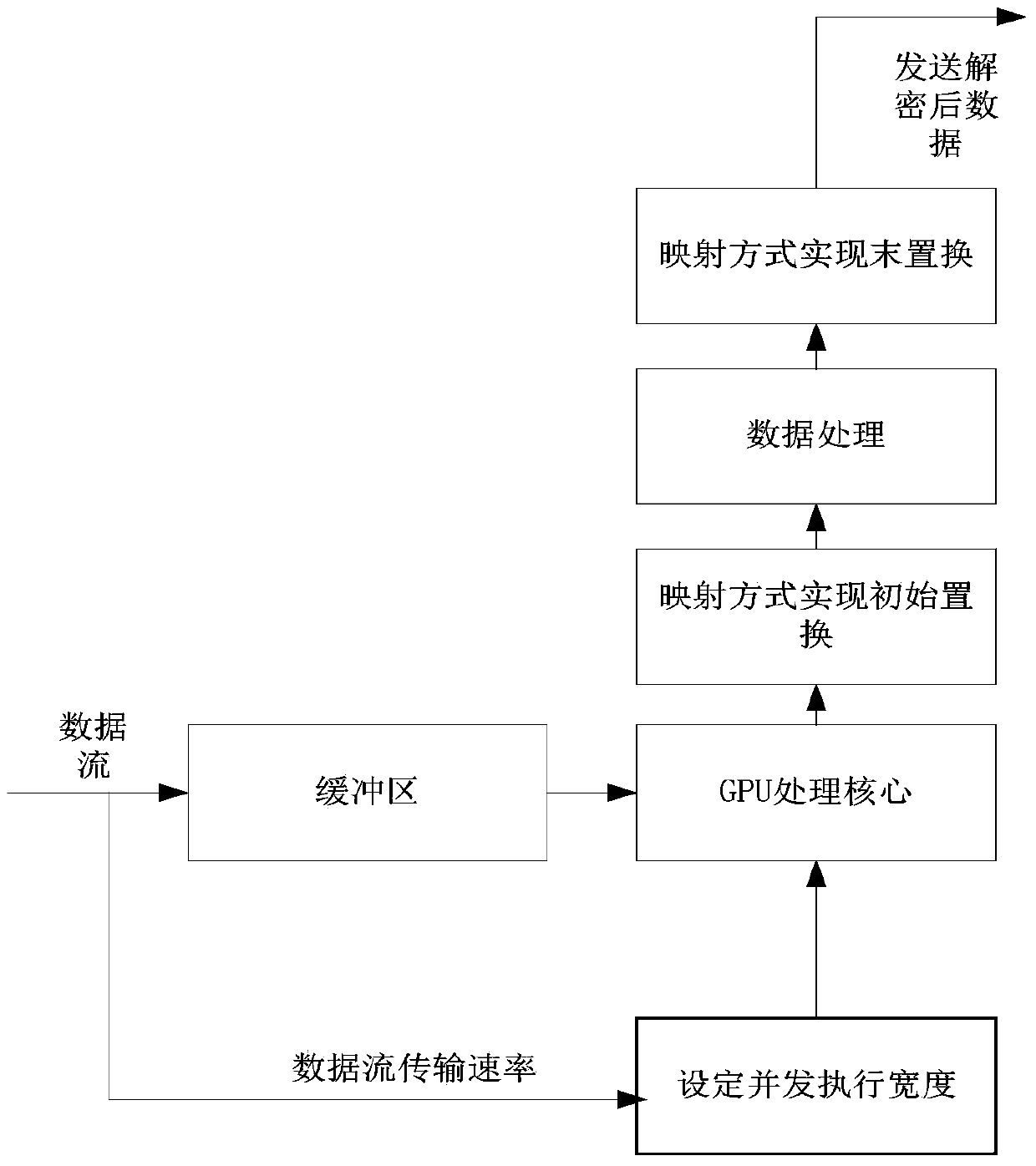

Parallel encryption and decryption method for dynamic data under large data environment

ActiveCN103632104AReduce computing loadNormal transmissionDigital data protectionComputer hardwareGraphics

The invention discloses a parallel encryption and decryption method for dynamic data under a large data environment. Under the large data environment, according to the method, parallel encryption and decryption operations on a large amount of dynamic data stream generated on a network are achieved. According to the method, a general computer GPU is used for completing the data encryption and decryption processes in a parallel mode. According to the dynamic data transmission rate, the data processing concurrent width is adjusted self-adaptively, and on the basis that information safety is guaranteed, open operation of encryption and decryption is realized.

Owner:云端智造(广州)物联网科技有限公司 +2

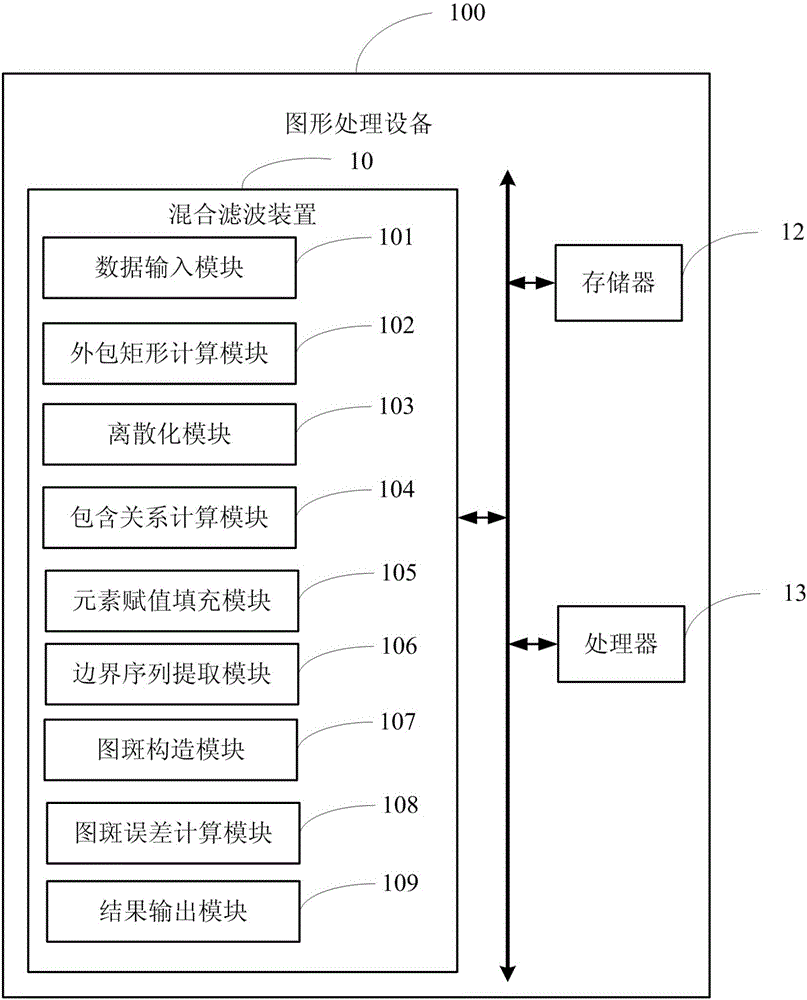

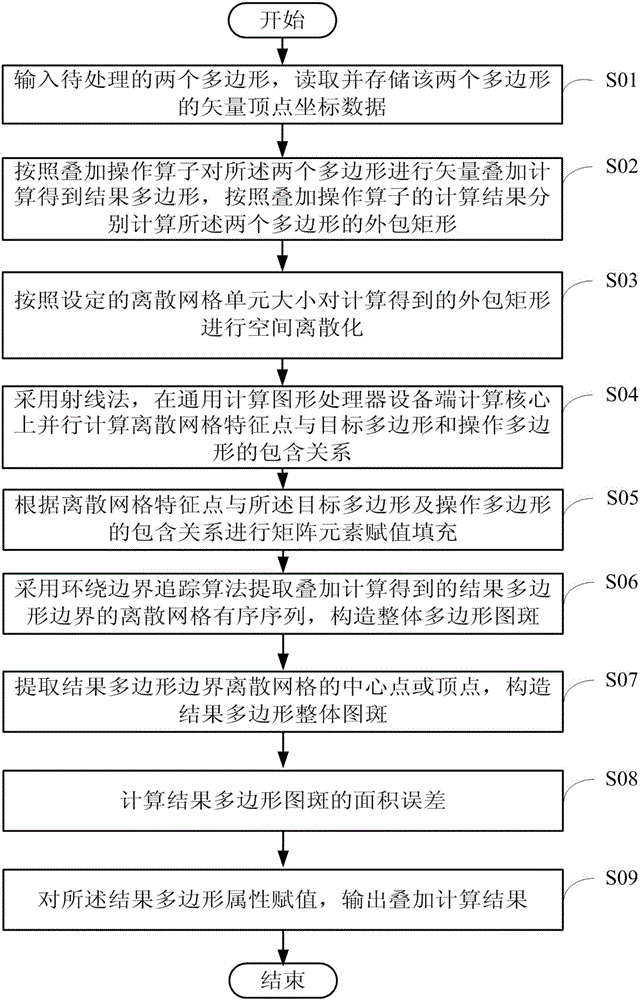

Graph processing method and device based on rasterized superposition analysis

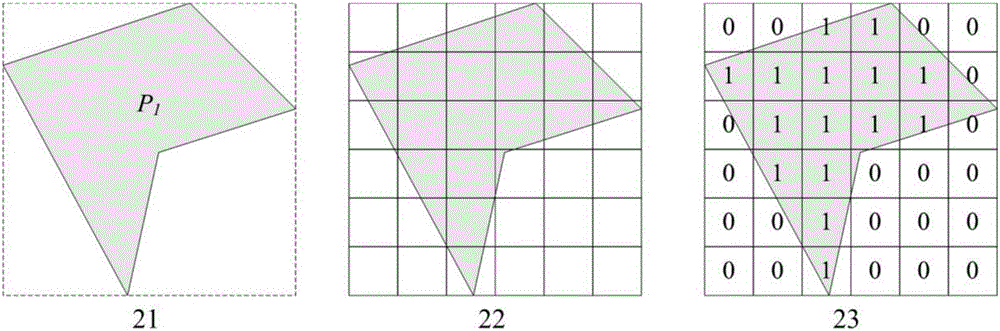

InactiveCN105956994AIncrease profitLow coupling propertiesImage analysisProcessor architectures/configurationGraphicsInclusion relation

The embodiment of the invention provides a graph processing method and a device based on rasterized superposition analysis in order to solve a problem in the prior art that the computation efficiency rapidly decreases along with increase in the number of polygon vertices. The graph processing method comprises the steps of computing bounding rectangles of superposition computation results of two vector polygons participating in superposition computation, carrying out spatial discretization on the bounding rectangles according to the set discrete grid cell size, parallelly computing an inclusion relation between discrete grid feather points and the two polygons on a computing kernel of a general purpose computation graph processor equipment terminal by adopting a ray method, carrying out matrix element assignment filling according to the inclusion relation between the discrete grid feature points and the two polygons, extracting a discrete grid ordered sequence of result polygon boundaries by adopting a surround boundary tracing algorithm, extracting a center point or a vertex of a discrete grid of the result polygon boundaries so as to construct a result polygon overall pattern spot, computing an area error of the result polygon pattern spot, and carrying out attribute assignment on the result polygon so as to output a superposition computation result.

Owner:SHANDONG UNIV OF TECH

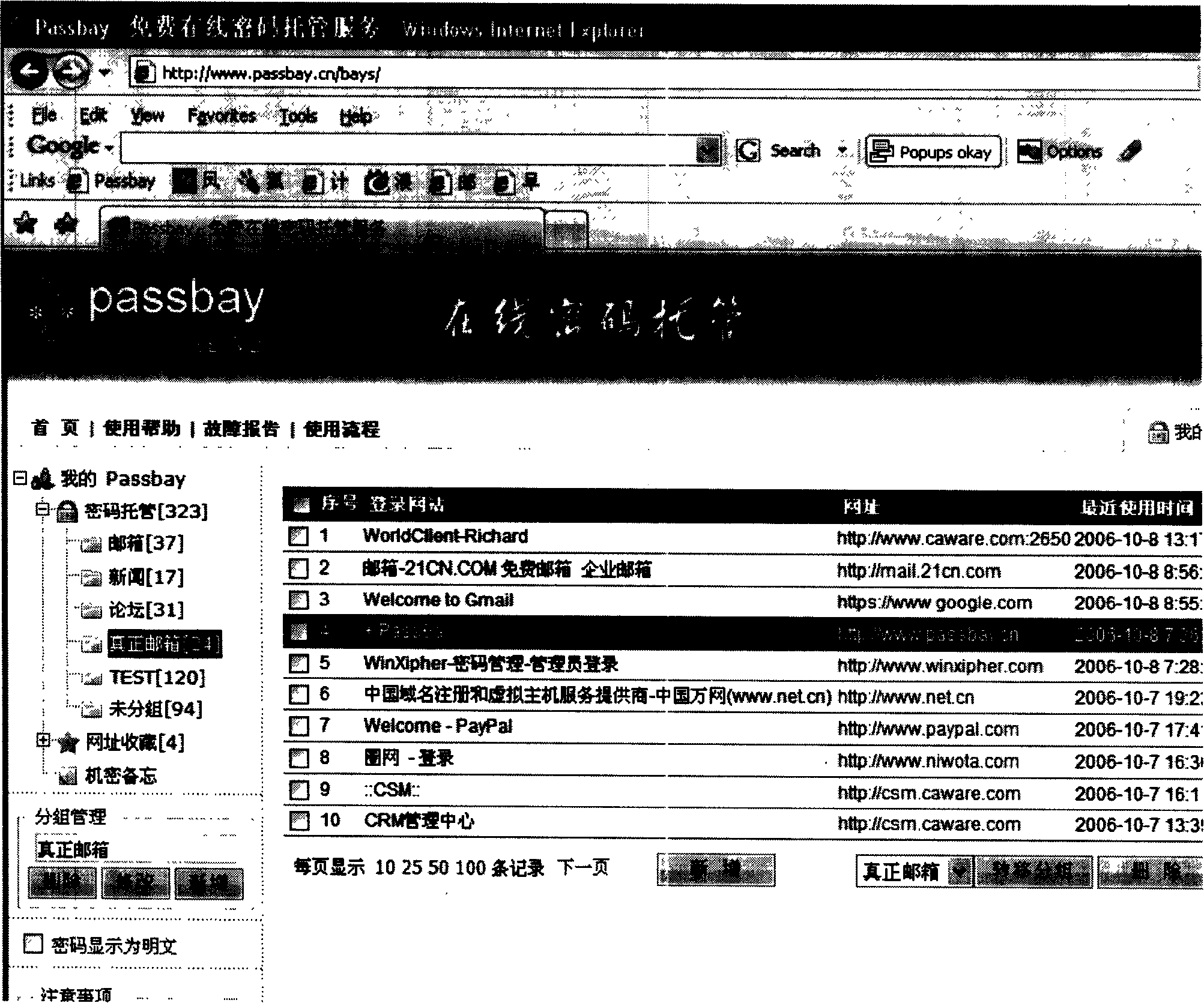

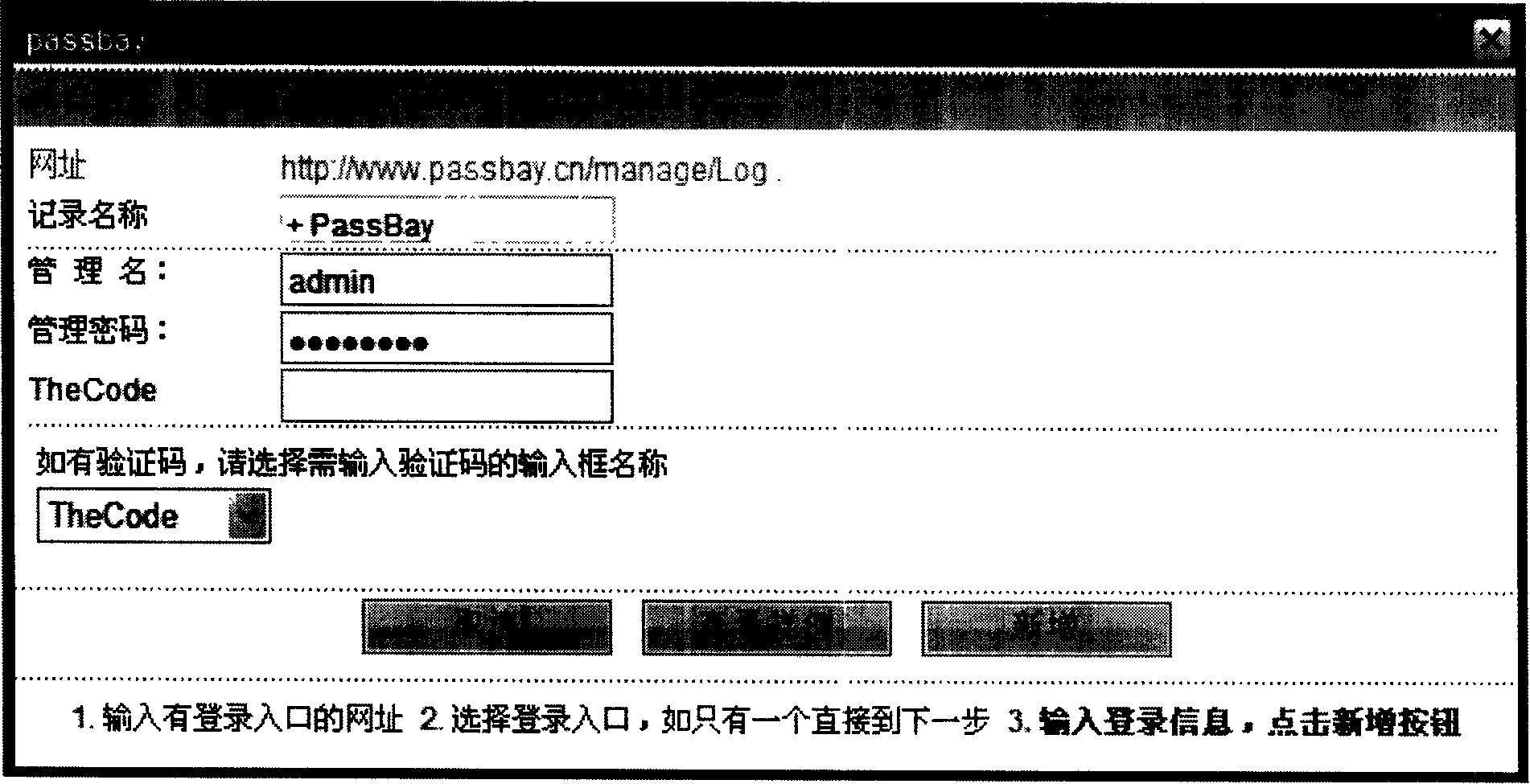

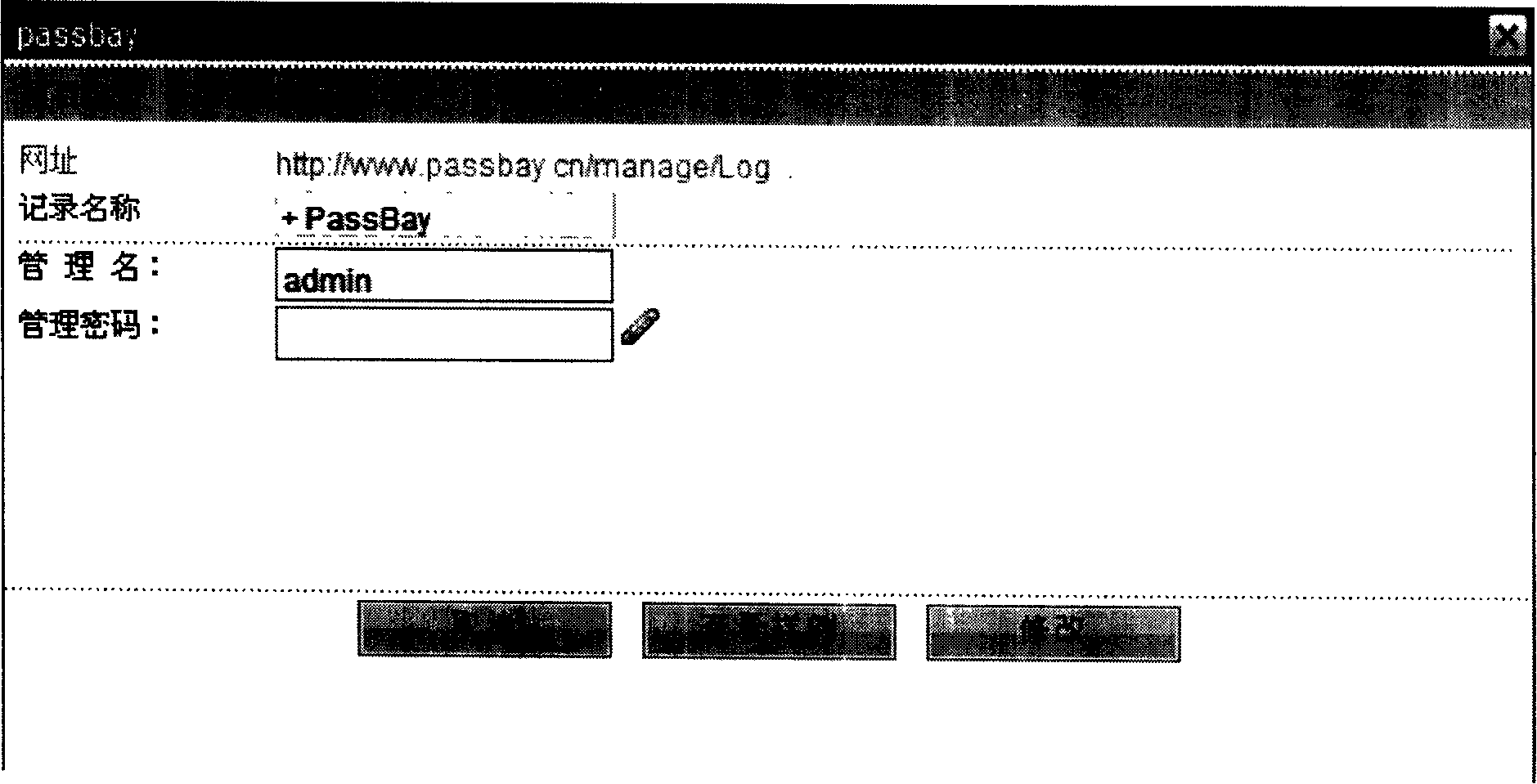

Method and system for realizing agent certification based on identity authentication mode including random information

InactiveCN101170408AReduce manual input operationsImprove securityUser identity/authority verificationData switching by path configurationAuthentication protocolPassword

The invention relates to a method and a system to realize agent authentication aiming to an identity authentication mode including random information. The identity authentication mode including the random information is to authenticate user's identity information including a changeless part such as the account, the password and other changeable information during each authentication process. The system comprises a program operated in general computing devices. The agent authentication steps comprise that: a user starts an authentication flow, and the program picks up the random information relevant to the authentication and gives prompt to the user; the user inputs the assisted authentication information in accordance with the program prompt; the program submits the pre-stored authentication information and the assisted information of the authentication process to a corresponding authentication scene, and the authentication is then completed. The method and the system can significantly reduce the manual input operation in the authentication process and enhance the security of the authentication process.

Owner:许先才

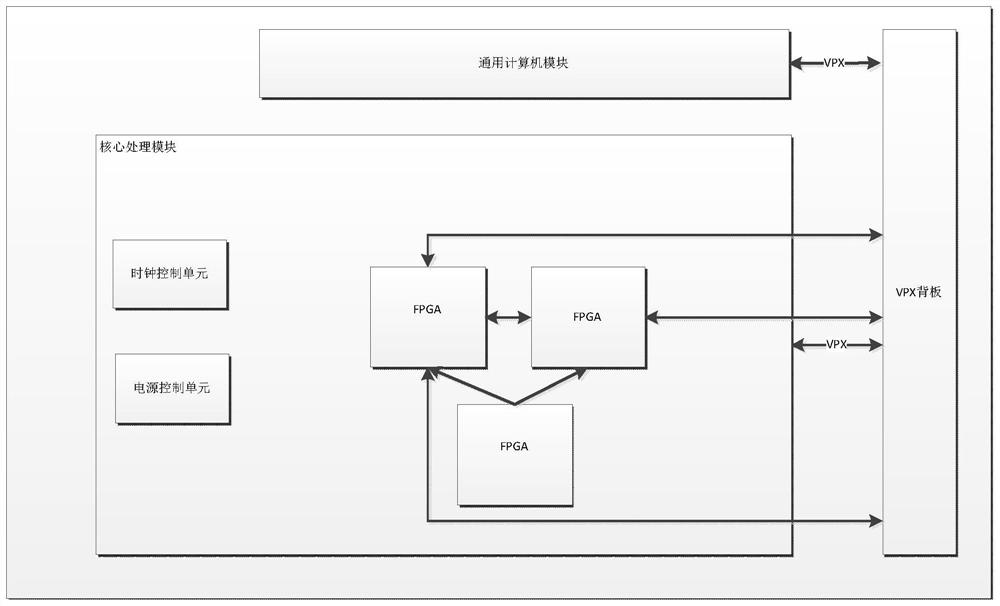

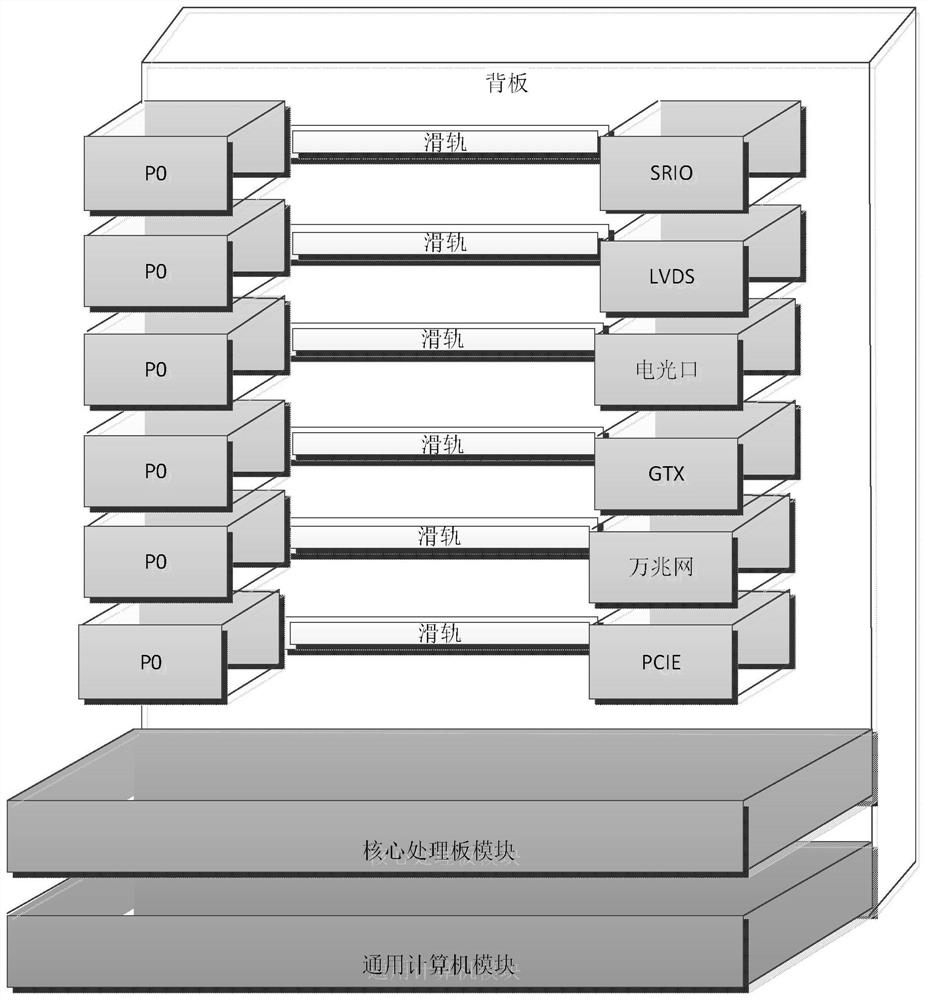

Universal testing device for VPX high-speed signal board

PendingCN112285530AEasy to useEasy to implementProgramme controlComputer controlData streamGeneral purpose computer

The invention discloses a universal testing device for a VPX high-speed signal board, and relates to the field of high-speed signal acquisition of measurement and control communication and the like. According to the technical scheme, a universal computing module is adopted as a central node of star switching, and a PCIe of an X4 of a connector is connected with a core processing module to completea control function, control and state detection of the core processing module and control and monitoring of an external test instrument are realized; the core processing module interacts with the universal computer module, sends the received information to the signal processing board for processing, responding to a command of reusing the control system through single board software is made, and different function options are loaded; the core processing module takes three FPGAs connected in parallel as a core, completes analysis and distribution of control commands and transmission of signal data streams through the FPGAs, and is connected with SRIO signals of the VPX backboard to form an SRIO data transmission network for data interaction, and the FPGAs send data to each other irregularlyin a point-to-point manner.

Owner:10TH RES INST OF CETC

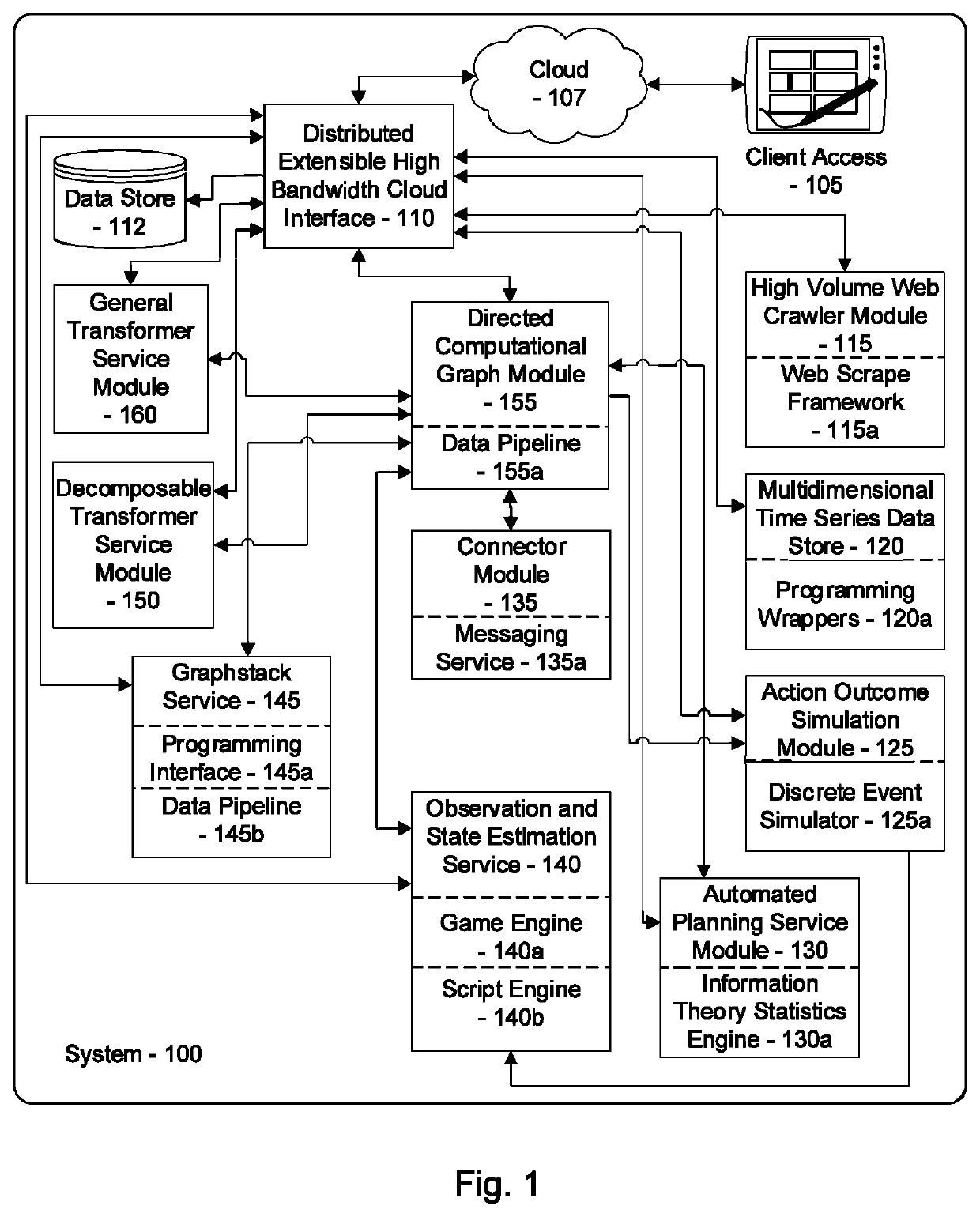

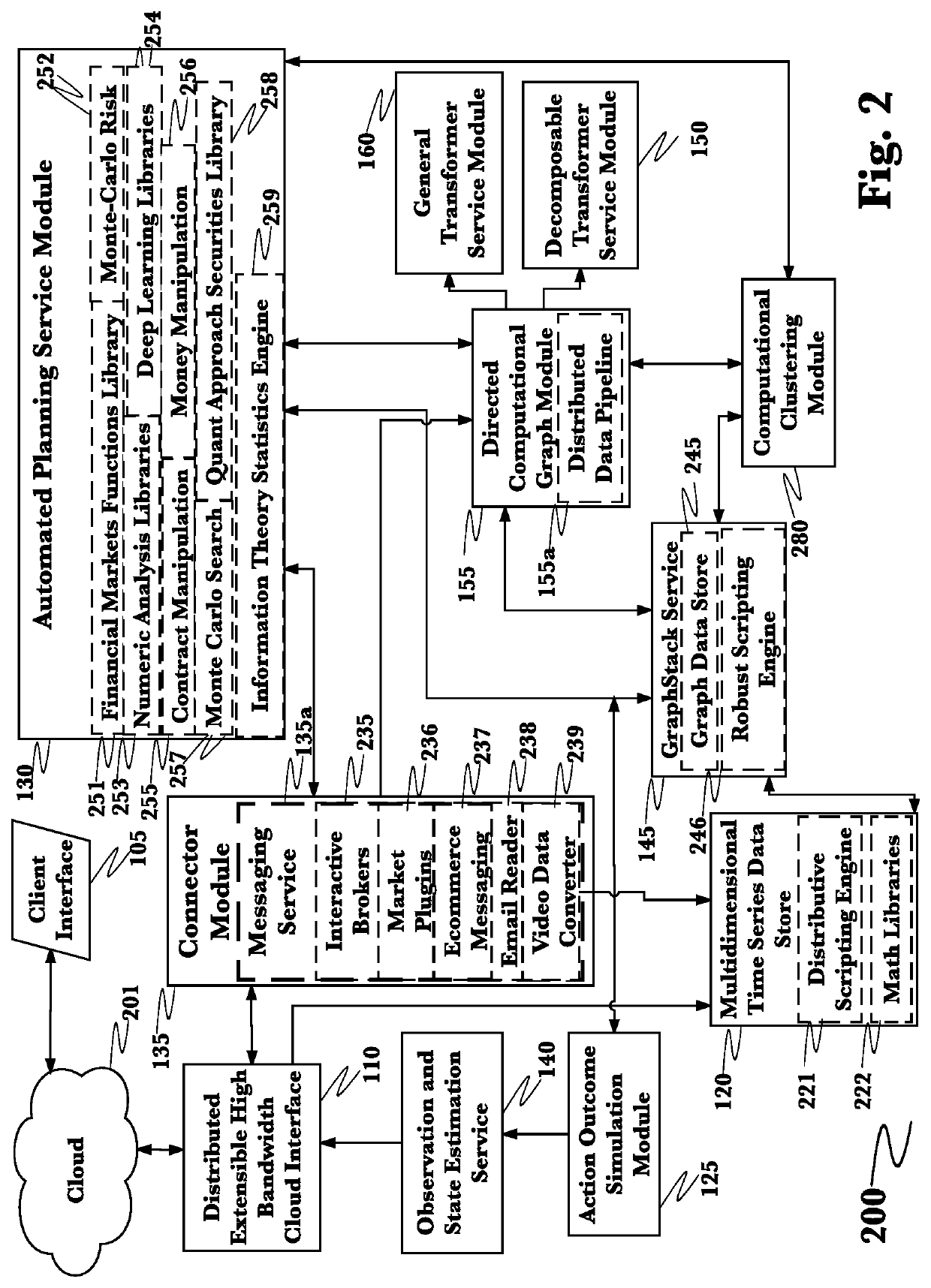

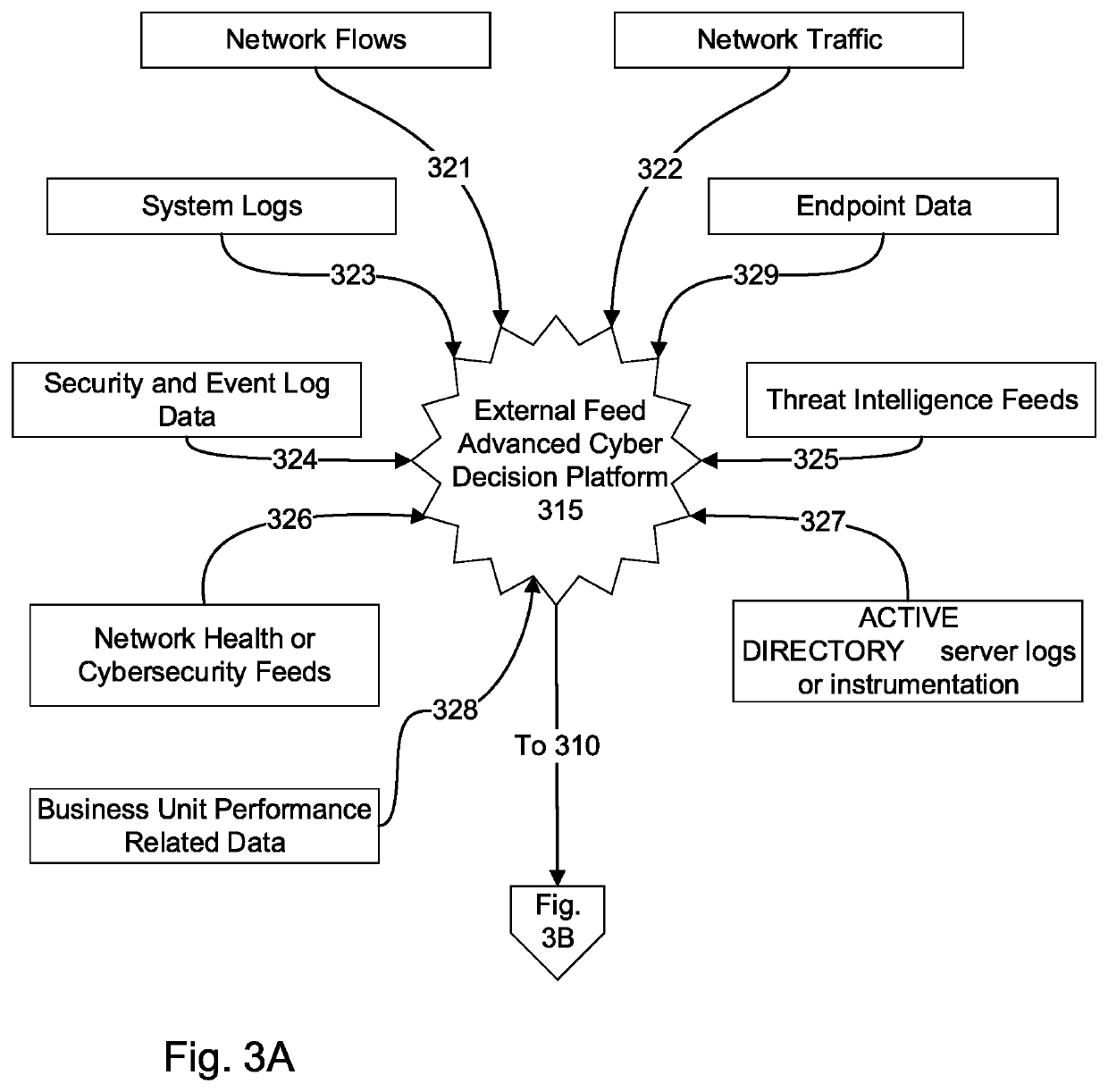

Universal computing asset registry

A system and method for universalization and contextualization of computing assets that utilizes structure, organization, and ontologically-related metadata to unify computing assets into a common data model combined with provenance-related metadata to contextualize the assets for suitability in a given situation. The system and method include an asset registry that contains provenance information and ontological information about available computing assets, a provenance manager which tracks the provenance of each asset for data validation and contextual analysis purposes, an ontology manager that uses ontological relationships among assets to determine other domains in which an asset may be useful, and an interoperability manager which combines the provenance and ontology outputs to suggest computing assets that may be useful in a given context.

Owner:QOMPLX LLC

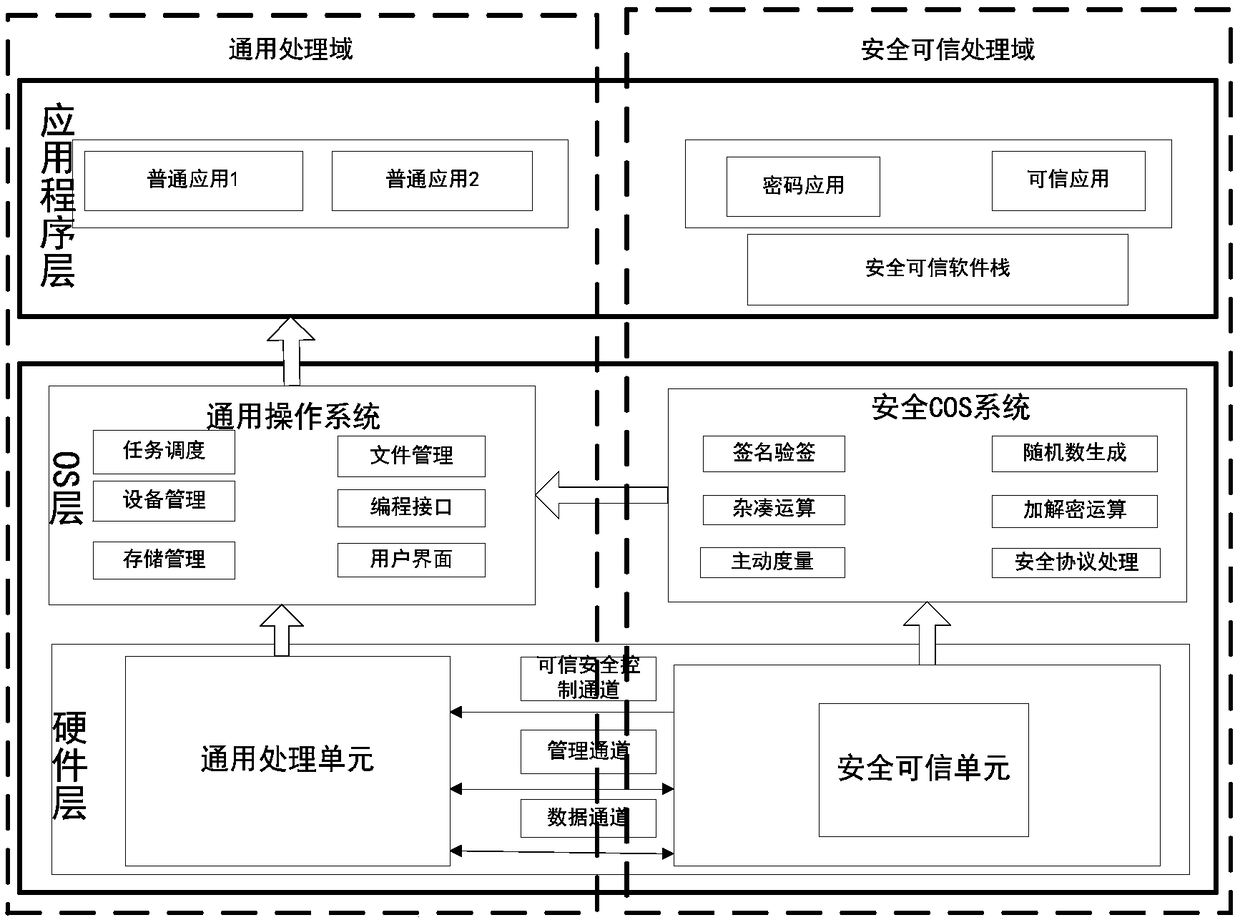

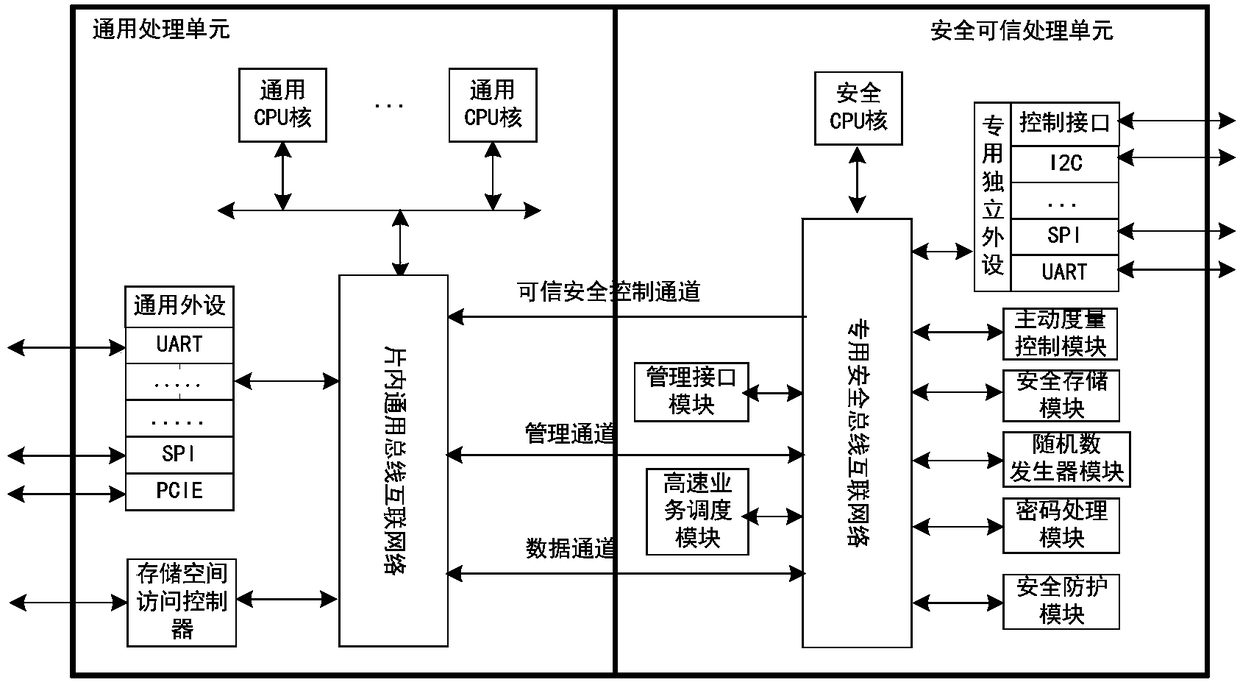

General purpose computation, trusted computation and cryptographic computation integrated safety processor

ActiveCN108491727AGuaranteed normal transmissionImprove securityDigital data protectionTrusted ComputingSafety control

The invention discloses a general purpose computation, trusted computation and cryptographic computation integrated safety processor, which comprises a general processing unit and a safety trusted processing unit. The general processing unit and a safety trusted processing unit realize data interaction through a data channel, a management channel and a trusted safety control channel. Compared withthe prior art, the safety processor has advantages that by chip level deep fusion of the general processing unit and the safety trusted processing unit, on-chip efficient transmission of data betweenthe general processing unit and the safety trusted processing unit is realized, chip level cryptographic services are provided, chip level trusted services according with trusted computation relatedstandards are provided, safety is effectively improved, and the safety processor is capable of withstanding physical attacks, reverse engineering attacks and cloning attacks.

Owner:成都三零嘉微电子有限公司

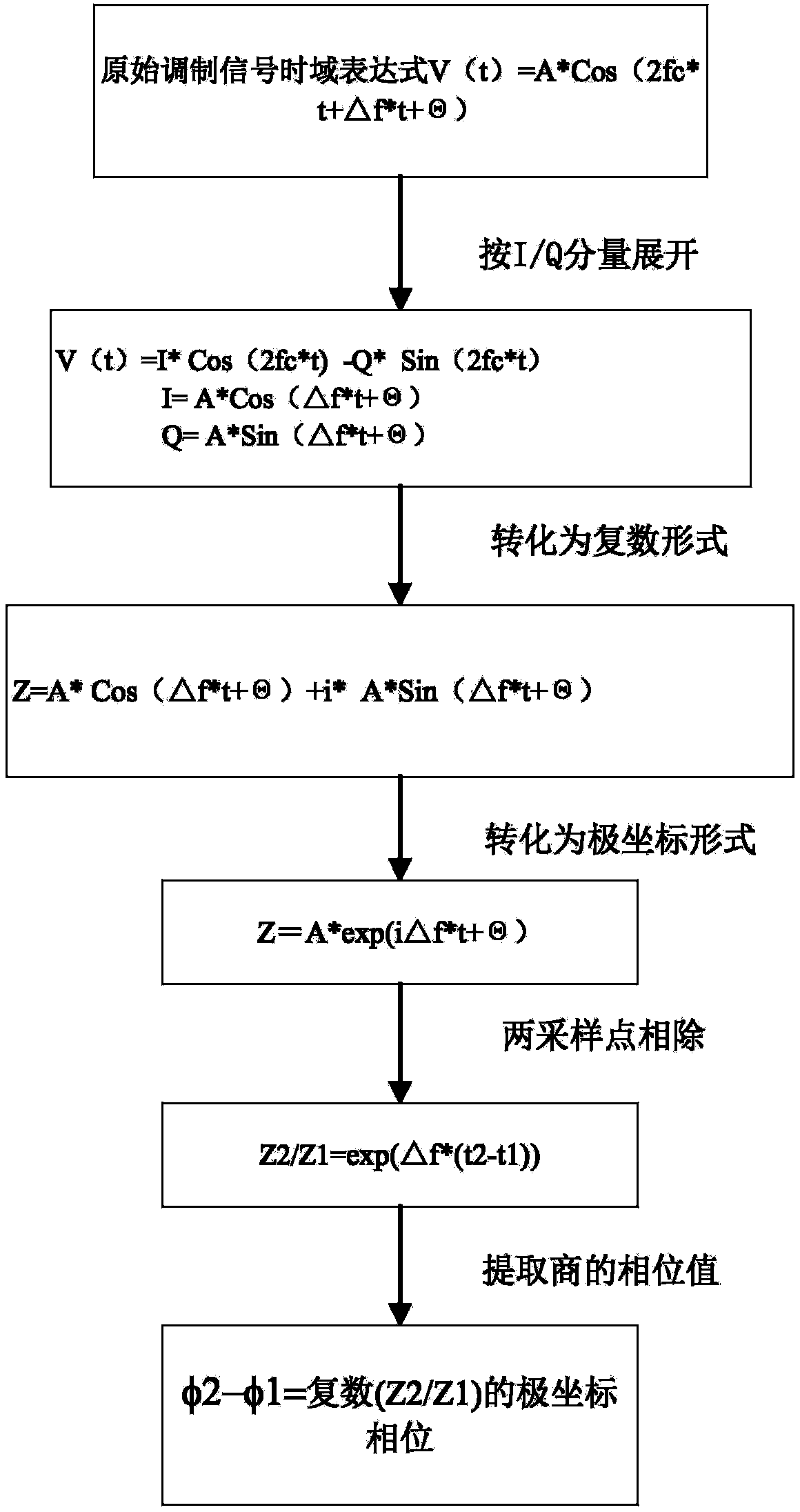

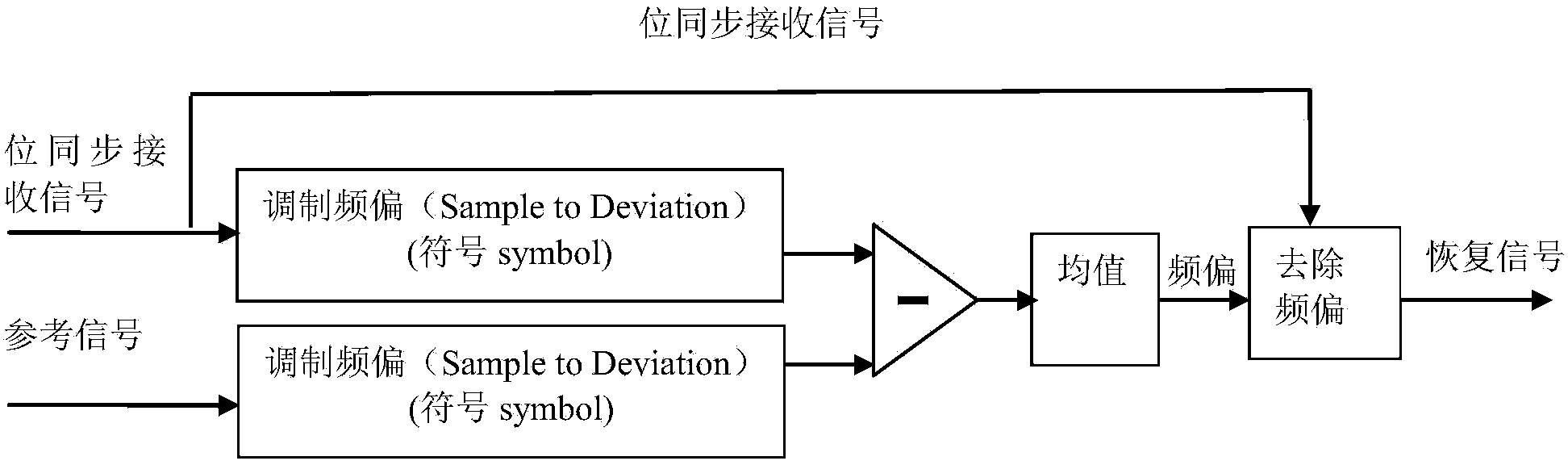

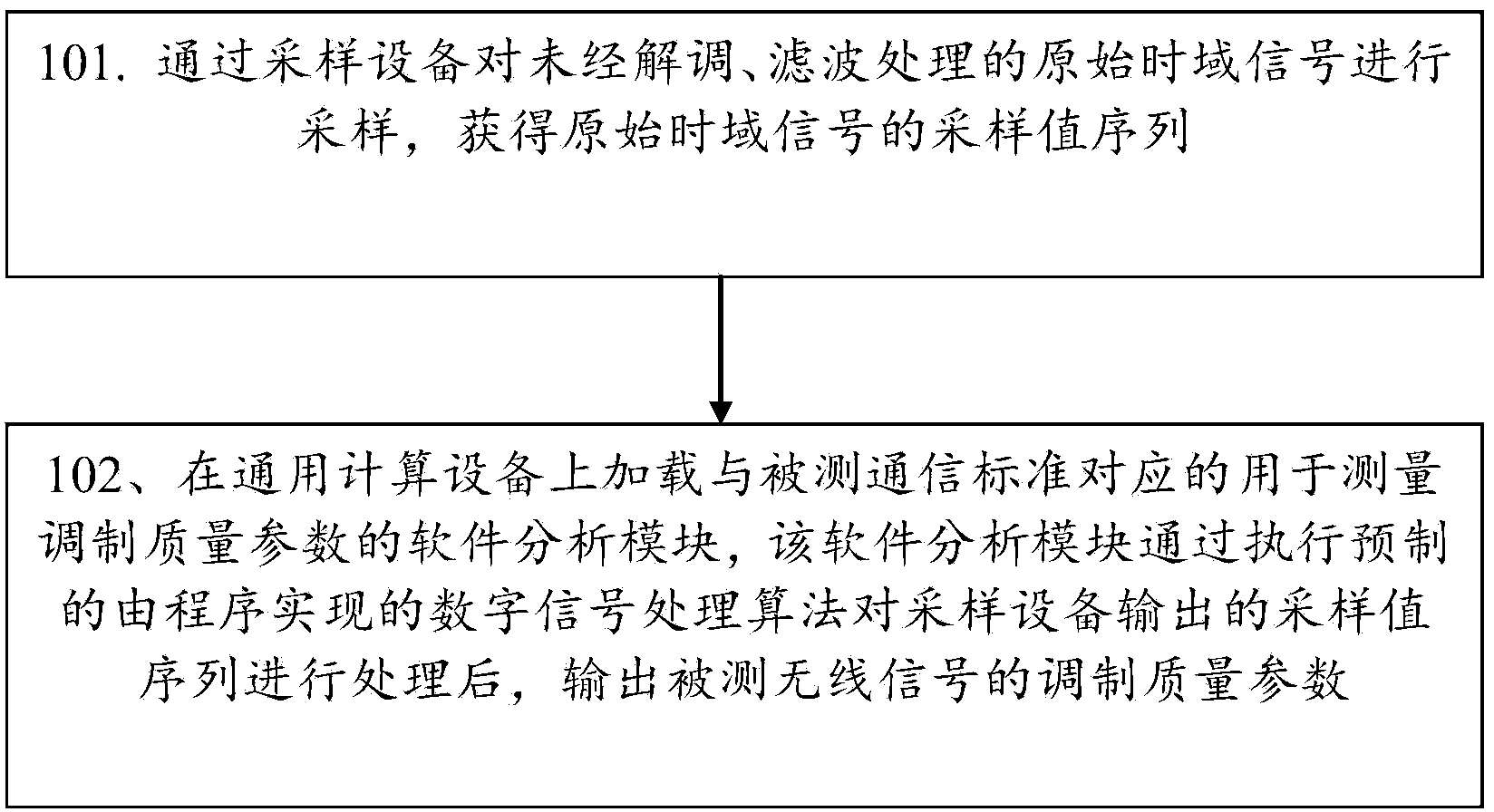

Method for measuring modulation quality parameters based on software radio technology and system

InactiveCN103414523AImprove test accuracyFunction increaseError preventionTransmission monitoringTime domainMeasurement cost

The invention discloses a method for measuring modulation quality parameters based on software radio technology and a system. According to the invention, an original time-domain signal with no demodulation and filtering is acquired through a sampling device, and a sampling value sequence is inputted into a general purpose computation device. In the general purpose computation device, a software analysis module, which corresponds to the communication standard and is used for measuring the modulation quality parameters, is used for executing a digital signal processing algorithm premade by a program to process the sampling value sequence that the sampling device outputs so that modulation quality parameter results of the measured signal are obtained. Based on the same test platform, the method for measuring the modulation quality parameters based on software radio technology and the system are capable of achieving measurement of modulation quality parameters of various different communication standards, can extend the functions of existing equipment, reduce measurement costs and improve measurement capability, and help to improve the measuring accuracy of the modulation quality parameters.

Owner:NAT INST OF METROLOGY CHINA

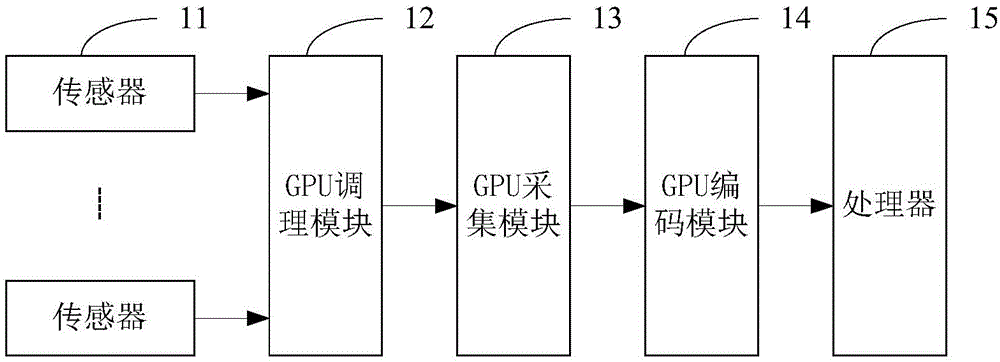

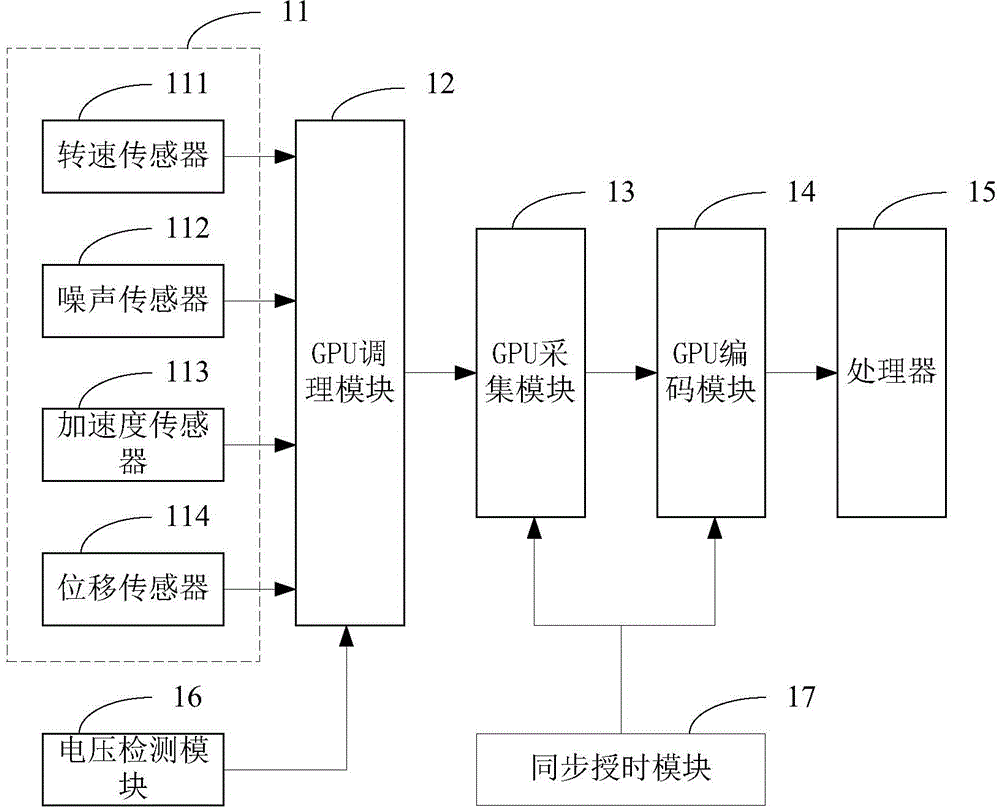

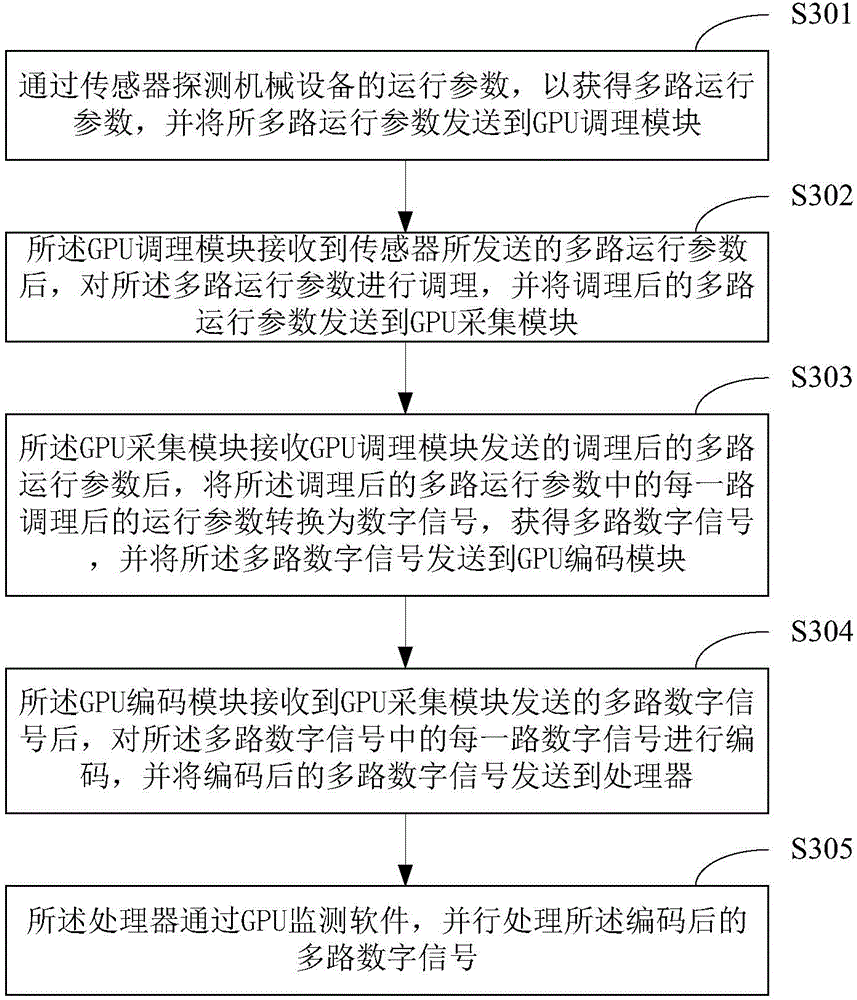

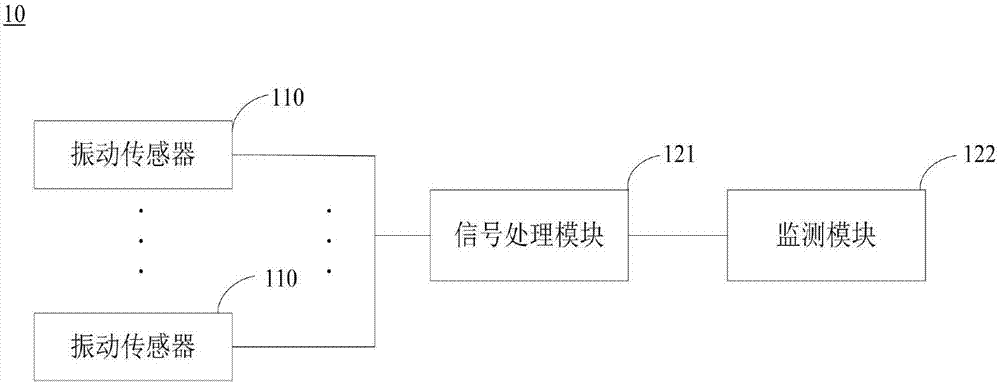

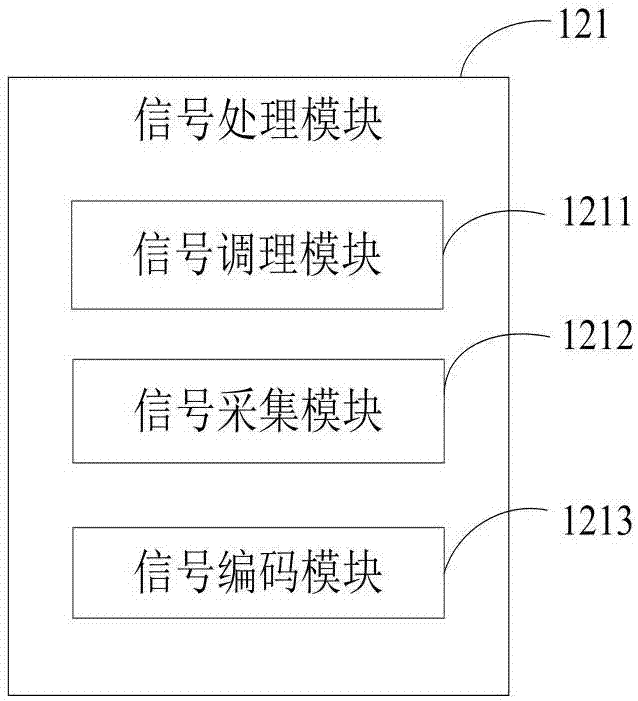

Mechanical failure monitoring system and method

InactiveCN104880330AMiniaturizationIncrease frequency bandwidthStructural/machines measurementMonitoring systemMiniaturization

The invention belongs to the field of monitoring technology, and provides a mechanical failure monitoring system and a mechanical failure monitoring method. The mechanical failure monitoring system comprises a plurality of sensors, a GPU conditioning module, a GPU acquisition module, a GPU encoding module and a processor, wherein the plurality of sensors are used for detecting mechanical equipment to obtain multi-path operating parameters; the GPU conditioning module is connected with the plurality of sensors, and is used for conditioning the multi-path operating parameters; the GPU acquisition module is connected with the GPU conditioning module, and is used for converting the conditioned multi-path operating parameters into digital signals to obtain multi-path digital signals; the GPU encoding module is connected with the GPU conditioning module, and is used for encoding the multi-path digital signals; and the processor is connected with the GPU encoding module, and is used for carrying out parallel processing on the encoded multi-path digital signals through GPU monitoring software. Therefore, the purpose of applying a general purpose computation graphics processing unit GPGPU to the mechanical failure monitoring system is realized, the synchronous analysis and processing of the multi-path operating parameters in the current window are realized, the miniaturization of the mechanical failure monitoring system is achieved, and the failure monitoring speed is increased.

Owner:SHENZHEN YATEKS OPTICAL ELECTRONICS TECH CO LTD

C/c++ language extensions for general-purpose graphics processing unit

A general-purpose programming environment allows users to program a GPU as a general-purpose computation engine using familiar C / C++ programming constructs. Users may use declaration specifiers to identify which portions of a program are to be compiled for a CPU or a GPU. Specifically, functions, objects and variables may be specified for GPU binary compilation using declaration specifiers. A compiler separates the GPU binary code and the CPU binary code in a source file using the declaration specifiers. The location of objects and variables in different memory locations in the system may be identified using the declaration specifiers. CTA threading information is also provided for the GPU to support parallel processing.

Owner:NVIDIA CORP

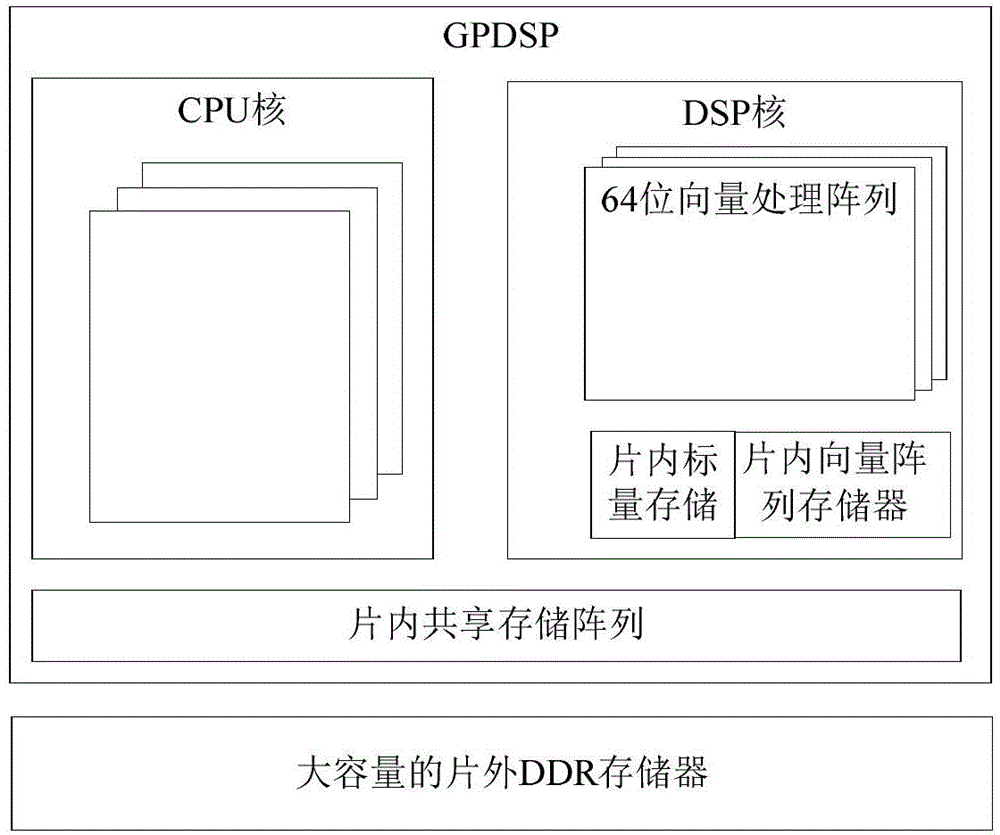

Method for vectorization computing of solution of large-scale trigonometric linear system of equations for GPDSP

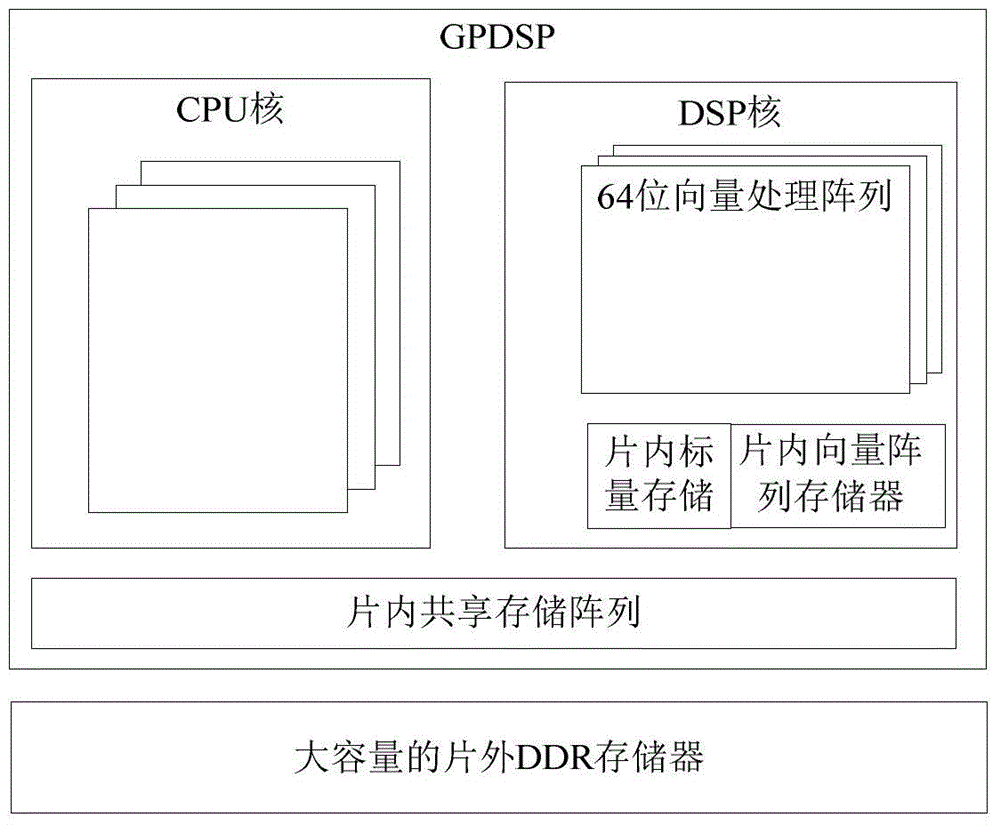

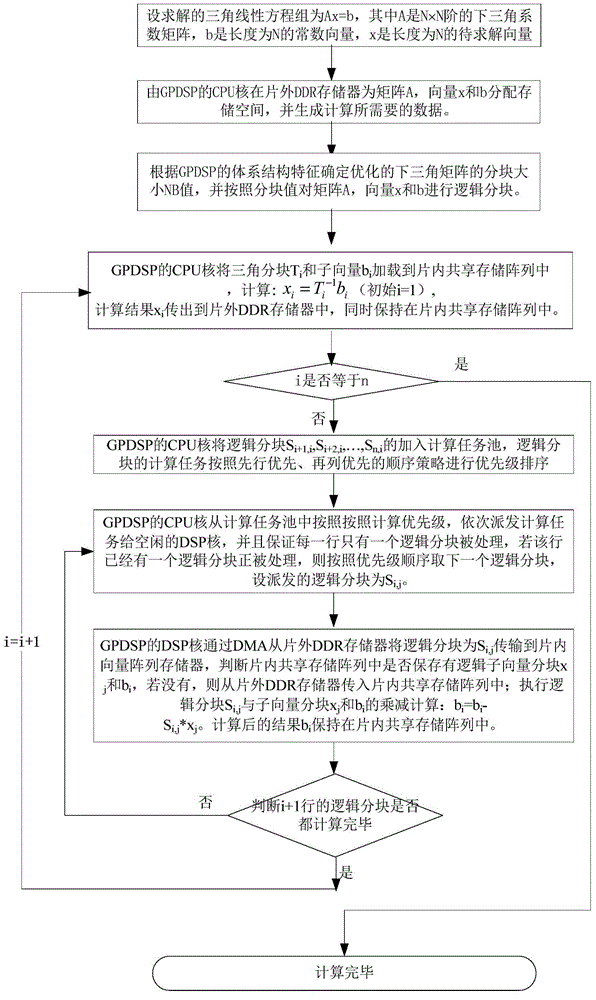

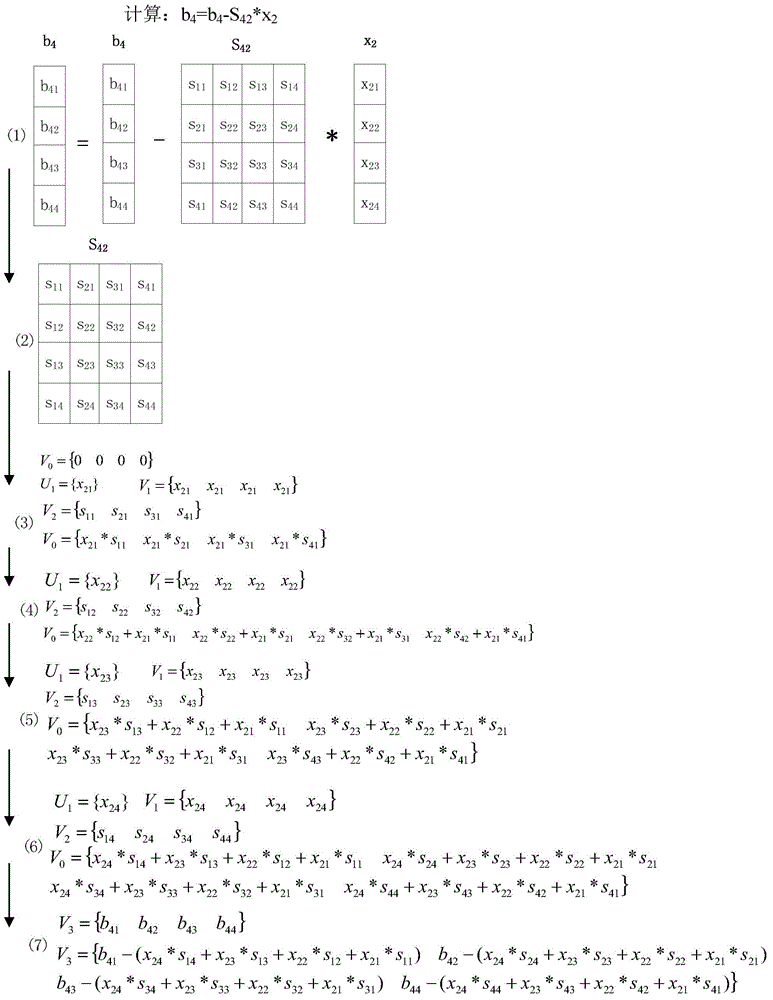

ActiveCN104615584ADynamic Load BalancingGet the most out of general-purpose computingMultiple digital computer combinationsComplex mathematical operationsHigh bandwidthOperational system

The invention discloses a method for vectorization computing of a solution of a large-scale trigonometric linear system of equations for a GPDSP. The method comprises the steps that the solution of the large-scale trigonometric linear system of equations is partitioned into irregular triangular matrix partition and vector multiplication and regularized matrix partition and vector multiplication in a partitioning computing mode; a CPU core in the GPDSP runs an operating system, is in charge of logical partitioning of data and dispatching of tasks and computes the irregular triangular matrix partition and vector multiplication with a small number of loads; DSP cores in the GPDSP are in charge of the regularized matrix partition and vector multiplication, obtain new computing tasks from the CPU core uninterruptedly and report running results to the CPU core, and the CPU core achieves dynamic load balance of the computing tasks among all the DSP cores by means of dynamic dispatching. By means of the method, the principle is simple, operation is convenient, the general purpose computation capacity of the CPU core in the GPDSP and the powerful vector processing array parallel computation and high-bandwidth vector data loading capacity of the DSP cores in the GPDSP can be fully utilized, and the computing memory access ratio of the DSP cores is increased remarkably.

Owner:NAT UNIV OF DEFENSE TECH

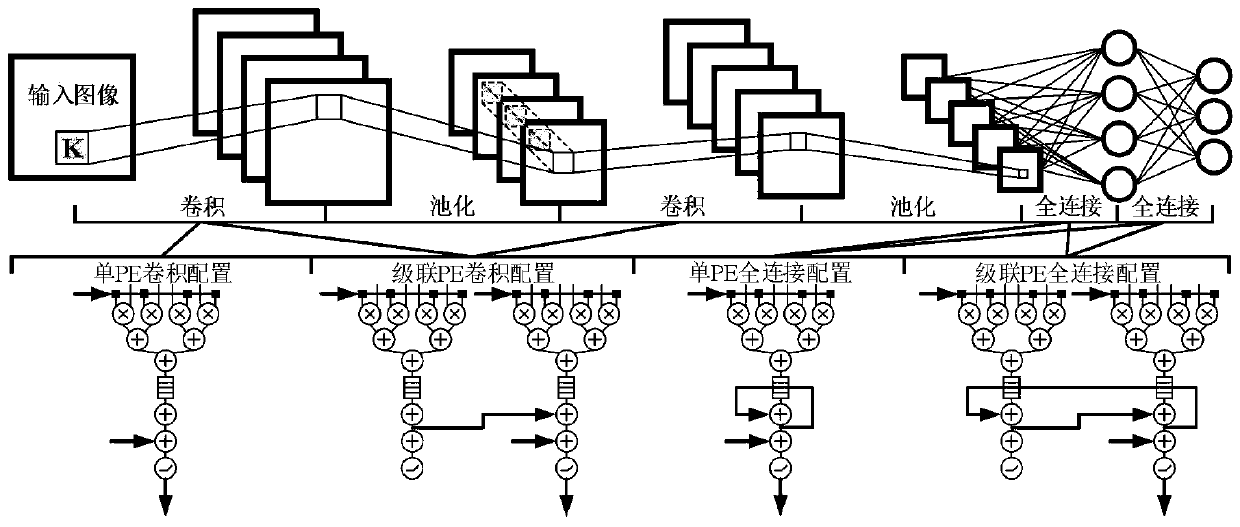

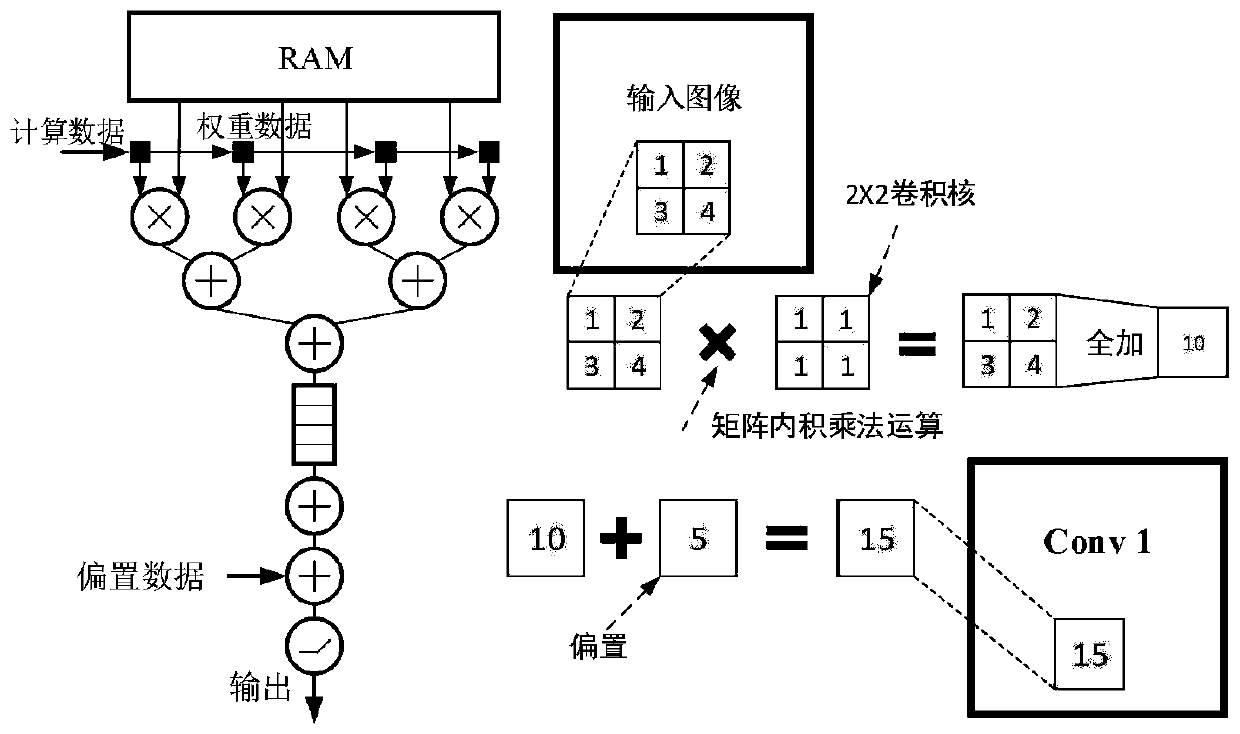

Universal computing circuit of neural network accelerator

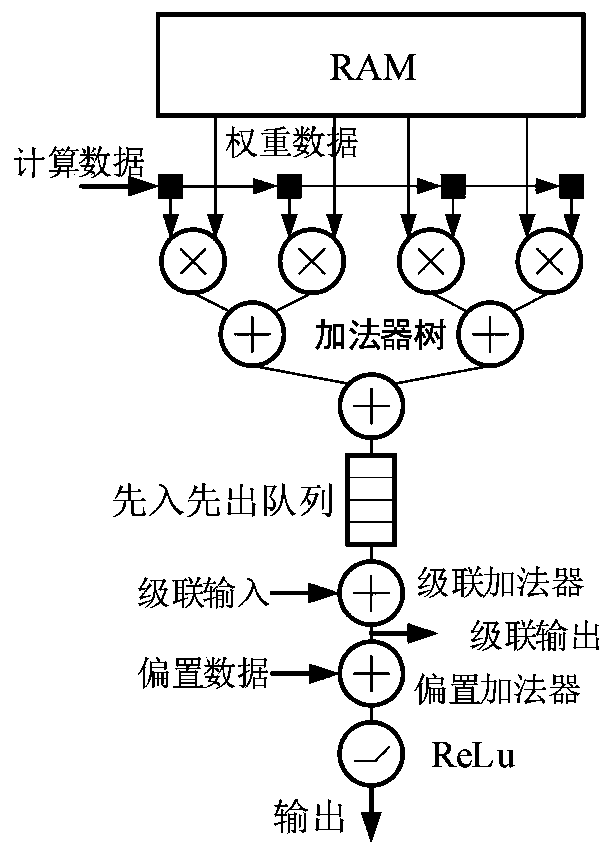

ActiveCN110807522AReduce inference timeSimple designNeural architecturesPhysical realisationActivation functionBinary multiplier

The invention discloses a general calculation module circuit of a neural network accelerator. The general calculation module circuit is composed of m universal computing modules PE, any ith universalcomputing module PE is composed of an RAM, 2n multipliers, an adder tree, a cascade adder, a bias adder, a first-in first-out queue and a ReLu activation function module. The single PE convolution configuration, the cascaded PE convolution configuration, the single PE full-connection configuration graph and the cascaded PE full-connection configuration are utilized to respectively construct calculation circuits of different neural networks. According to the invention, the universal computing circuit can be configured according to the variable of the neural network accelerator, so that the neural network can be built or modified more simply, conveniently and quickly, the inference time of the neural network is shortened, and the hardware development time of related deep research is reduced.

Owner:HEFEI UNIV OF TECH

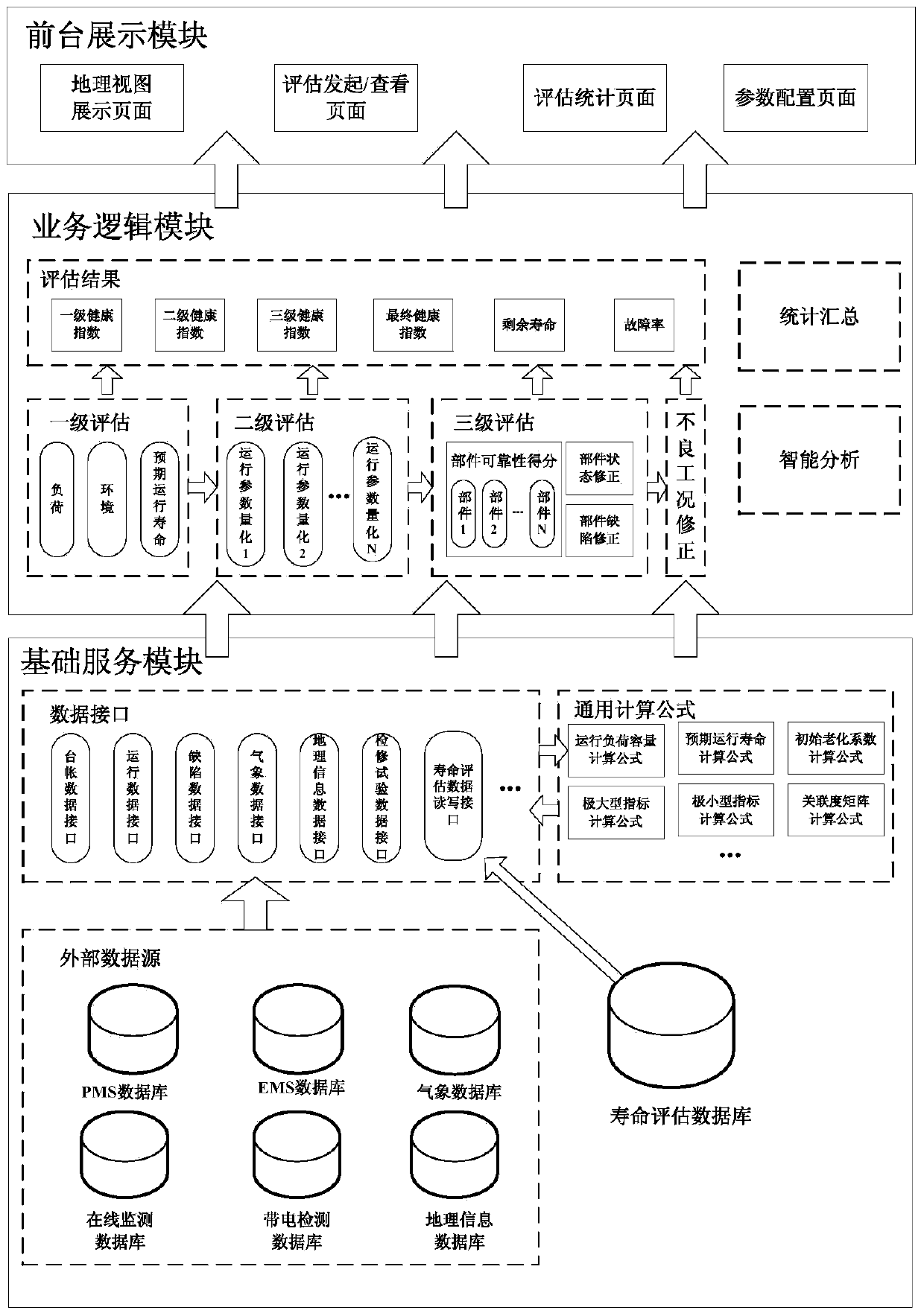

Power grid device service life evaluation platform based on multiple characteristic parameters

InactiveCN103995967ARapid development and deploymentEasy to carry outSpecial data processing applicationsThree levelFailure rate

The invention discloses a power grid device service life evaluation platform based on multiple characteristic parameters. The power grid device service life evaluation platform comprises a basic service module, a business logic module and a foreground displaying module from bottom to top, wherein the basic service module provides data support through a data interface and a general purpose computation formula and abstractly simplifies complicated computation steps. The business logic module achieves three-level evaluation and poor working condition correction and obtains primary / secondary / tertiary health indexes, a final health index, the remaining service life and the failure rate of a power grid device. The foreground displaying module provides a friendly operating interface for a user. The power grid device service life evaluation platform provides the service life condition of the power grid device through multiple-data-source comprehensive application and a series of flexibly-configured evaluation models and achieves visualized displaying. By utilizing the power grid device service life evaluation platform, professionals and developers can perform quick development deployment and dynamic improvement on the service life evaluation system according to the actual demands, and accordingly great convenience is provided for implementation of service life evaluation work.

Owner:STATE GRID CORP OF CHINA +1

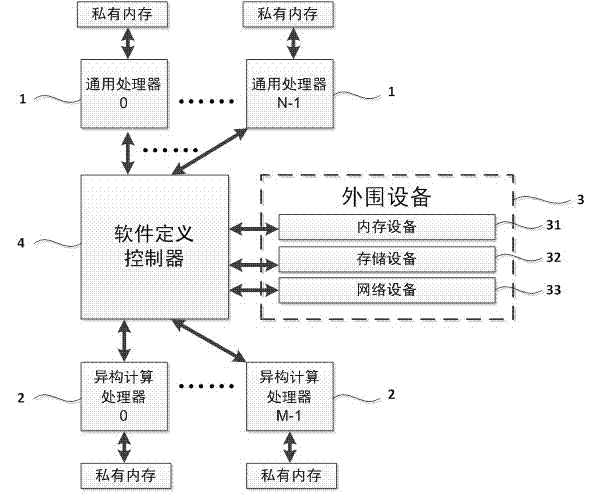

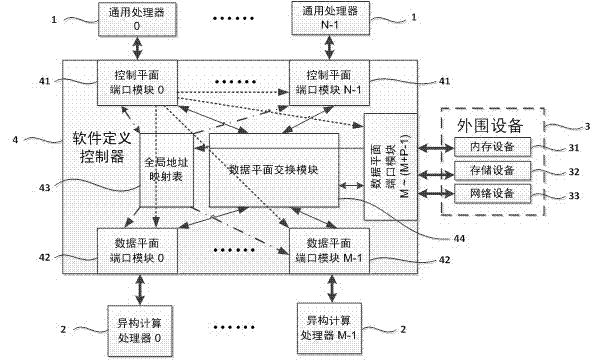

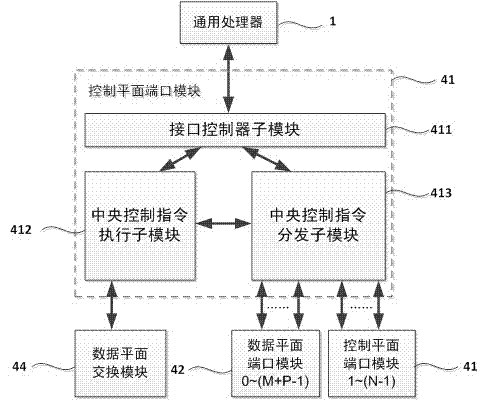

Software definition server system and method for heterogeneous computing

The invention discloses a software definition server system and method for heterogeneous computing. A software definition heterogeneous multiprocessor system comprises a universal processor, a heterogeneous computing processor, a software definition controller and peripheral equipment. The universal processor is used for executing the tasks of a control plane, wherein the tasks comprise the steps of executing a control process of a parallel program, initially configuring the multiprocessor system and providing universal computing capacity. The heterogeneous computing processor (like a GPGPU and other processors) is used for executing the computing task of the parallel program; the software definition controller is used for carrying out data exchange on a data plane between all parts (including the universal processor, the heterogeneous computing processor and the peripheral equipment) in the multiprocessor system; the peripheral equipment comprises an internal storage device (like a DRAM), a storage device (like a disk) and a network device (like a network interface card), and the like.

Owner:QUFU NORMAL UNIV

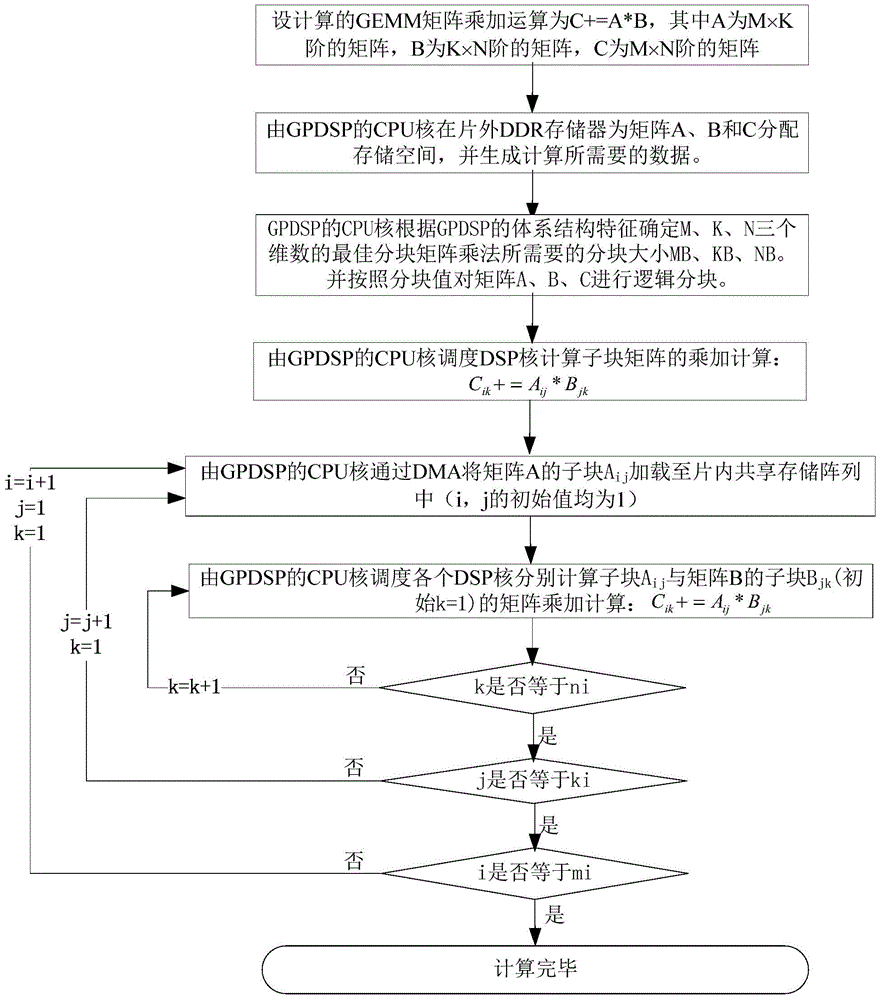

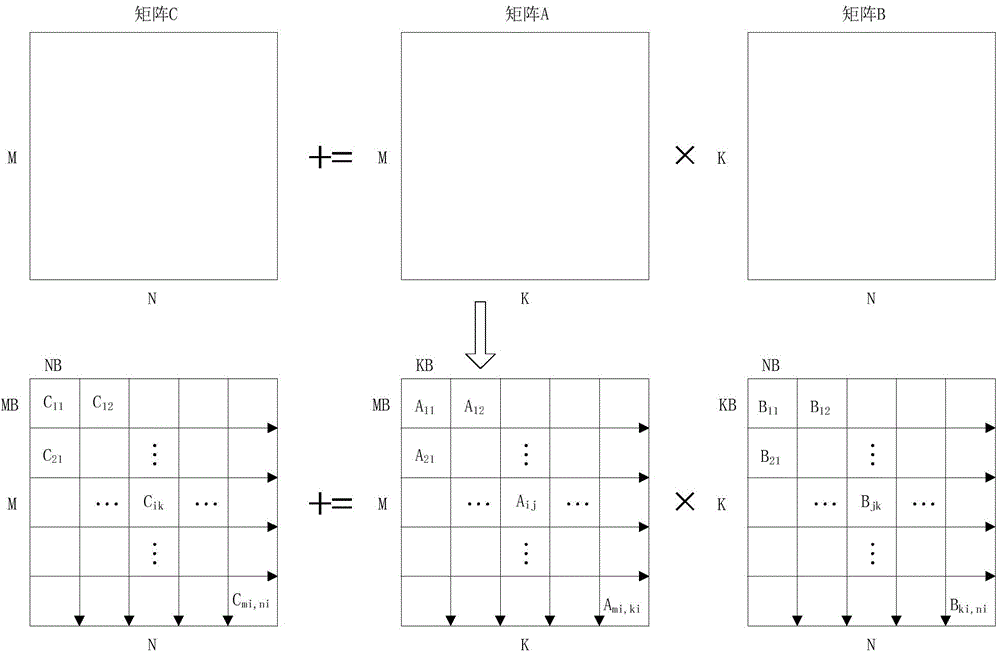

GPDSP-oriented large-scale matrix multiplication calculation method

ActiveCN104636316ACooperate closelyThe principle is simpleDigital data processing detailsComplex mathematical operationsHigh bandwidthParallel computing

The invention discloses a GPDSP-oriented large-scale matrix multiplication calculation method. The method comprises the steps that S1, a CPU core is used for distributing storage space for a matrix A, a matrix B and a matrix C on an off-chip DDR memory, and initialized data are generated or data needed by the calculation are transmitted from other data sources; S2, the best block size MB, KB and NB needed by block matrix multiplication are determined according to the architecture features of a GPDSP system; S3, the CPU core is used for conducting logic block partitioning on the matrix A, the matrix B and the matrix C according to the MB value, the KB value and the NB value determined in the step S2; S4, the CPU core of the GPDSP is used for dispatching a DSP core to conduct the multiplication and addition calculation (please see the specifications for the formula) of subblock matrixes; S5, calculation is completed. According to the GPDSP-oriented large-scale matrix multiplication calculation method, the principle is simple, operation is convenient, the general purpose computation of the CPU core of the GPDSP and the powerful parallel computing and high-bandwidth vector data loading capacity of a DSP core vector processing array are fully utilized, and the DSP core calculation memory access rate is obviously improved.

Owner:NAT UNIV OF DEFENSE TECH

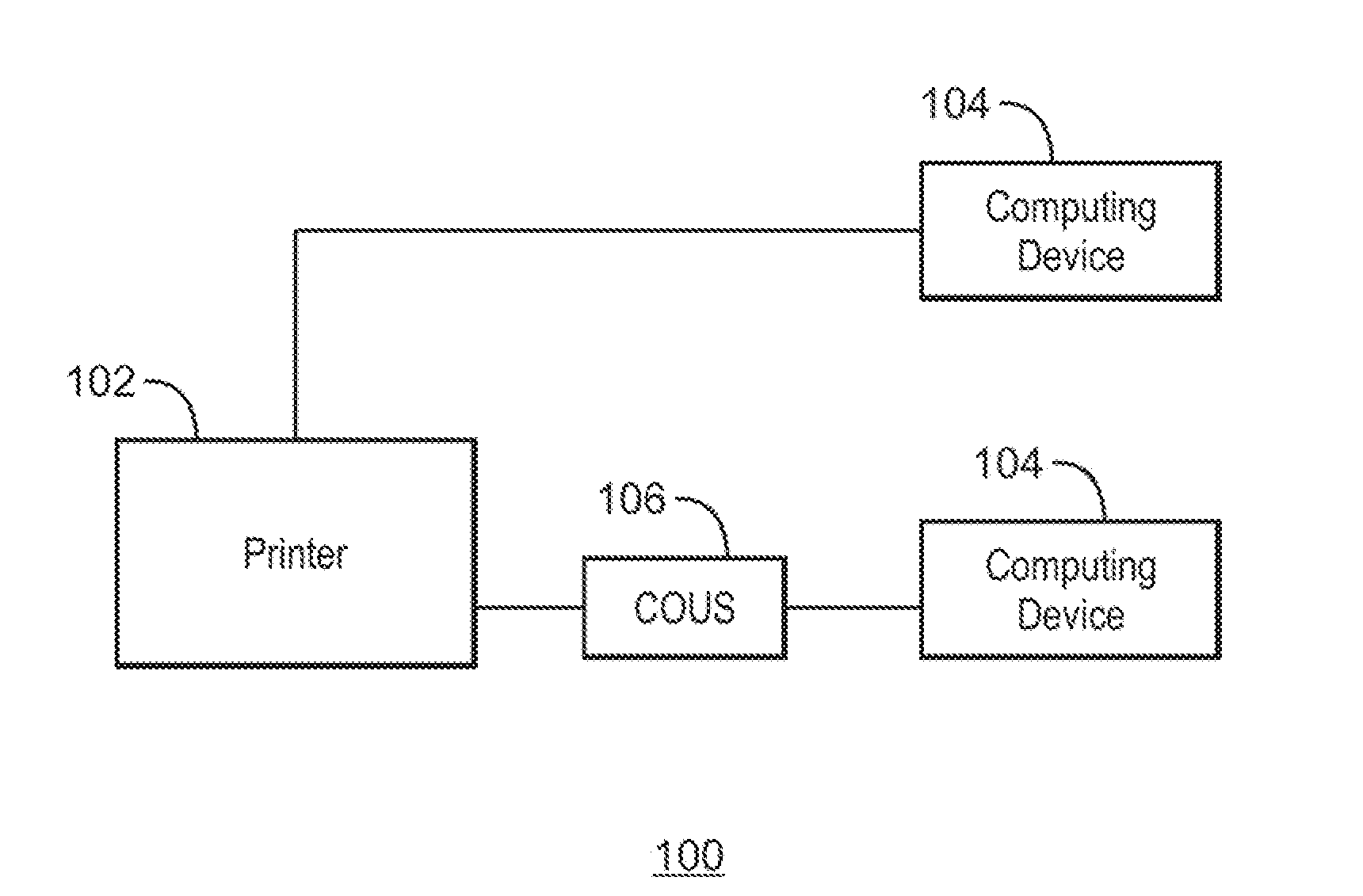

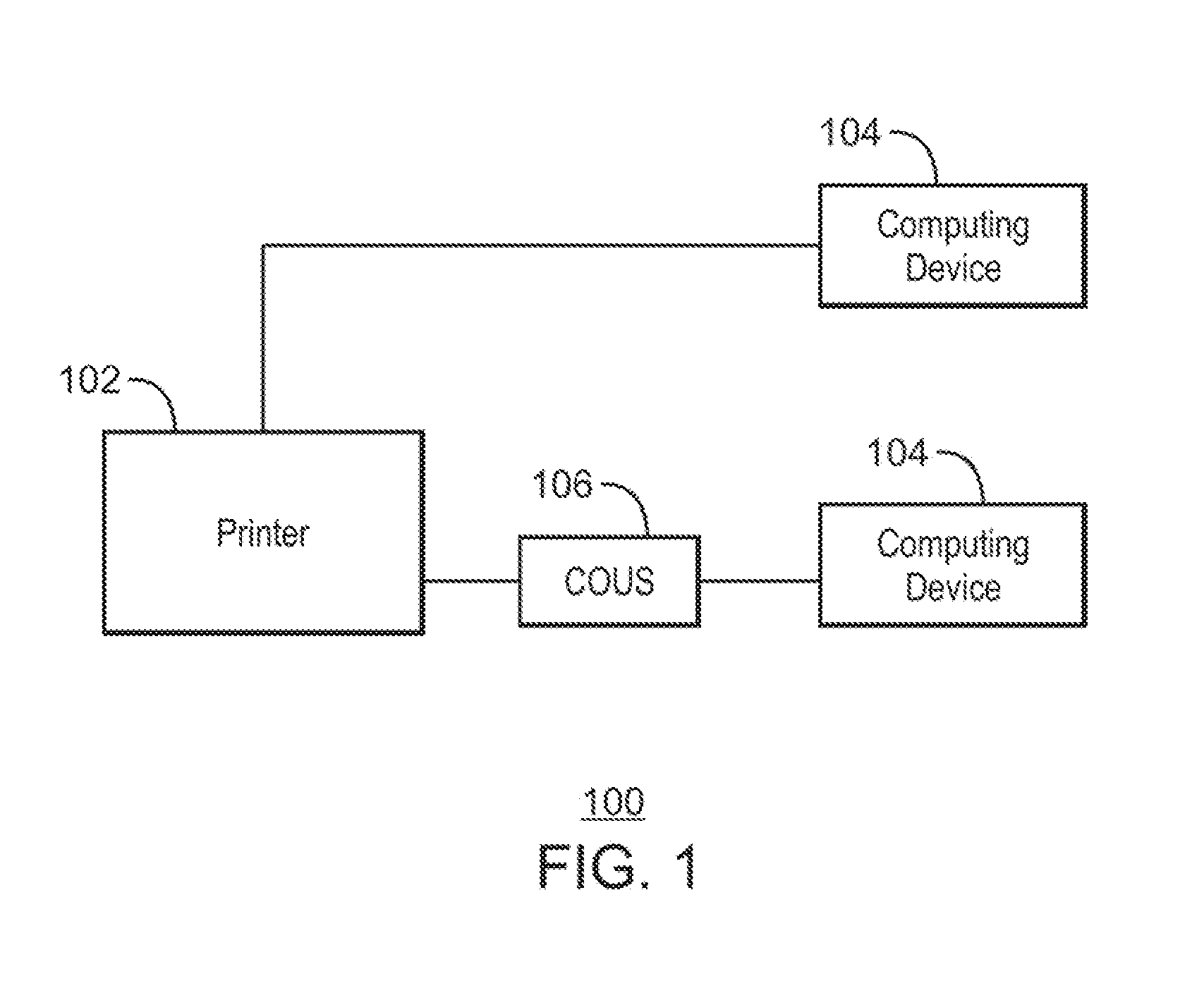

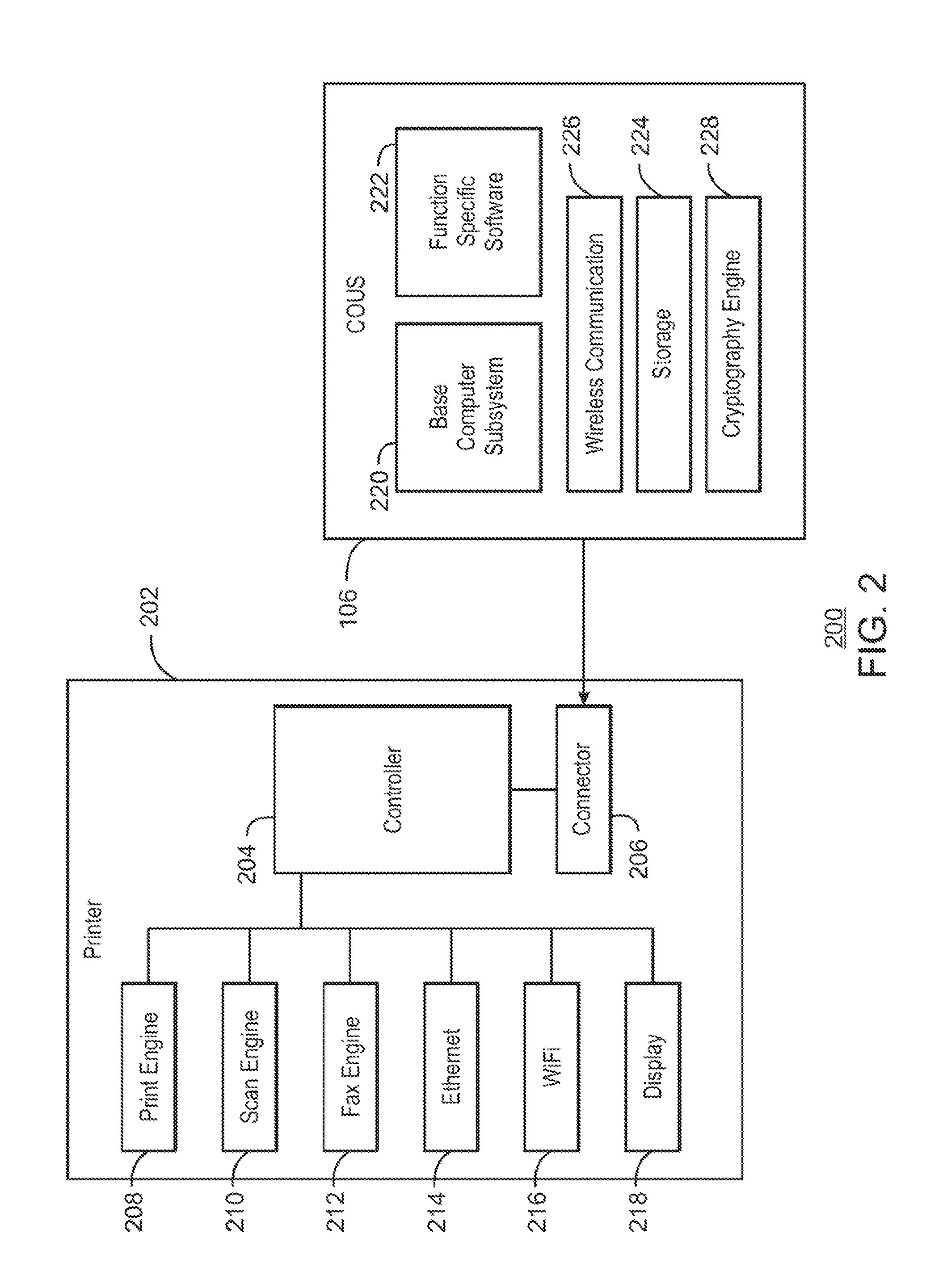

Adding functionality to a printer

A system and method of adding a new printer function to a printer is disclosed herein. The system includes the printer. The system also includes a general purpose computing device communicatively coupled to the printer. The system further includes an upgrade module communicatively coupled to the printer, wherein the upgrade module includes a processor and computer-readable instructions to direct the processor to communicate with the printer to add the new print function to the printer

Owner:INTEL CORP

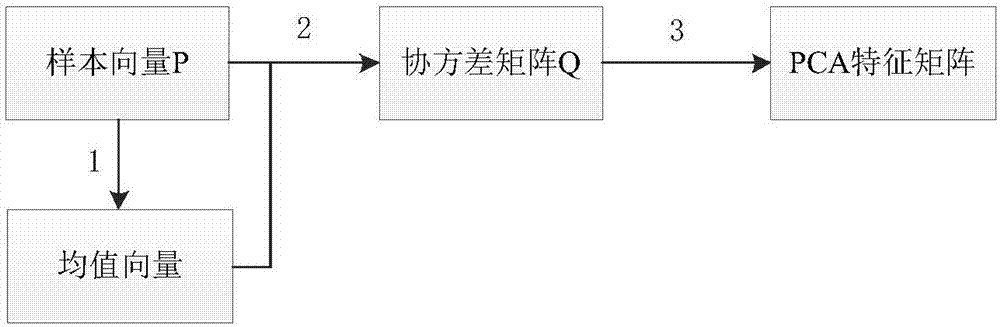

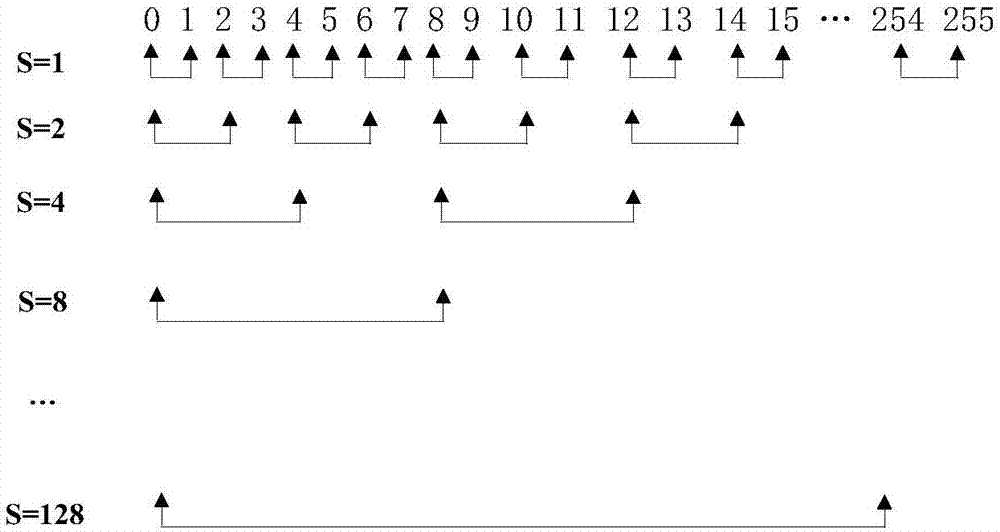

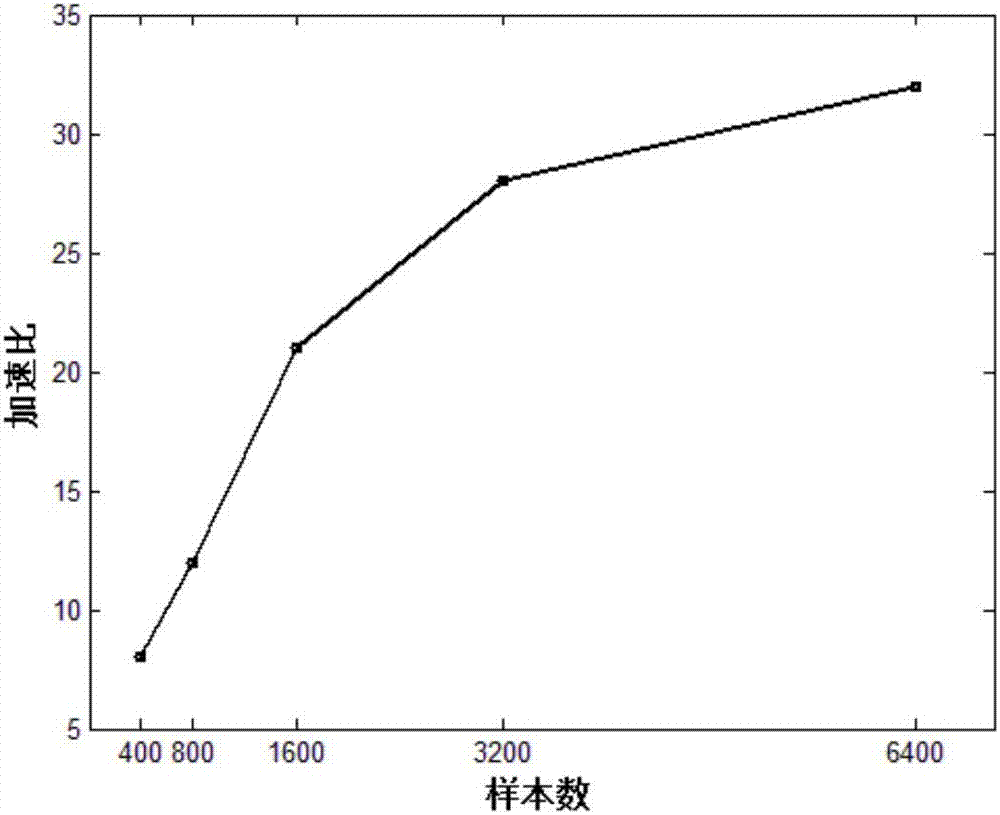

Synthetic aperture radar image target recognition method implemented based on GPU

The invention belongs to the field of radar image target recognition technology and particularly relates to a synthetic aperture radar image target recognition method implemented based on a GPU. Along with development of the SAR imaging technology, the resolution and data size of an SAR image are both increased rapidly, and therefore traditional PCA methods based on CPU serial computation are excessively low in efficiency and excessively high in computation cost. According to the method, efficient computation capability of GPU general purpose computation is utilized to perform parallel analysis on PCA feature extraction methods, and GPU parallel improvement is performed on a matrix multiplication method, a Jacobi feature decomposition method, a reduction maximum value solving method and other methods with high parallelism.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

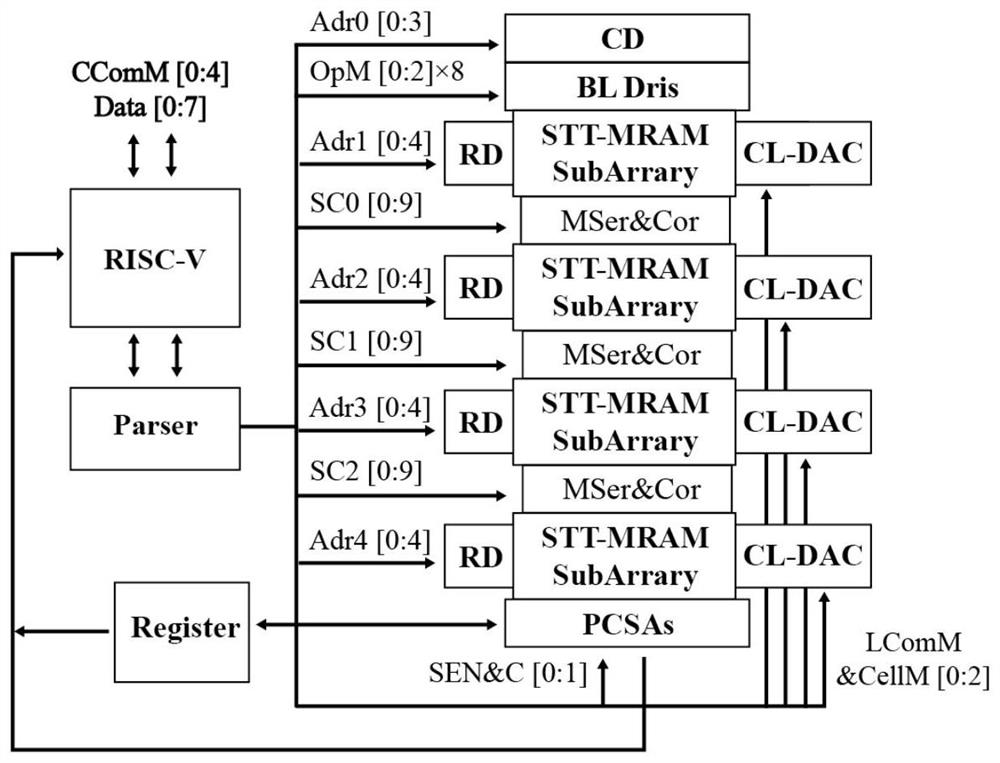

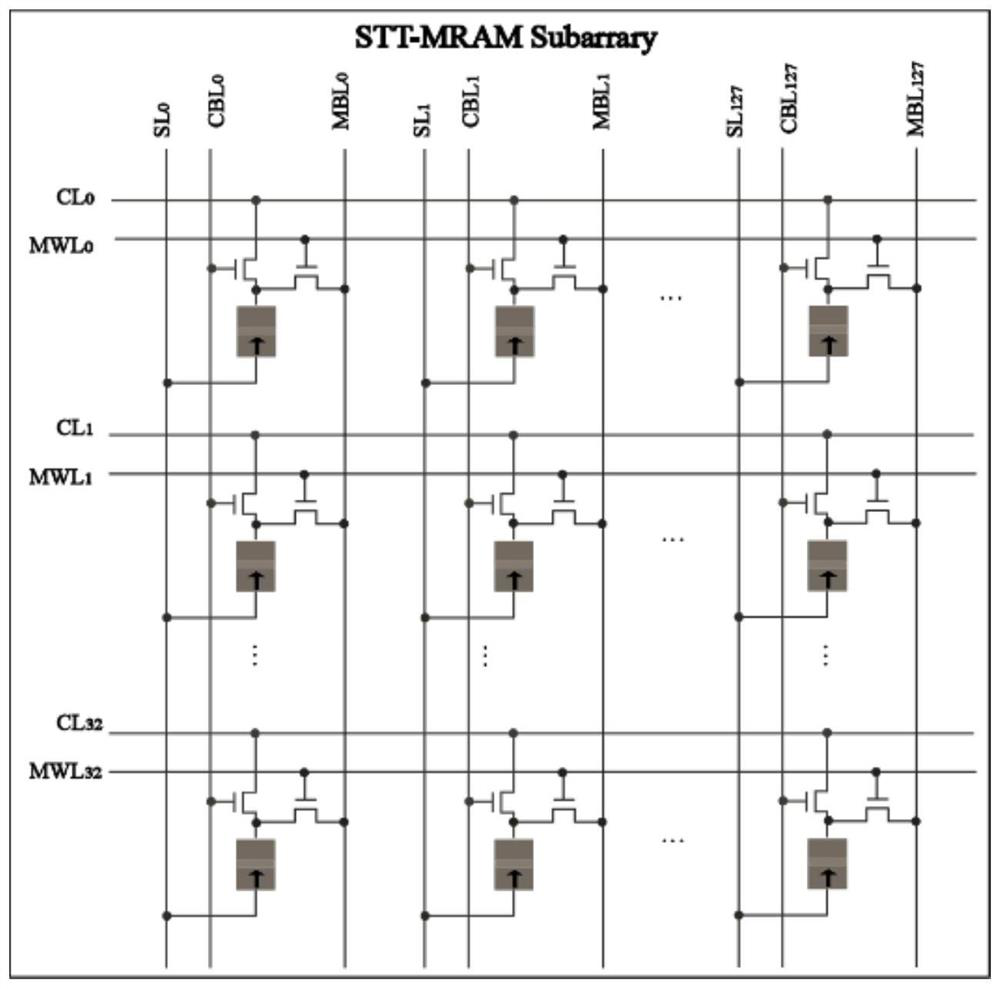

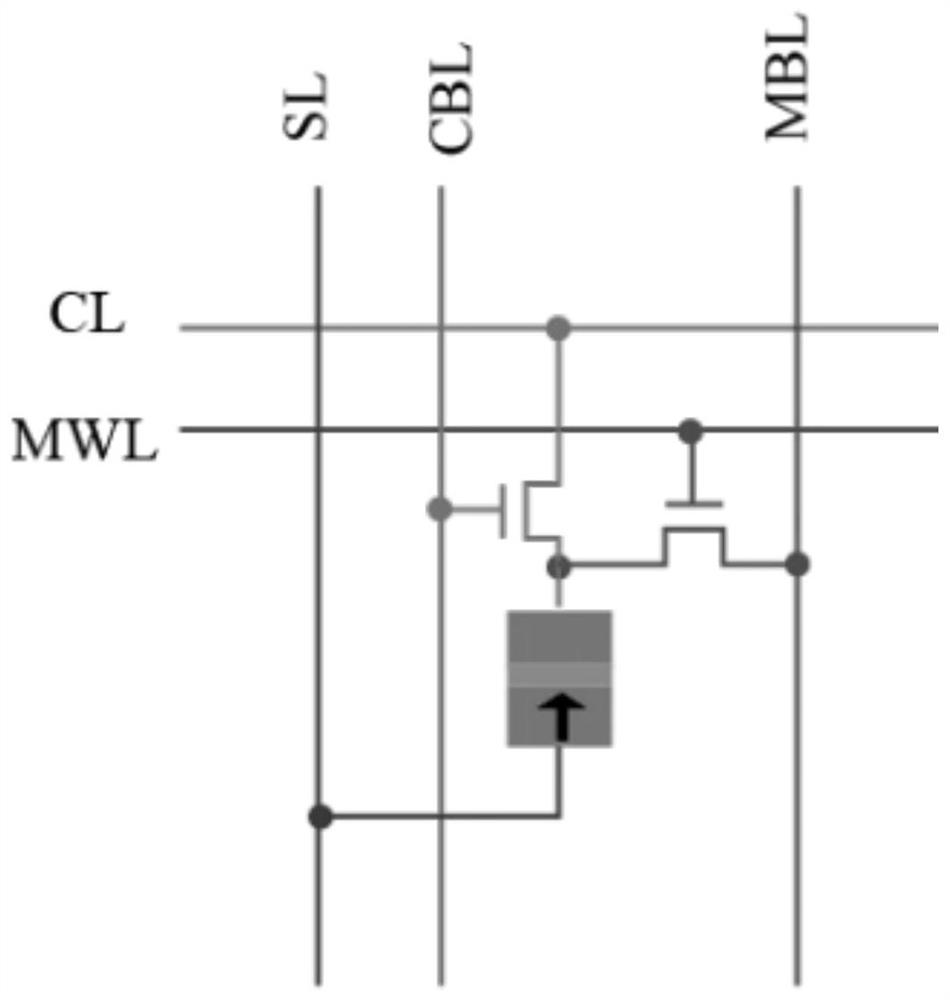

In-memory computing system supporting universal computing based on magnetic random access memory

ActiveCN111798896AImplement storageImprove reconfigurabilityDigital storageBit lineComputer architecture

The invention belongs to the field of general in-memory computing, in particular to an in-memory computing system supporting general computing based on a magnetic random access memory. The in-memory computing system comprises a GCIM architecture, and the GCIM architecture comprises a spin transfer torque magnetic random access memory array, a shifter, a connector, a row decoder, a column decoder,a bit line driver, a calculation word line digital-to-analog converter, a pre-charging induction amplifier, a fifth-generation reduced instruction set processor, an instruction parser and a register.According to the invention, storage can be realized in the memory, and calculation operation can be carried out in the memory. Moreover, the method can effectively support general calculation (including logic calculation, fixed-point calculation, floating-point calculation and the like), fully utilizes a plurality of sub-array structures and improved shifters and connectors, improves the reconfigurability and calculation parallelism of the architecture, and improves the calculation efficiency.

Owner:BEIHANG UNIV

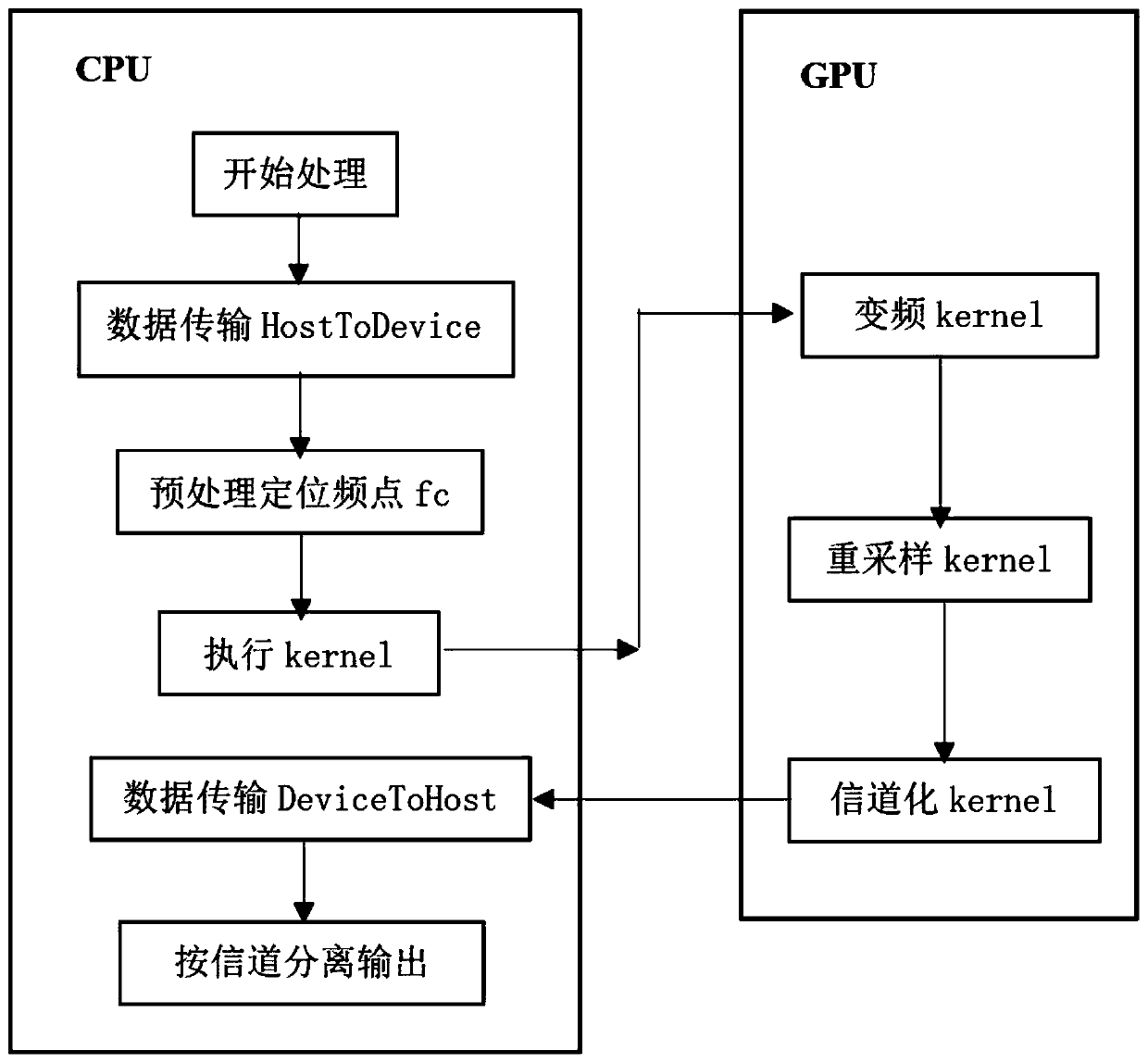

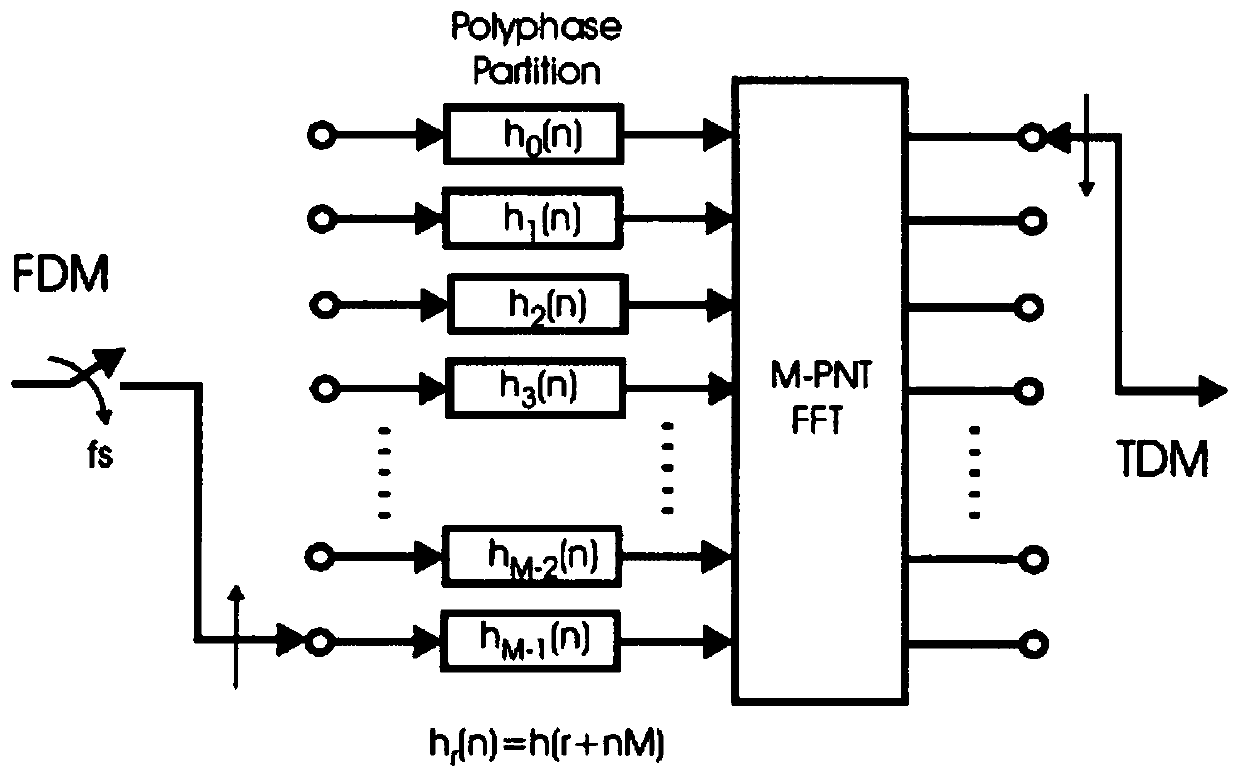

GPU-based broadband signal DDC system design method

ActiveCN111552559AWith group processing functionReduce computational complexityProgram initiation/switchingResource allocationDigital signal processingComputer architecture

The invention discloses a GPU (Graphics processing unit)-based broadband signal DDC (Direct Down Conversion) system design method, which aims at executing a complex digital signal processing functionin parallel by utilizing a lightweight thread and a kernel of a GPU and mainly completing two tasks, namely digital channelization and sampling rate change. A multiphase filtering digital channelization method is taken as a scheme main body, and a group processing function for broadband acquisition signals is realized, and DDC sampling data is output in parallel in multiple paths. And an efficientresampling method is combined, so that the system is matched with any output sampling rate. According to the GPU-based broadband signal DDC system design method, the powerful general computing powerof the GPU is used; and the parallelism degree of the algorithm is mined, and the algorithm is transplanted to a GPU heterogeneous platform through CUDA programming, and heterogeneous parallel optimization means such as memory optimization, thread organization scheduling optimization and stream processing architecture are adopted, so that the algorithm complexity is effectively reduced, and the scheme has high throughput and high flexibility and adapts to a real-time processing environment.

Owner:SHANGHAI UNIV

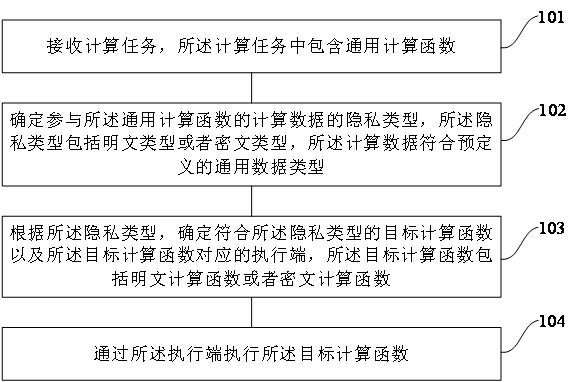

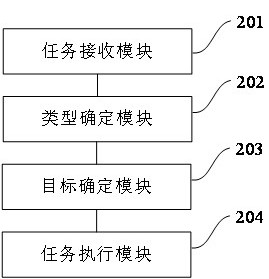

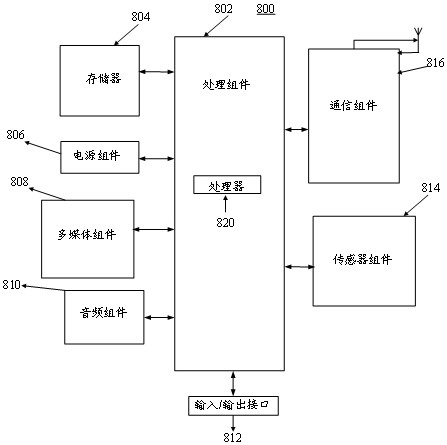

Data processing method and device and device for data processing

ActiveCN113449325AGuaranteed privacy and securityGuaranteed Computational EfficiencyDigital data protectionAlgorithmCiphertext

The embodiment of the invention provides a data processing method and device and a device for data processing. The method comprises the steps that a calculation task is received, and the calculation task comprises a general calculation function; the privacy type of calculation data participating in the general calculation function is determined, the privacy type comprises a plaintext type or a ciphertext type, and the calculation data accords with a predefined general data type; according to the privacy type, a target calculation function conforming to the privacy type and an execution end corresponding to the target calculation function are determined, and the target calculation function comprises a plaintext calculation function or a ciphertext calculation function; and the target calculation function is executed through the execution end. According to the embodiment of the invention, the calculation efficiency can be improved on the basis of ensuring the data privacy security.

Owner:HUAKONG TSINGJIAO INFORMATION SCI BEIJING LTD

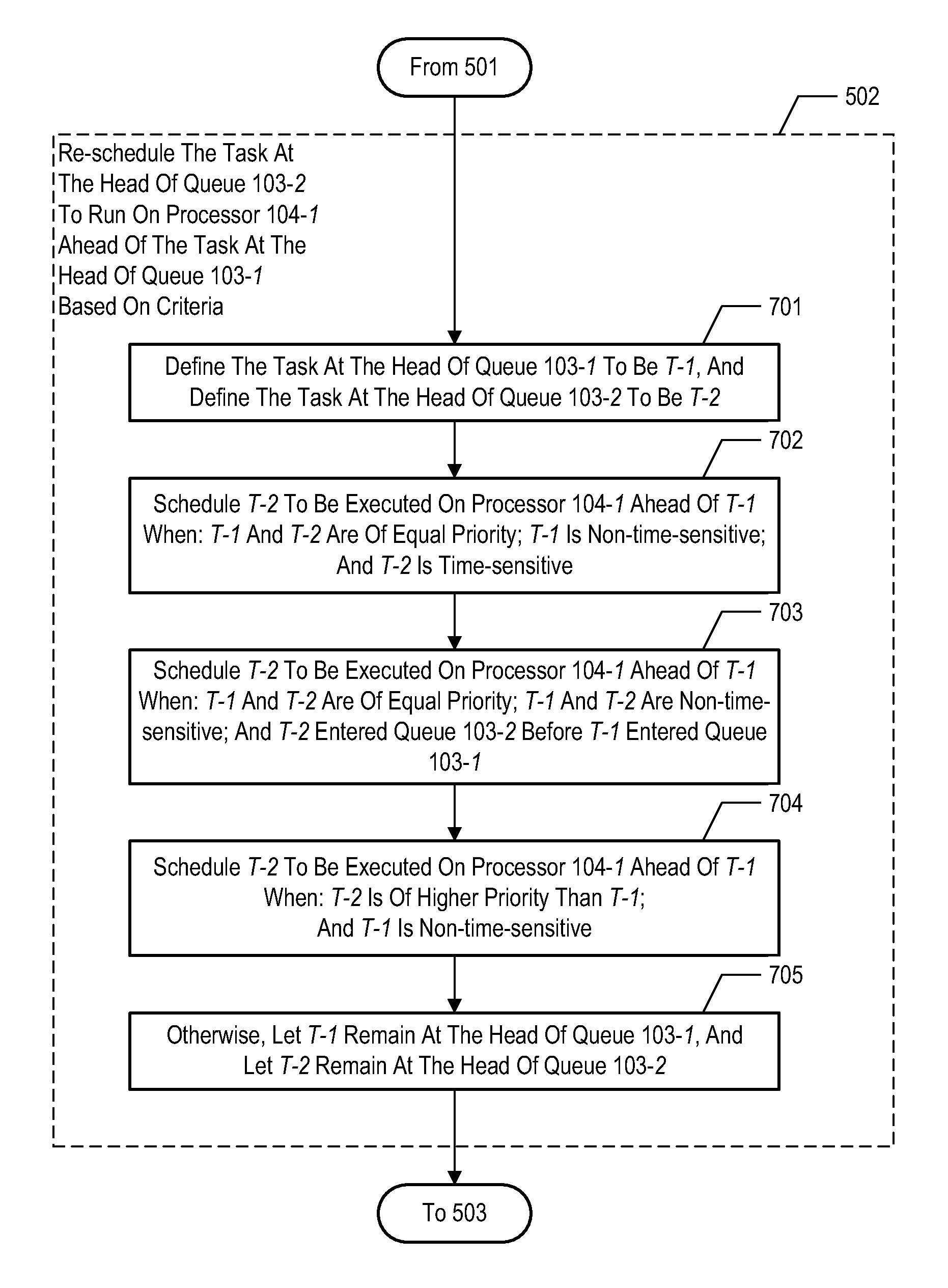

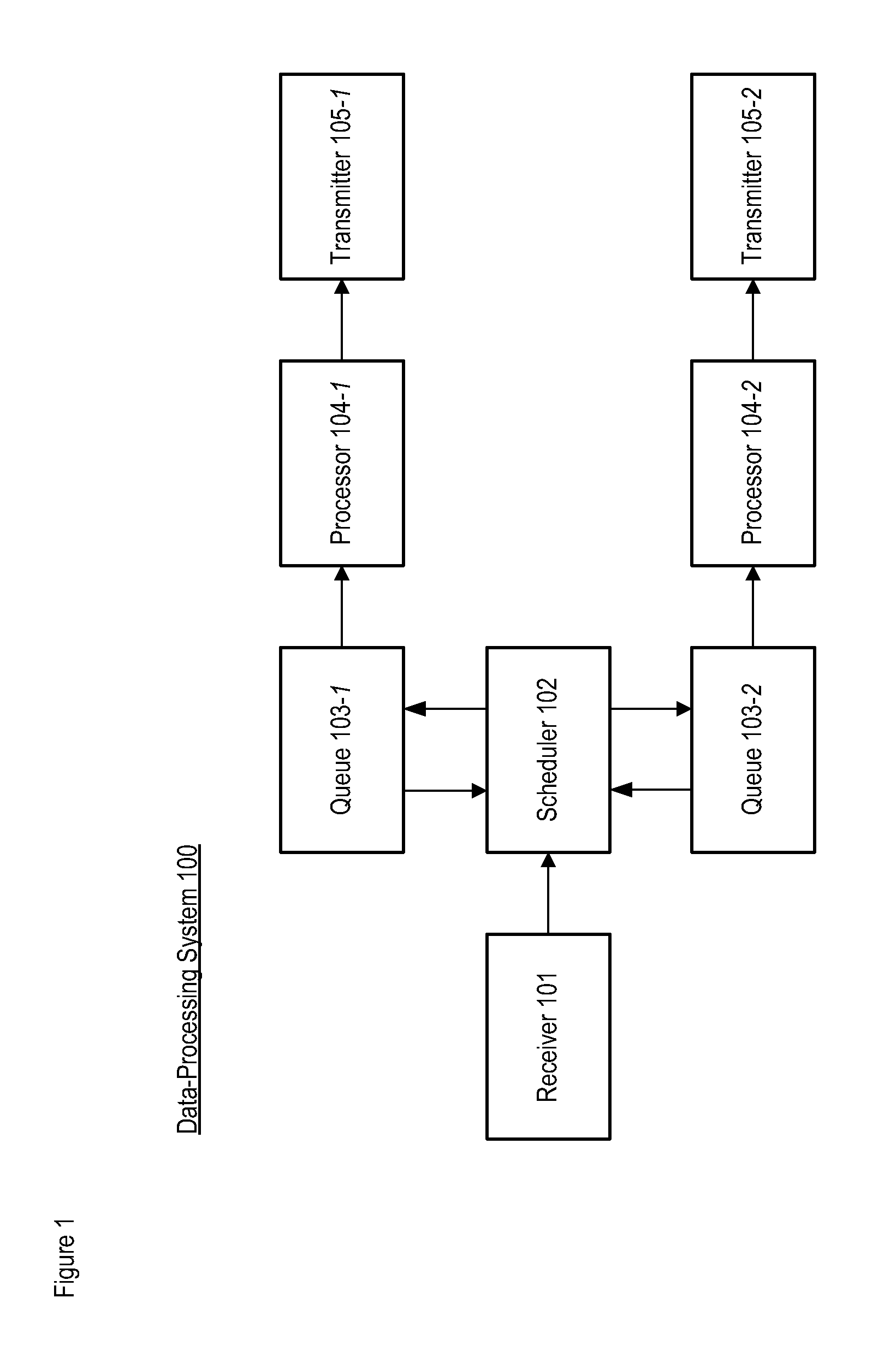

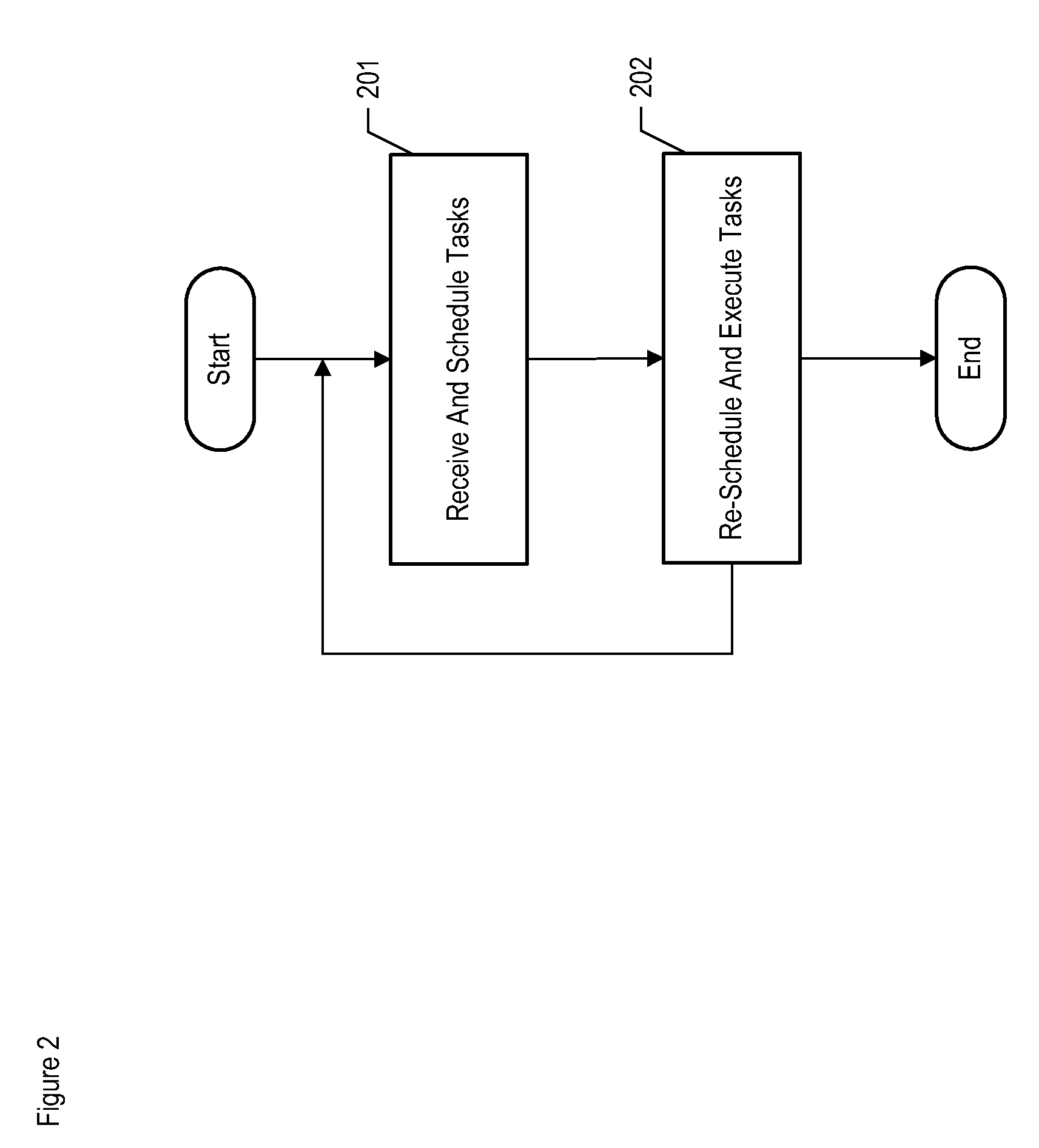

Soft real-time load balancer

ActiveUS8161491B2Reduces “ starvation ”Suitable for processingDigital computer detailsMultiprogramming arrangementsVirtualizationLoad Shedding

Owner:AVAYA INC

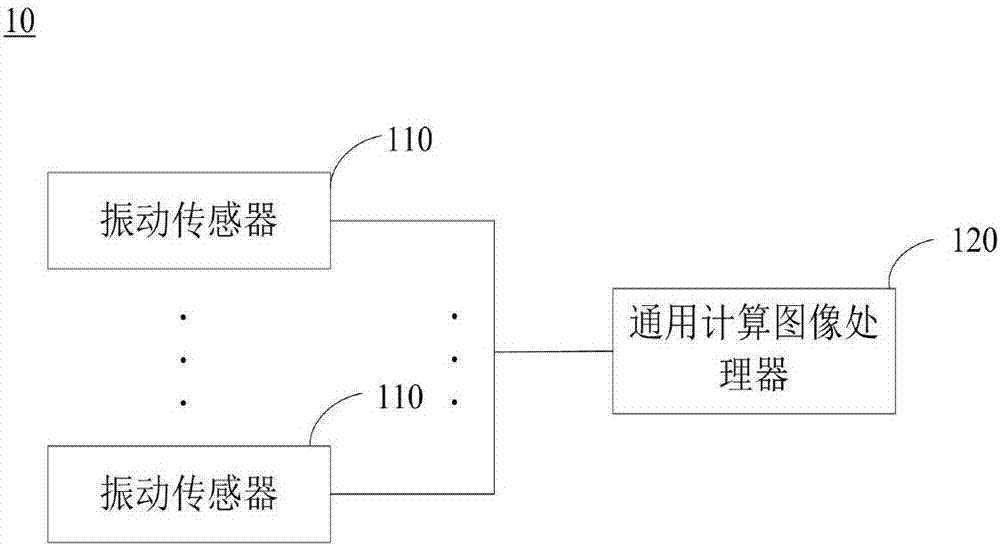

A vibration test system and an analysis method for vibration signal time domain waveforms thereof

InactiveCN107462318AImprove practicalityRealize synchronous acquisitionSubsonic/sonic/ultrasonic wave measurementUsing electrical meansField analysisVIT signals

The invention provides a vibration test system used for rotary machines. The vibration test system comprises a plurality of vibration sensors used for acquiring multiple paths of vibration signals of a rotary machine and a general purpose computation image processor used for processing, display, computation and analysis of the multiple paths of vibration signals. The vibration sensors include eddy current displacement sensors used for acquiring key phase point signals. The general purpose computation image processor comprises a signal processing module used for conditioning, analog-digital conversion and encoding of the vibration signals and a monitoring module which displays the multiple paths of processed vibration signals in the time domain waveform image form and performs computation and analysis on the signals. The vibration test system has the advantages that the eddy current displacement sensors and the general purpose computation image processor cooperate to acquire vibration signals with key phase information for field analysis and judgment, so that multiple paths of vibration signals can be analyzed and processed synchronously and the practicality is great. The invention also provides an analysis method for vibration signal time domain waveforms of the vibration test system.

Owner:SHENZHEN YATEKS OPTICAL ELECTRONICS TECH CO LTD

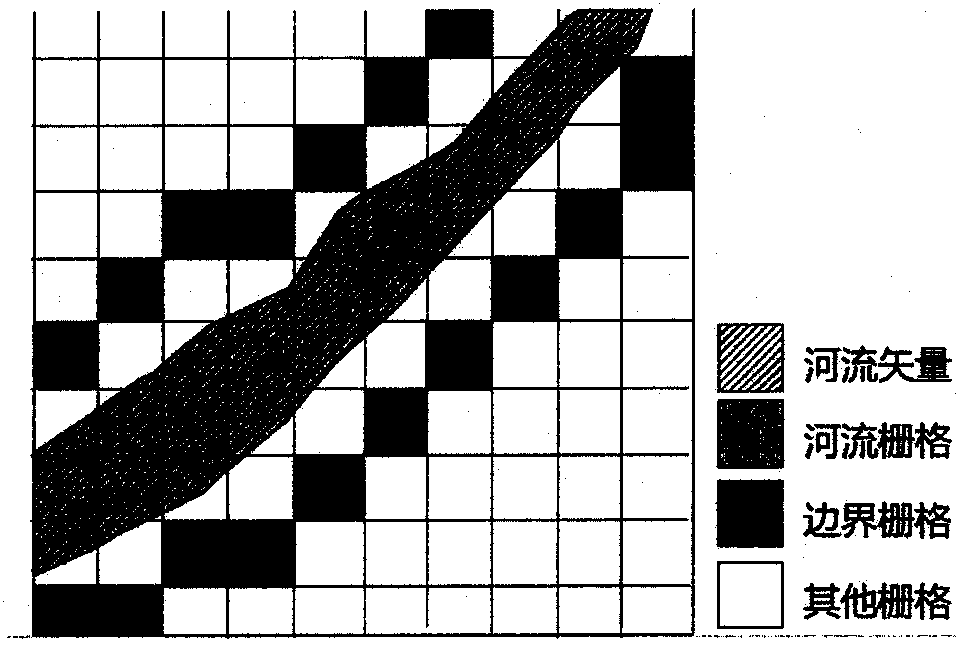

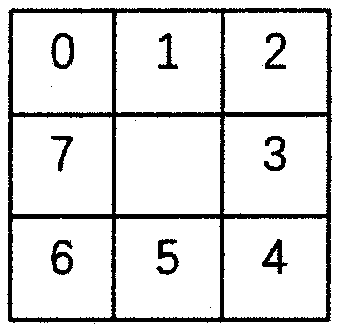

Basin water quality real-time simulation method based on general calculation

PendingCN110837684AGuaranteed parallelismDesign optimisation/simulationCAD numerical modellingParallel algorithmEnvironmental engineering

The invention discloses a basin water quality real-time simulation method based on general calculation. The basin water quality real-time simulation method comprises the following steps: dividing basin grids under a general calculation framework; and performing parallelization design of a basin water quality model, wherein the step S1 comprises sequentially executing contents listed in 1.1, 1.2 and 1.3; 1.1, dividing basin grids in a grid mode; 1.2, defining a simulation grid; 1.3, constructing a grid neighborhood topology, and the step S2 comprises sequentially executing contents listed in 2.1, 2.2, 2.3, 2.4 and 2.5; 2.1, universally calculating basic requirements on a water quality model; 2.2, simulating attributes of the grids; 2.3, designing a hydrodynamic parallel algorithm of the simulation grid; 2.4, designing a water quality simulation parallel algorithm of a simulation grid. According to the simulation method, the water quality can be simulated in real time, and the simulationprecision also reaches an ideal effect.

Owner:CHENGDU UNIV OF INFORMATION TECH

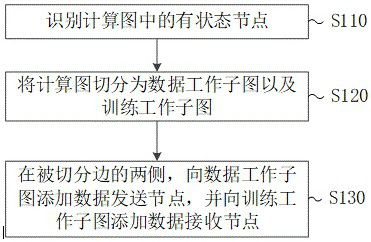

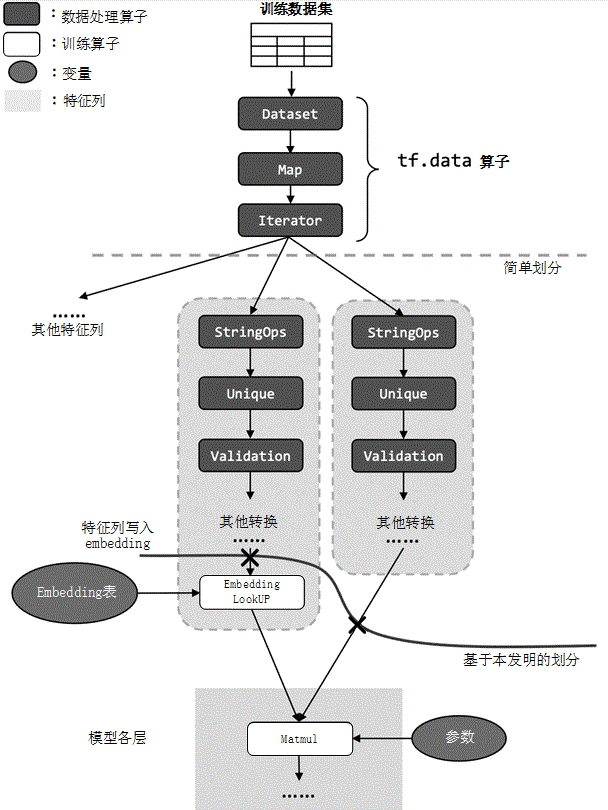

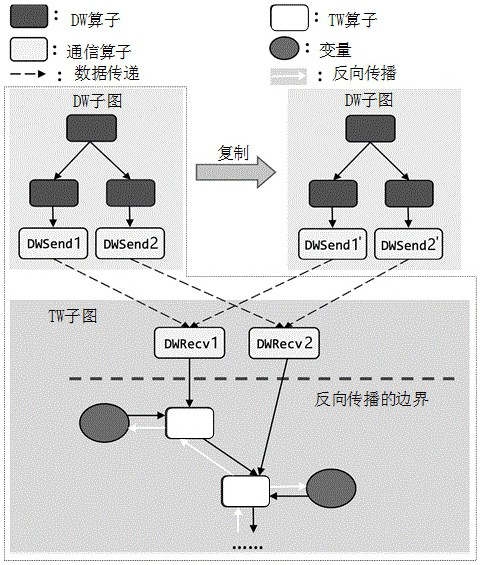

Machine learning calculation optimization method and platform

ActiveCN114418127AImprove processing efficiencyMeet different requirementsMachine learningEnergy efficient computingEngineeringData mining

The invention discloses a machine learning calculation optimization method and platform. The method comprises the following steps: segmenting a machine learning calculation graph into a data working sub-graph consisting of upstream nodes of stateful nodes and a training working sub-graph consisting of stateful nodes and downstream nodes thereof, and adding data sending nodes to the data working sub-graph at two sides of a segmented edge, and adding a data receiving node to the training work sub-graph. According to the method, data and training work in the same task can be decoupled, so that general computing resources participating in the data work during operation can be dynamically allocated; the problem that the running efficiency of a deep learning task is reduced due to the fact that enough preprocessing data cannot be provided for a special computing unit such as a GPU is solved. Furthermore, through combination with a scheduler, general computing resource scheduling can be carried out in a cluster range, a single-machine boundary is broken, and the overall hardware utilization efficiency of the platform is improved.

Owner:ALIBABA CLOUD COMPUTING LTD

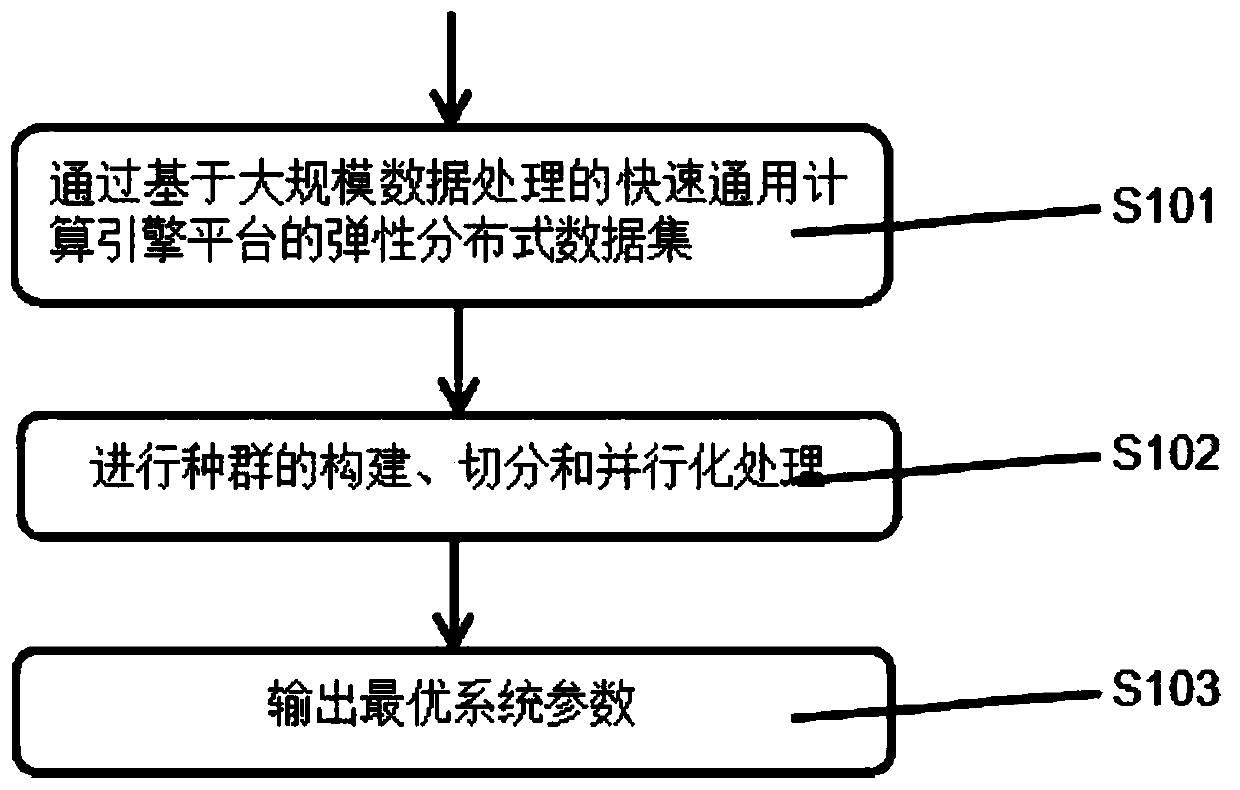

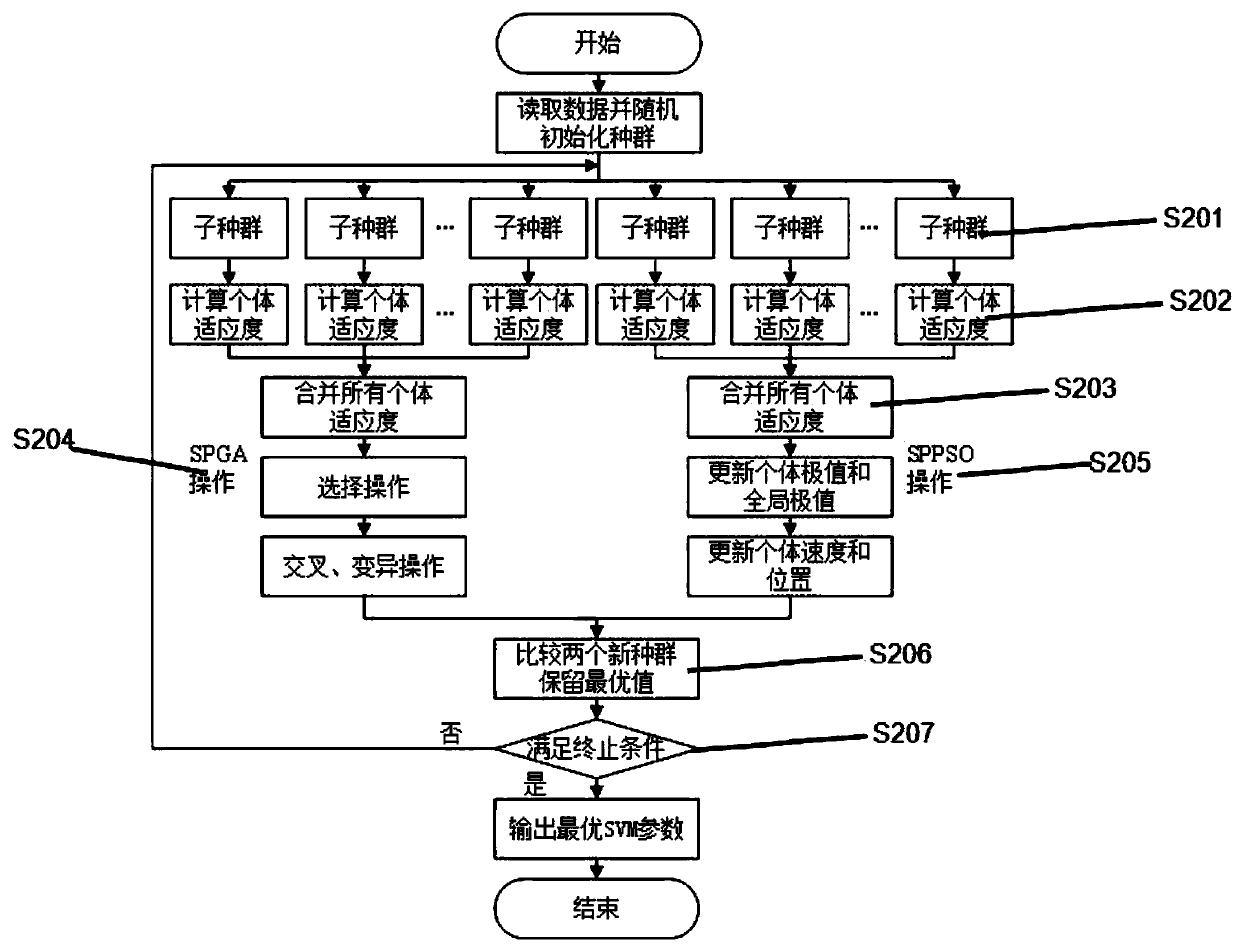

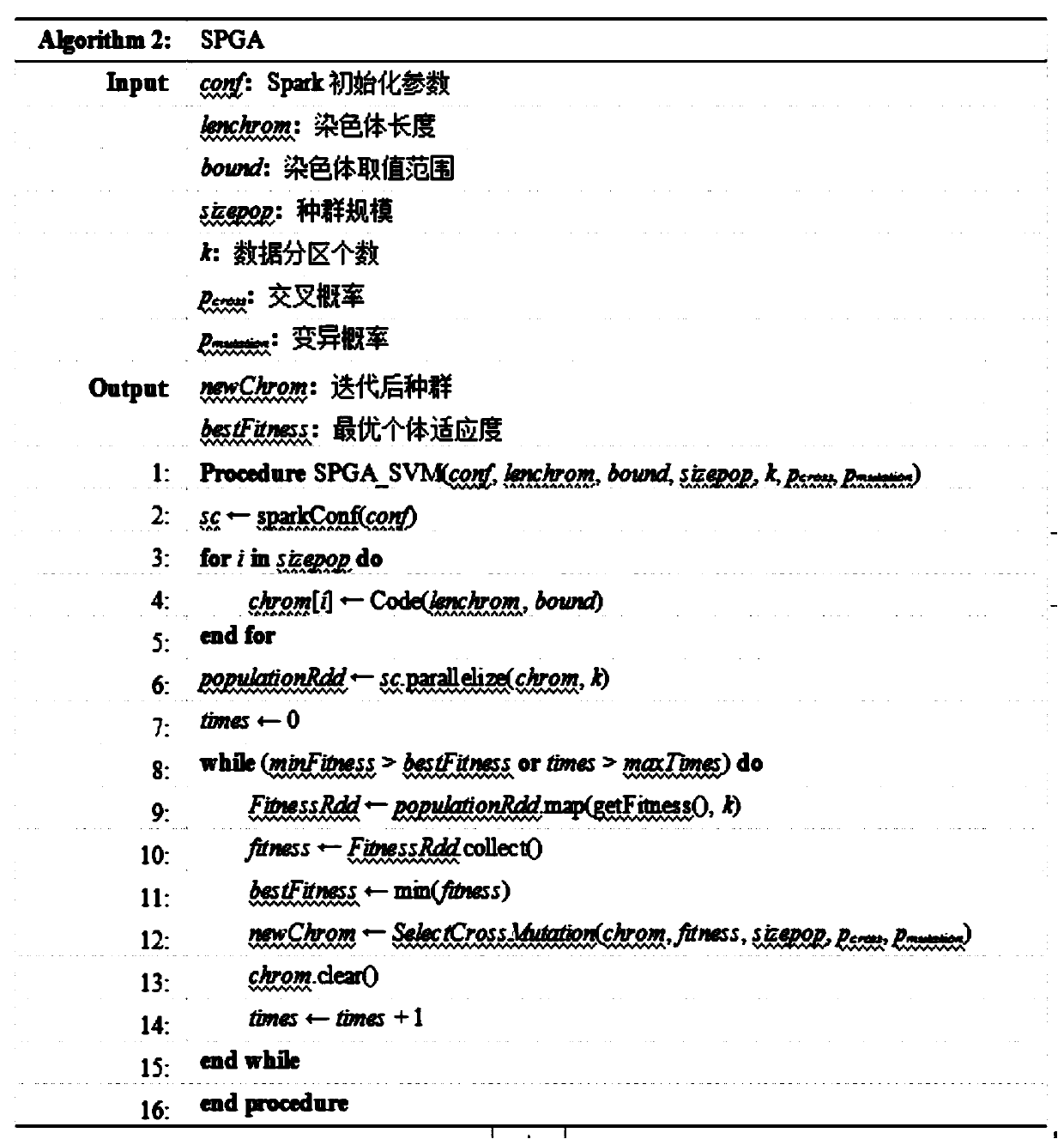

Bus passenger flow volume prediction method and system based on SPGAPSO-SVM algorithm

InactiveCN110766237ARun fastSolve the low prediction accuracyKernel methodsForecastingTraffic predictionData set

The invention belongs to the technical field of bus passenger flow volume prediction, in particular to a bus passenger flow prediction method and system based on an SPGAPSO-SVM algorithm. The method comprises the steps that population construction, segmentation and parallelization processing are carried out through an elastic distributed data set of a rapid universal computing engine platform based on large-scale data processing; optimal system parameters are output. According to the method, the problem that in the prior art, the time consumed for calculating the fitness of an existing prediction model is too long is solved, and the method has the beneficial technical effects of being high in prediction accuracy, high in operation speed and good in expandability.

Owner:INNER MONGOLIA UNIV OF TECH

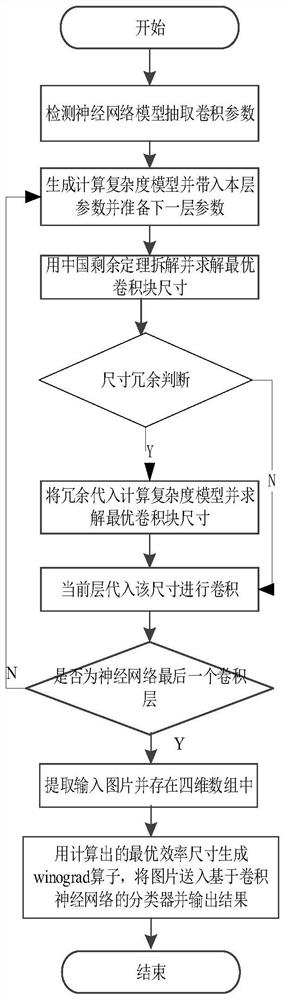

Image processing method based on winograd dynamic convolution block

PendingCN112434786AQuick calculationSolve the problem of convolution performance degradationNeural architecturesNeural learning methodsImaging processingComputation complexity

The invention discloses an image processing method based on winograd dynamic convolution blocks, and belongs to the field of convolution networks. According to the invention, a calculation complexityfunction of a winograd rapid convolution method is generated by using a Chinese remainder theorem algorithm, and convolution parameters of each layer in a convolutional neural network model are introduced as constants by the calculation complexity function to obtain a calculation complexity model of which the variable is the size of a winograd convolution block; the method also includes minimizingthe computation overhead based on the computation complexity model; according to the convolution block size obtained by minimizing the calculation overhead, completing winograd rapid convolution calculation of the corresponding layer number; extracting features of the pictures and sending the features to a convolutional neural network for classification processing; according to the invention, theproblem of convolution performance reduction caused by unbalanced efficiency of a single convolution block of a winograd algorithm on a general computing platform is solved, and the image processingmethod can accelerate the computation of the convolutional neural network computed by the processor.

Owner:XI AN JIAOTONG UNIV