High-speed three-level parallel analog-to-digital converter of CMOS image sensor and operation method of high-speed three-level parallel analog-to-digital converter

An image sensor, analog-to-digital technology, applied in the field of high-speed three-level parallel analog-to-digital converter and its calculation, can solve the problems of low internal operation speed and conversion efficiency that cannot meet the needs of use, so as to save layout area and improve analog/digital Effect of Slew Rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

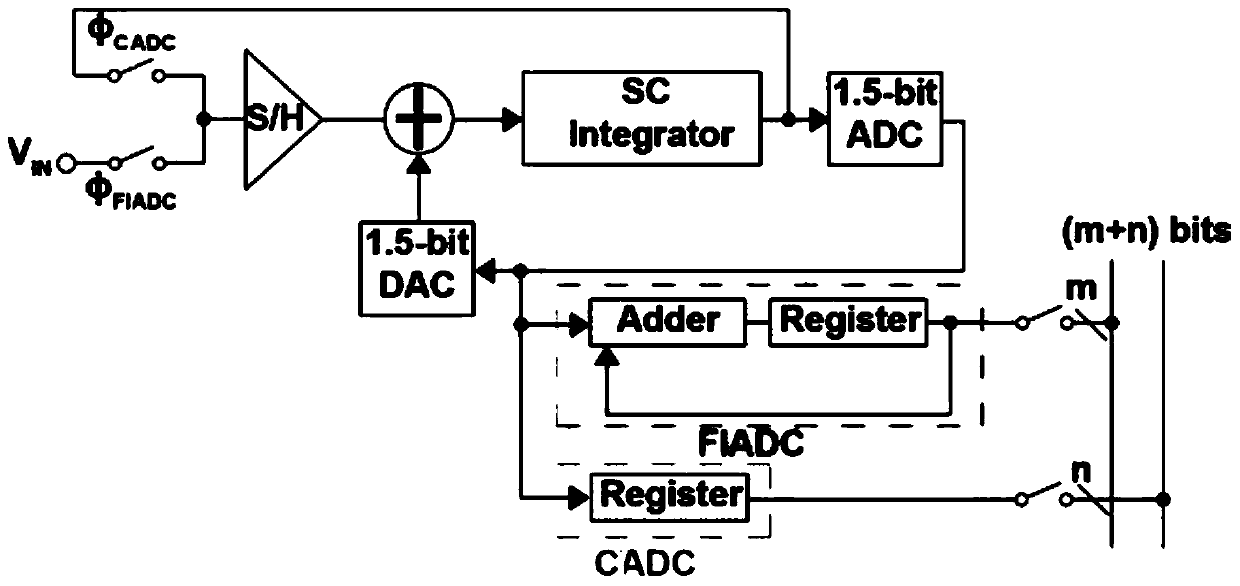

[0021] see figure 1 , what this embodiment provides is the high-speed three-stage parallel analog-to-digital converter of the CMOS image sensor, including CADC timing switching switch Φ CADC , Sampling and holding circuit S / H, FIADC timing switch Φ FIADC , Shared analog modules, FIADC, CADC, SSADC and counters.

[0022] FIADC is a folded integrated analog-to-digital converter, CADC is a circular analog-to-digital converter, and SSADC is a single-slope analog-to-digital converter.

[0023] Specifically, the shared analog-electric module in this embodiment includes a switched capacitor integrator SC Integrator, a 1.5-bit ADC, and a 1.5-bit DAC (digital-to-analog converter). Its specific structure is that the switched capacitor integrator SC Integrator is connected in series to the 1.5-bit ADC, the 1.5-bit ADC is connected in series to the 1.5-bit DAC, the 1.5-bit DAC is connected in series to the 1.5-bit ADC, and the switched capacitor integrator SC Integrator, 1.5-bit ADC an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com