Semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of semiconductor devices and their formation, can solve problems affecting the performance of semiconductor devices, difficulties, and insufficient filling of metal gates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

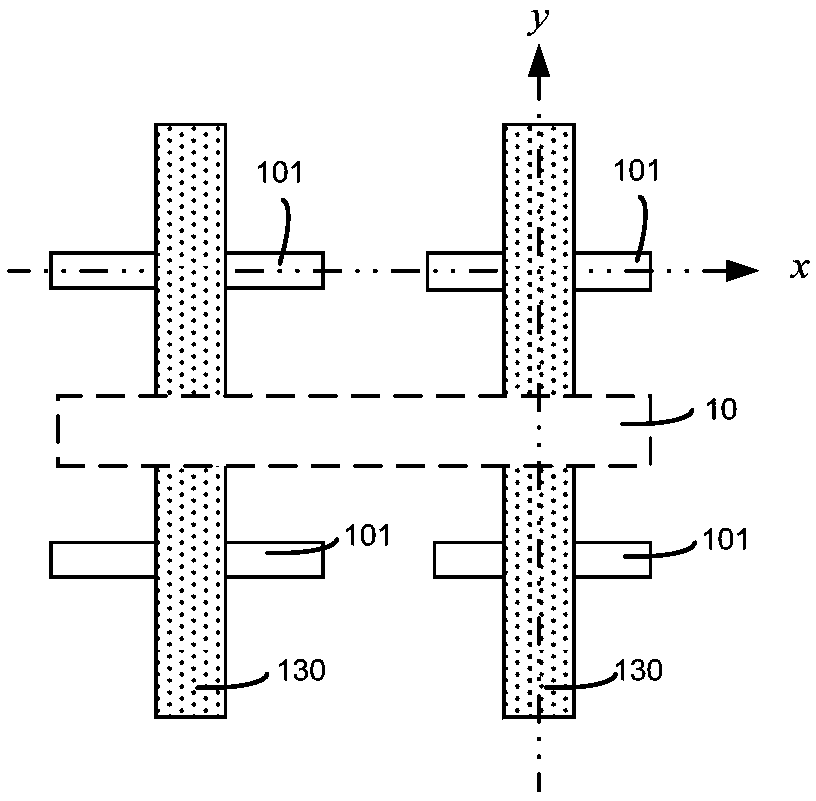

[0043] Please refer to figure 1 , forming a dummy gate 130 on part of the fin portion 101 .

[0044] figure 1 It is a top view of the structure of the embodiment of the present invention, the dummy gate 130 covers part of the fin 101 , and the area framed by the dotted line 10 is the area where the interlayer isolation structure will be formed later.

[0045] figure 1 x and y in represent two different directions of the structure of the embodiment of the present invention respectively. Each of the drawings below includes two parts a and b, and part a and part b are respectively along the figure 1 The structural schematic diagram obtained by the longitudinal section of the y-direction line and the x-direction line in the middle is applicable to different embodiments of the present invention.

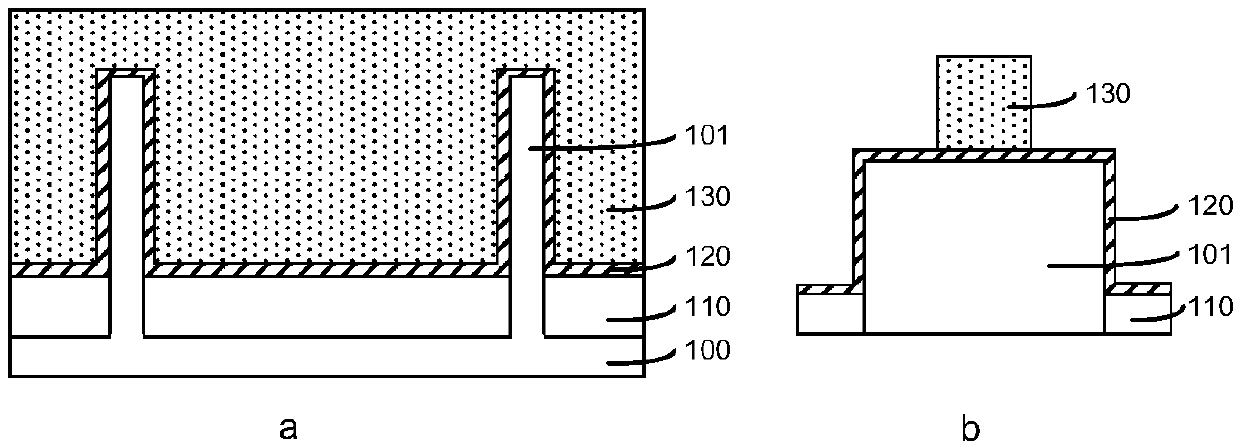

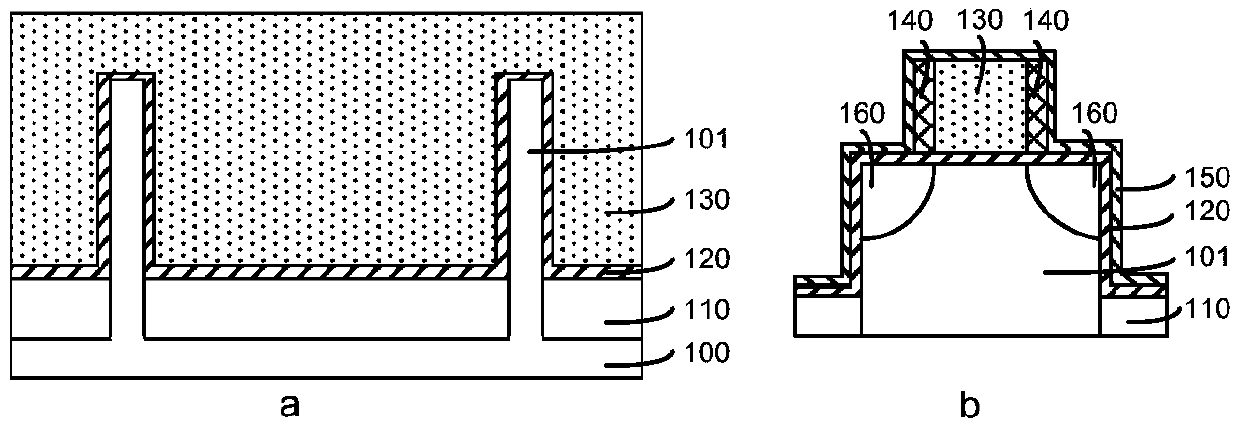

[0046] Please refer to figure 2 A fin portion 101 is formed above the semiconductor substrate 100 , and a dummy gate structure (not shown) is formed on part of the fin portion 101 ....

no. 2 example

[0106] The difference between the second embodiment and the first embodiment is: after removing the dummy gate structure, continue to etch part of the interlayer isolation structure, so that from the bottom of the first sidewall to the bottom of the second sidewall, the The distance between the point and the central axis of the longitudinal section of the fin adjacent to the second side wall decreases. Other process steps are consistent with the first embodiment.

[0107] From providing the semiconductor substrate 200 to removing the dummy gate structure, the process steps of the embodiment of the present invention are consistent with those of the first embodiment, and will not be repeated here.

[0108] Please refer to Figure 10 After the dummy gate structure is removed, a part of the interlayer isolation structure 271 is etched.

[0109] In order to further increase the distance between the interlayer isolation structure 271 and the fin 201 by etching part of the side sur...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness dimension | aaaaa | aaaaa |

| Thickness dimension | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More