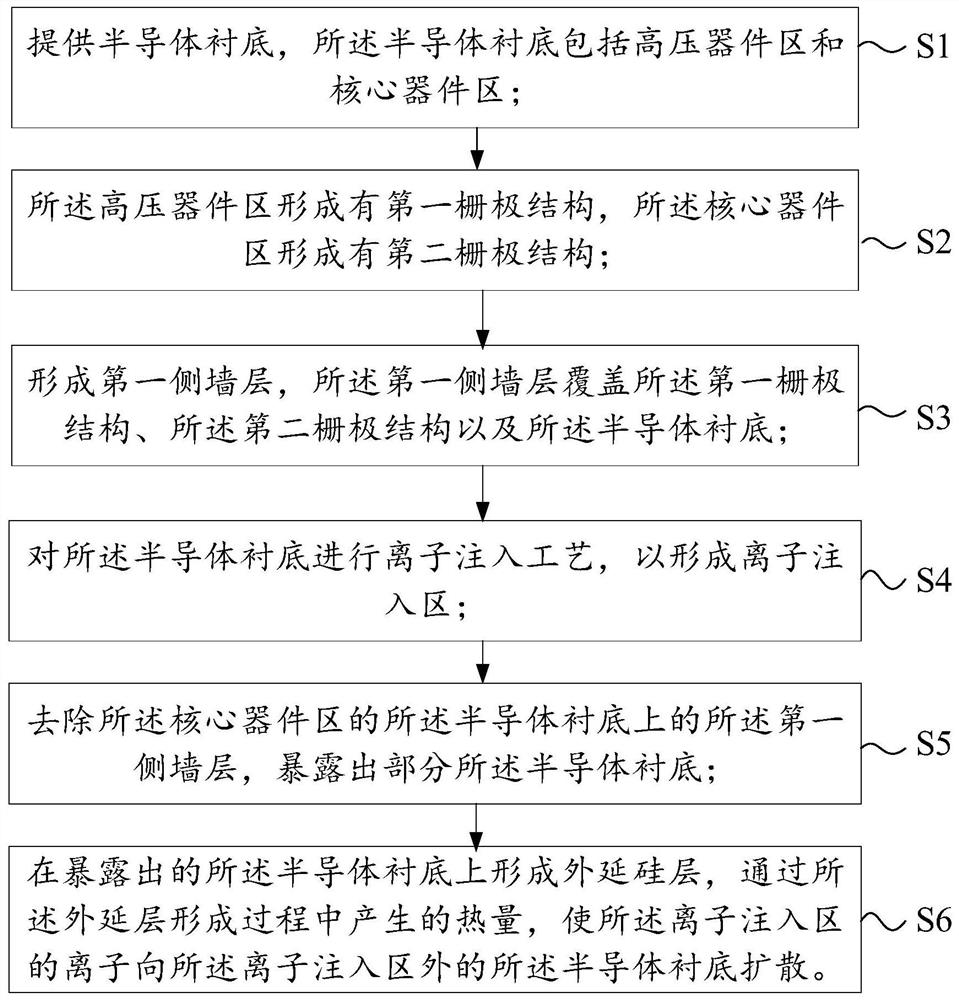

MOS device manufacturing method

A technology of MOS devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems that the effect cannot reach the expected effect and the requirements of the process cannot be met, so as to save processing time and improve performance , the effect of suppressing the hot carrier injection effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Step S2: the high-voltage device region is formed with a first gate structure, and the core device region is formed with a second gate

[0034] Step S5: removing the first spacer layer on the semiconductor substrate in the core device region, exposing the portion

[0035] Step S6: forming an epitaxial silicon layer on the exposed semiconductor substrate, through the epitaxial layer forming process

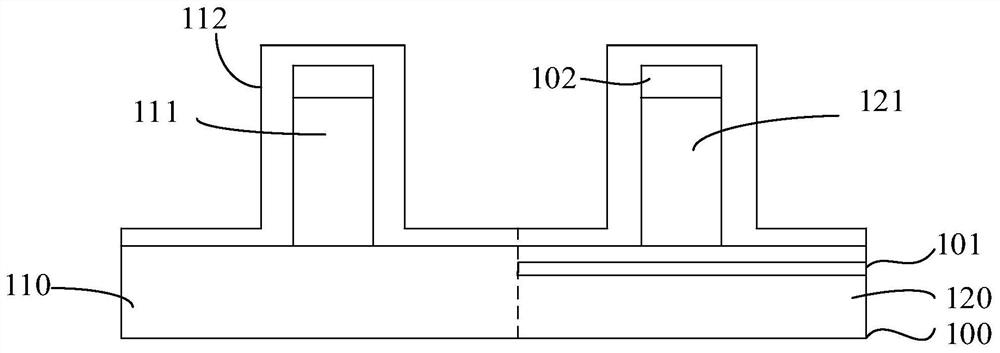

[0036] Please refer to FIG. 2, which is a schematic structural diagram of each step in a method for manufacturing a MOS device according to an embodiment of the present invention. exist

[0037] In step S3, the first spacer layer 112 covers the hard mask layer 102. can be formed by deposition

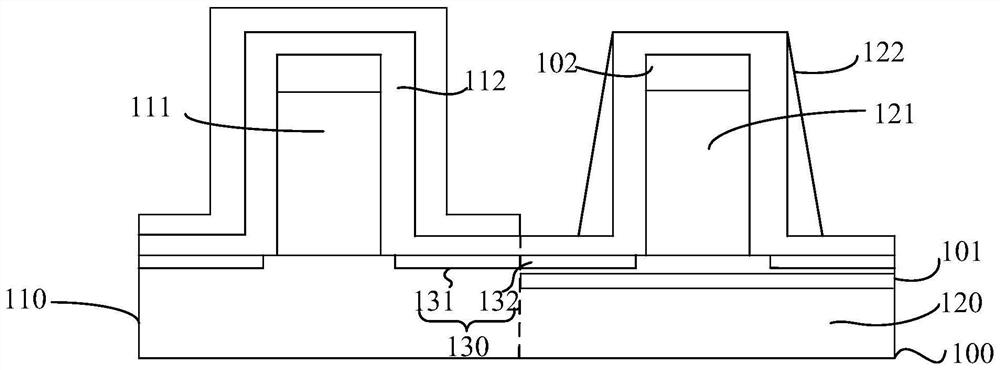

[0038] Please refer to FIG. 3. In step S4, an ion implantation process is performed on the semiconductor substrate to form an ion implantation process.

[0039] In an embodiment of the present application, the method for manufacturing the MOS device further includes, when forming the ion...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More