Wafer level packaging method and packaging structure

A technology of wafer-level packaging and packaging methods, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., to achieve the effect of simplifying the packaging structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

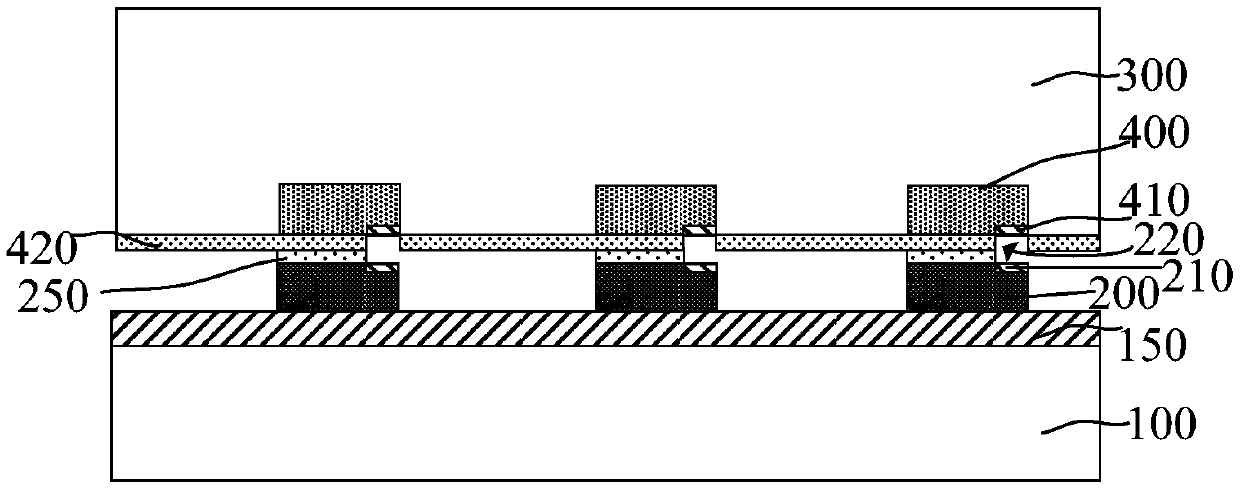

[0031] It can be seen from the background technology that the process of the packaging structure in the prior art is relatively complicated. The reason for the analysis is that in the prior art, after the bare chip to be integrated is bonded to the wafer, a first connection to be electrically connected to the bare chip needs to be formed. structure, the second connection structure electrically connected to the chips in the wafer, and the interconnection structure electrically connected to the first connection structure and the second connection structure, the process is relatively complicated.

[0032] In addition, before the bare chip is bonded to the wafer, an injection molding process is used to form the injection molding layer fixing the bare chip, and the injection molding layer is removed or partially removed after the bare chip is bonded to the wafer, and the steps are cumbersome.

[0033] In order to solve the technical problem, the present invention provides a wafer le...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More