SRAM controller and control method

A control method and controller technology, applied in the SOC field, can solve problems such as bottlenecks, occupancy, and command bandwidth occupation, and achieve low-latency effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

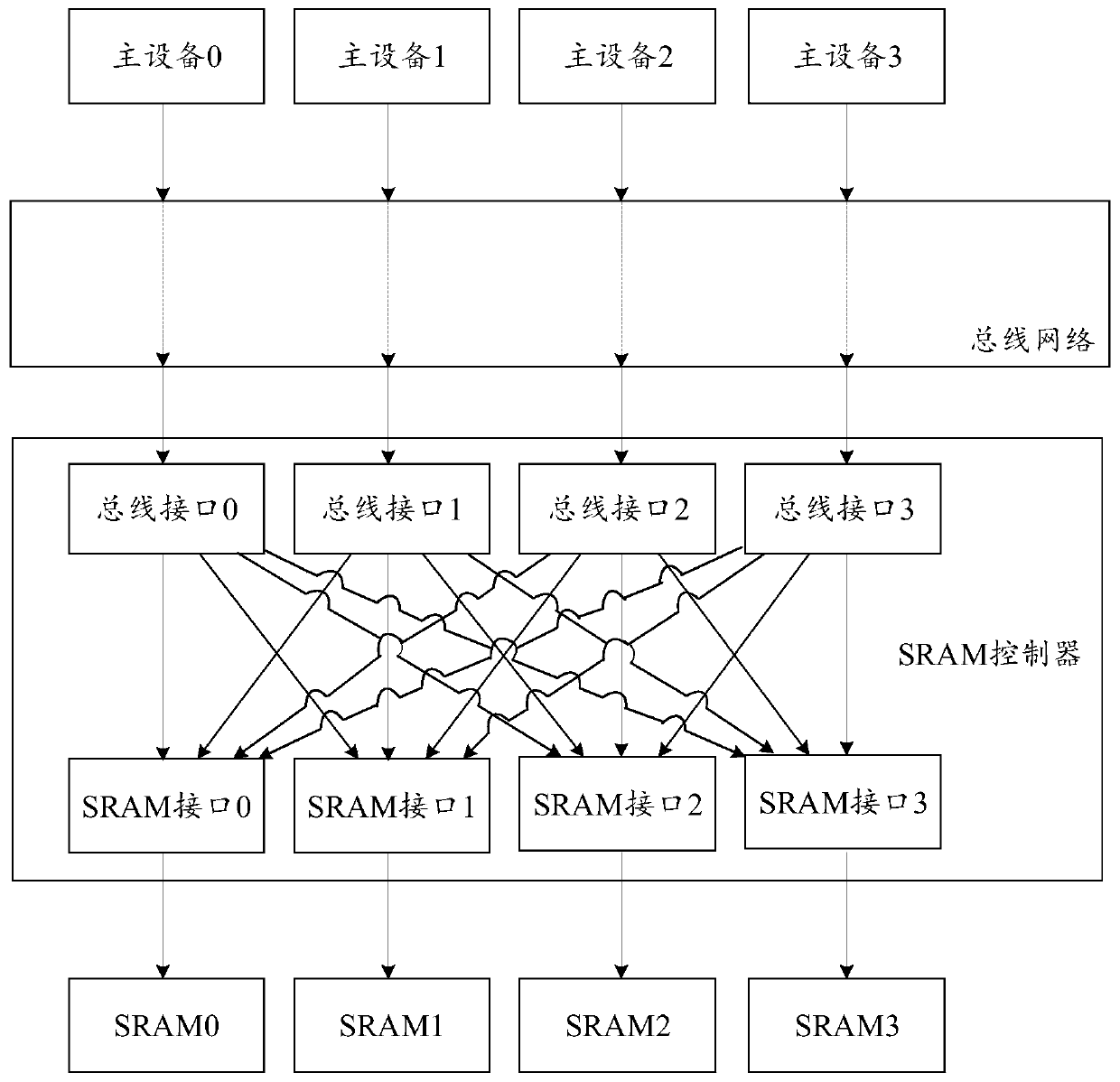

[0053] In example 1, in the same clock cycle, each master device does not conflict with the access to SRAM, master device 0 accesses SRAM0, master device 1 accesses SRAM 1, master device 2 accesses SRAM 2, and master device 3 accesses SRAM 3.

[0054]The SRAM access request sent by the master device 0 reaches the bus interface 0 after passing through the bus network. The bus interface 0 sends the SRAM access request to the SRAM interface 0 according to the address specified in the SRAM access request, and the SRAM interface 0 accesses the SRAM 0 according to the SRAM access request. . In a similar manner, bus interface 1 forwards the SRAM access request of master 1 to SRAM interface 1, bus interface 2 forwards the SRAM access request of master 2 to SRAM interface 2, and bus interface 3 forwards the SRAM access request of master 3 Forwarded to SRAM interface 3. SRAM0, SRAM1, SRAM2 and SRAM3 transmit data at the same time, so that the bandwidth of SRAM is fully utilized.

example 2

[0056] In Example 2, in the same clock cycle, two master devices conflict with SRAM access. Both master 0 and master 1 access SRAM 0, master 2 accesses SRAM 2, and master 3 accesses SRAM3.

[0057] The SRAM access request sent by the master device 0 reaches the bus interface 0 through the bus network, and the bus interface 0 sends the SRAM access request to the SRAM interface 0 according to the address specified in the SRAM access request. The SRAM access request sent by the master device 1 reaches the bus interface 1 through the bus network, and the bus interface 1 sends the SRAM access request to the SRAM interface 0 according to the address specified in the SRAM access request. In response to the above two SRAM access requests, SRAM interface 0 selects a SRAM access request (eg, the SRAM access request from bus interface 0 ) within one clock cycle, and accesses SRAM 0 according to the selected SRAM access request. In the next clock cycle immediately adjacent to the above c...

example 3

[0060] In Example 3, in the same clock cycle, three master devices conflict with SRAM access. Master 0, Master 1, and Master 2 all access SRAM 0, and Master 3 accesses SRAM 3.

[0061] The SRAM access request sent by the master device 0 reaches the bus interface 0 through the bus network, and the bus interface 0 sends the SRAM access request to the SRAM interface 0 according to the address specified in the SRAM access request. The SRAM access request sent by the master device 1 reaches the bus interface 1 through the bus network, and the bus interface 1 sends the SRAM access request to the SRAM interface 0 according to the address specified in the SRAM access request. The SRAM access request sent by the master device 2 reaches the bus interface 2 through the bus network, and the bus interface 2 sends the SRAM access request to the SRAM interface 0 according to the address specified in the SRAM access request. SRAM interface 0 selects one SRAM access request (eg, the SRAM acce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More