Multiplication unit circuit utilizing threshold voltage characteristics and multiplier

A threshold voltage, multiplication unit technology, applied in the direction of logic circuits, electrical components, logic circuits with logic functions, etc., can solve the problems of too many transistors, attacks, and vulnerability to reverse engineering and DPA attacks.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

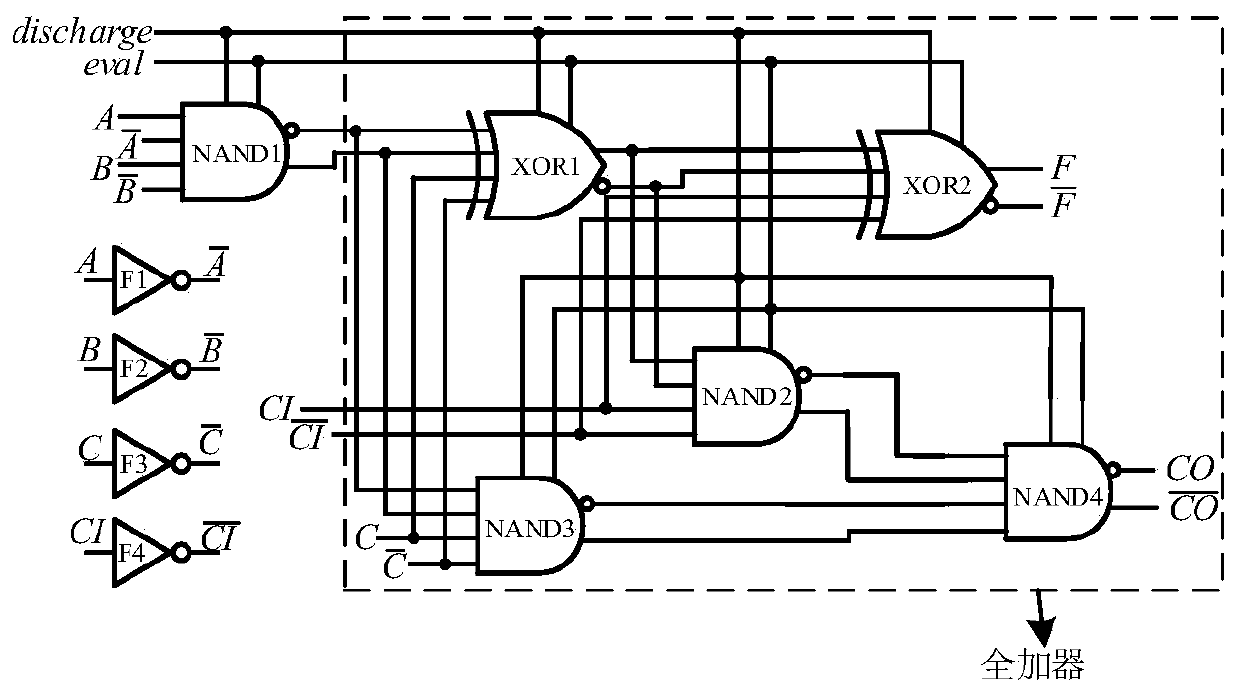

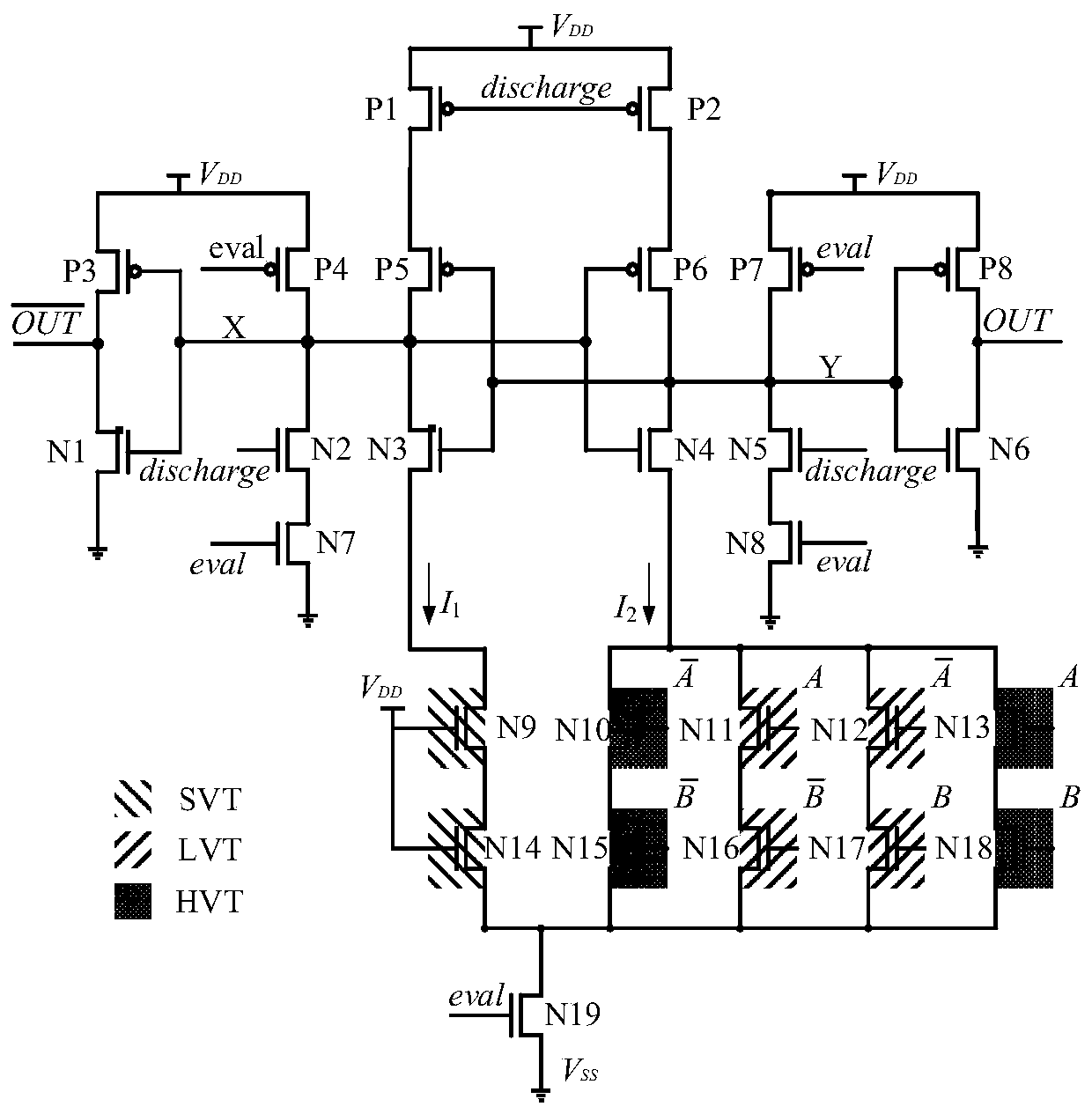

[0021] Embodiment: as shown in Figure 1, figure 2 with image 3As shown, a multiplication unit circuit utilizing threshold voltage characteristics includes a first inverter F1, a second inverter F2, a third inverter F3, a fourth inverter F4, four two-input inverters with the same structure A NAND gate and two two-input XOR gates with the same structure, each two-input NOT gate has a first input terminal, a first inverting input terminal, a second input terminal, a second inverting input terminal, a first control terminal, a second control terminal, an output terminal and an inverting output terminal, and each two-input XOR gate has a first input terminal, a first inverting input terminal, a second input terminal, a second inverting input terminal, a first Control terminal, second control terminal, output terminal and inverting output terminal; each two-input XOR gate respectively includes a first PMOS transistor P1, a second PMOS transistor P2, a third PMOS transistor P3, a f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More