Semiconductor structure capable of reducing switching loss and manufacturing method

A switching loss and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of excessive gate charge and large device switching loss, and achieve the effect of reducing switching loss and reducing manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

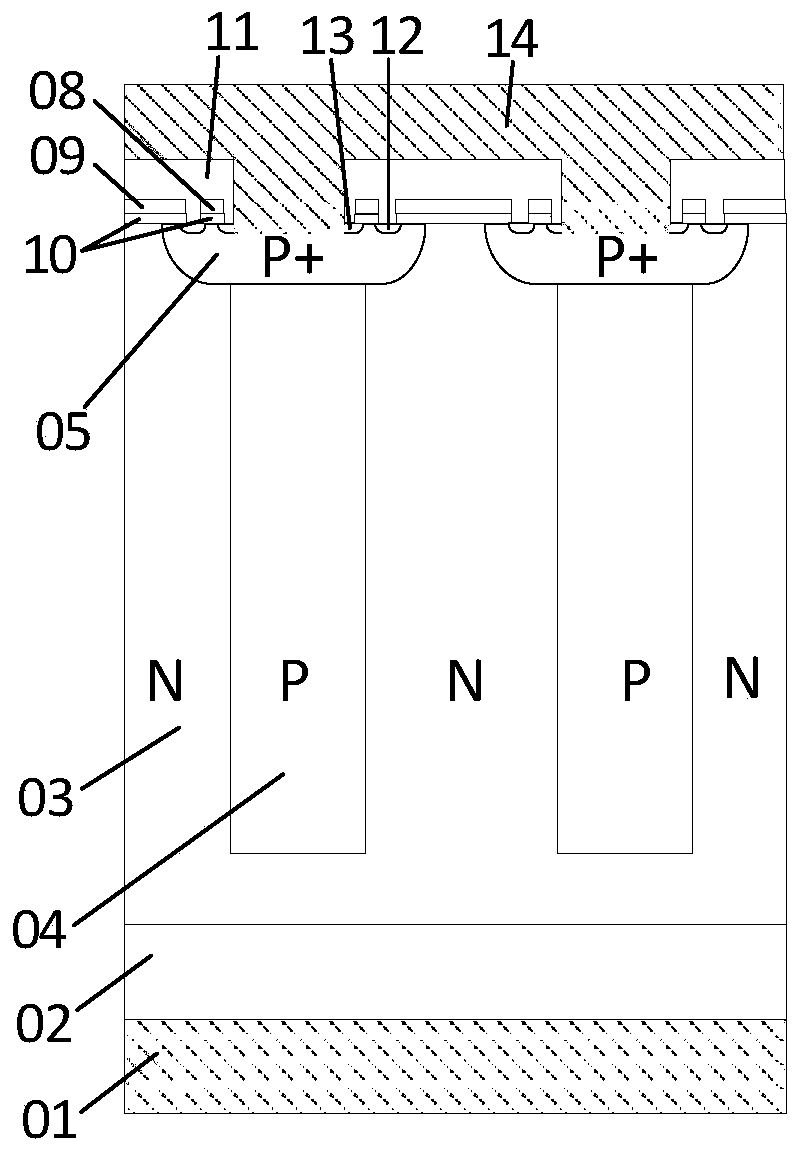

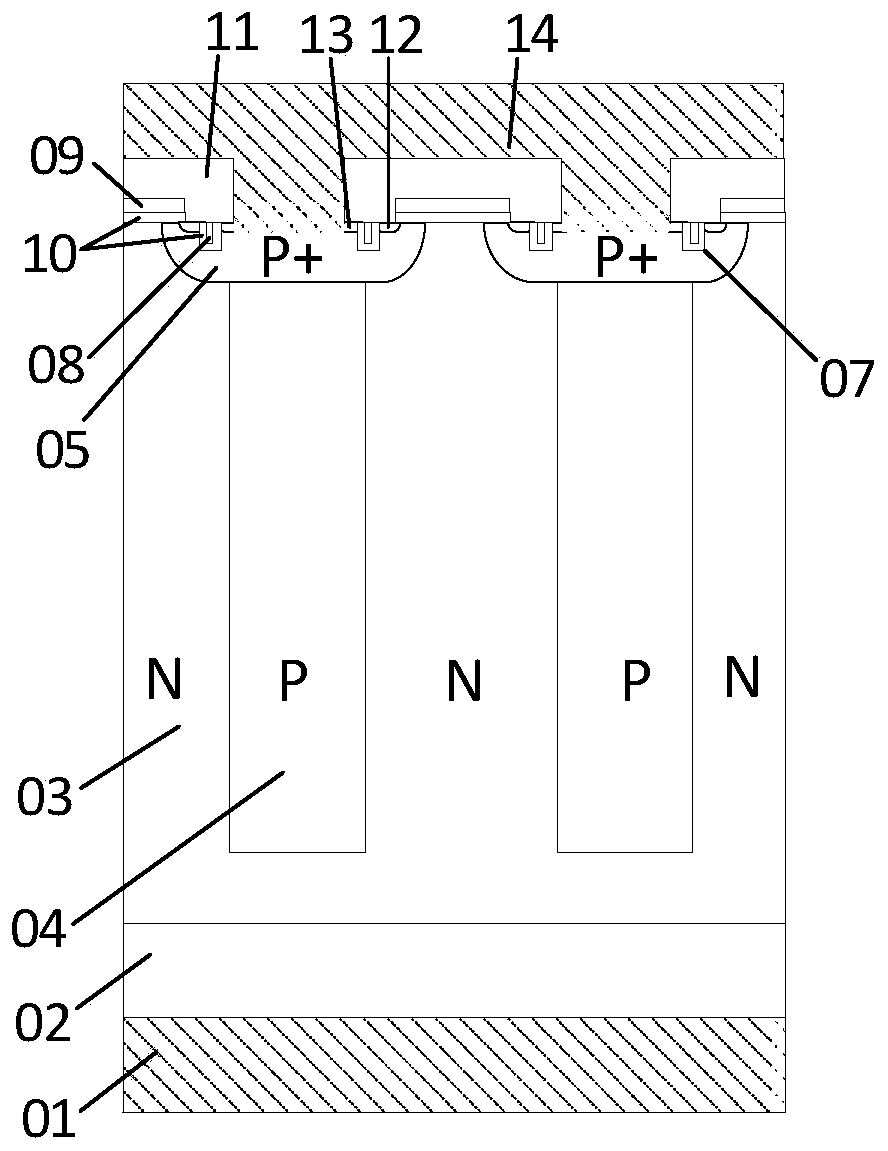

[0063] refer to figure 1 , is a semiconductor structure for reducing switching loss, taking an N-type planar super-junction power semiconductor device as an example, including a drain 01, an N-type substrate 02, and an N-type epitaxial layer 03 that are sequentially stacked from bottom to top; The material of the drain 01 is preferably metal, and the material of the N-type substrate 02 may be silicon.

[0064] A plurality of P-type columns 04 are arranged in the N-type epitaxial layer 03, and the plurality of P-type columns 04 are distributed at intervals, and each of the P-type columns 04 faces from the upper surface of the N-type epitaxial layer 03 to Extend down.

[0065] The upper end of the P-type column 04 forms a P-type body region 05, and the P-type body region 05 is heavily doped to form an N-type first source region 13, and the P-type body regions on both sides of the N-type first source region 13 The N-type second source region 12 is formed by heavy doping in the...

Embodiment 2

[0072] refer to figure 1 , is a semiconductor structure for reducing switching loss, taking an N-type planar super-junction power semiconductor device as an example, including a drain 01, an N-type substrate 02, and an N-type epitaxial layer 03 that are sequentially stacked from bottom to top; The material of the drain 01 is preferably metal, and the material of the N-type substrate 02 may be silicon.

[0073] A plurality of P-type columns 04 are arranged in the N-type epitaxial layer 03, and the plurality of P-type columns 04 are distributed at intervals, and each of the P-type columns 04 faces from the upper surface of the N-type epitaxial layer 03 to Extend down.

[0074] The upper end of the P-type column 04 forms a P-type body region 05, and the P-type body region 05 is heavily doped to form an N-type first source region 13, and the P-type body regions on both sides of the N-type first source region 13 The N-type second source region 12 is formed by heavy doping in the...

Embodiment 3

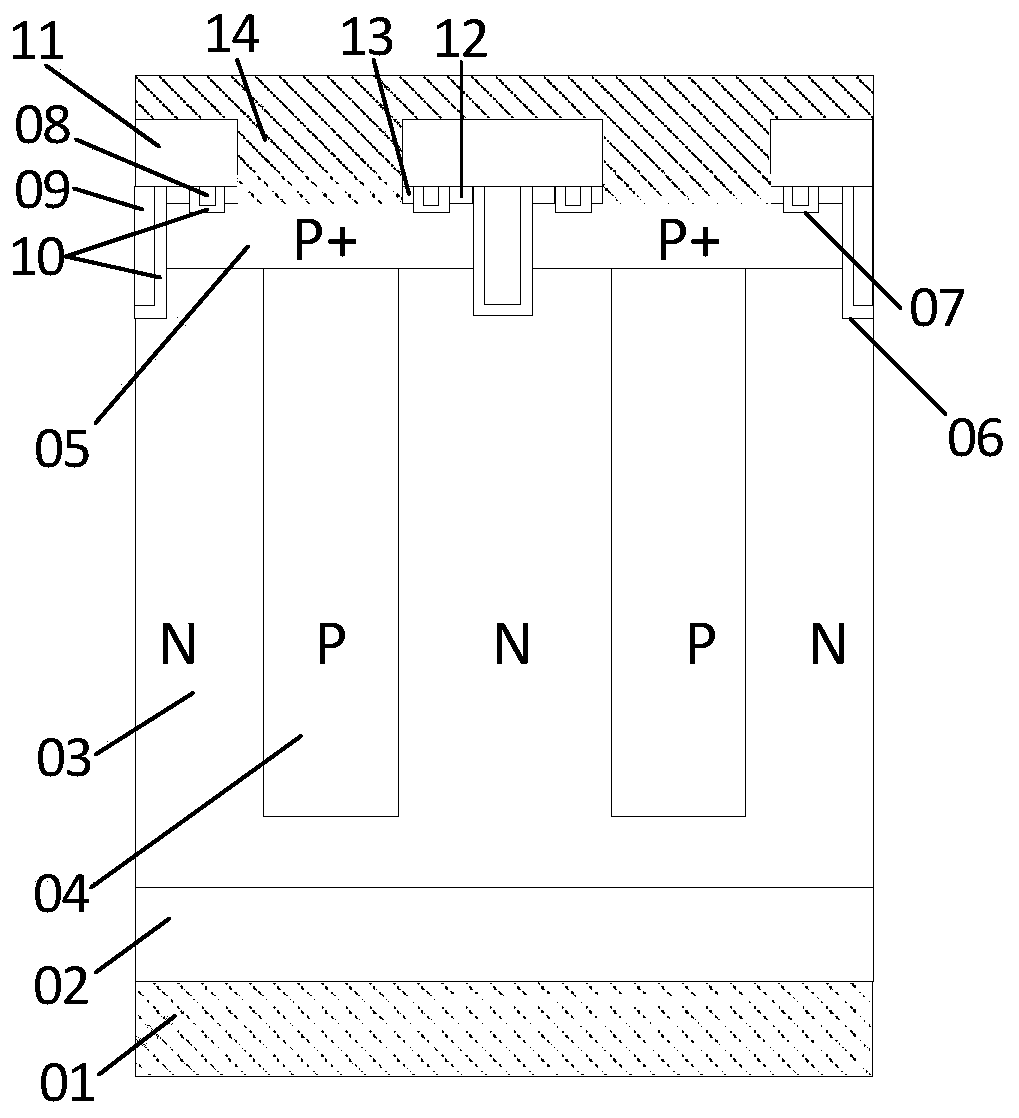

[0081] refer to image 3 , is a semiconductor structure for reducing switching loss, taking an N-type planar super-junction power semiconductor device as an example, including a drain 01, an N-type substrate 02, and an N-type epitaxial layer 03 that are sequentially stacked from bottom to top; The material of the drain 01 is preferably metal, and the material of the N-type substrate 02 may be silicon.

[0082] A plurality of P-type columns 04 are arranged in the N-type epitaxial layer 03, and the plurality of P-type columns 04 are distributed at intervals, and each of the P-type columns 04 faces from the upper surface of the N-type epitaxial layer 03 to Extend down.

[0083] The upper end of the P-type column 04 forms a P-type body region 05, and the P-type body region 05 is heavily doped to form an N-type first source region 13, and the P-type body regions on both sides of the N-type first source region 13 The N-type second source region 12 is formed by heavy doping in the bo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More