A yolov3 network computing acceleration system based on fpga and its acceleration method

A network and computing module technology, which is applied to the FPGA-based Yolov3 network computing acceleration system and its acceleration field, can solve the problems of difficult deployment of embedded terminals, large amount of calculation, etc., to improve bandwidth, get rid of bandwidth restrictions, and efficiently reuse data Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

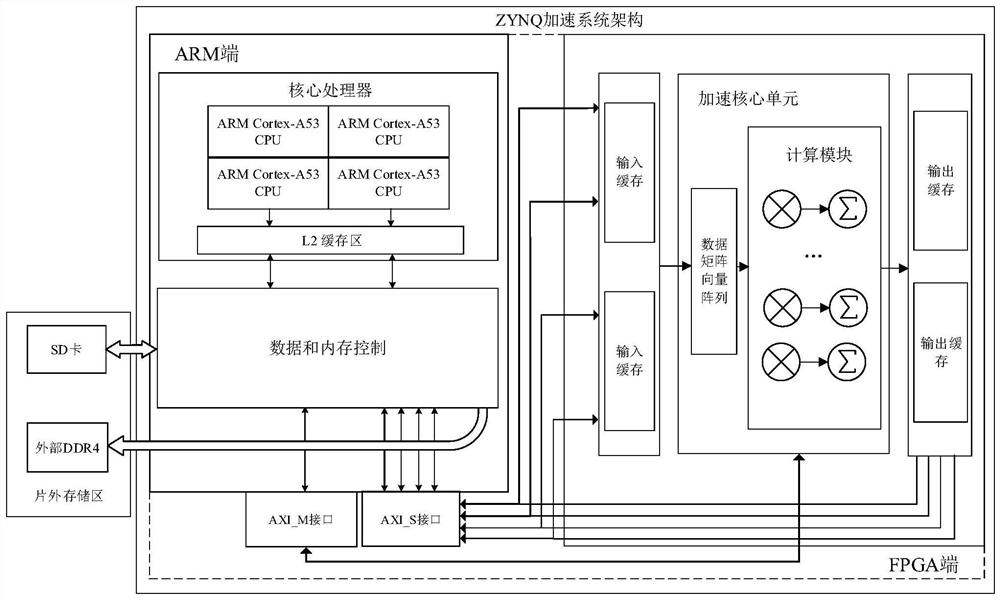

[0055] according to figure 1 As shown, a Yolov3 network computing acceleration system based on FPGA, the system includes ARM and FPGA platform architecture, off-chip storage area, AXI_M interface and AXI_S interface, and the ARM platform architecture includes a core processor and a data and memory controller , the FPGA platform architecture includes an acceleration core unit, an input cache end and an output cache end;

[0056] The core processor includes an ARM Cortex-A53CPU and an L2 cache area, the off-chip storage area includes an SD card and an external DDR4, and the acceleration core unit includes a data matrix vector array and a computing module;

[0057] The ARM Cortex-A53CPU is connected to the L2 cache area, the L2 cache area is connected to the data and the memory controller, the data and the memory controller are connected to the off-chip storage area, the data and the memory controller AXI_M interface and AXI_S interface, so The AXI_S interface is connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More