High-energy-efficiency full-dynamic comparator applied to SAR ADC

A comparator, full dynamic technology, applied in instruments, signal transmission systems, electrical components, etc., to reduce equivalent noise, reduce clock load, and improve pre-amplification gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be further described below in conjunction with the accompanying drawings.

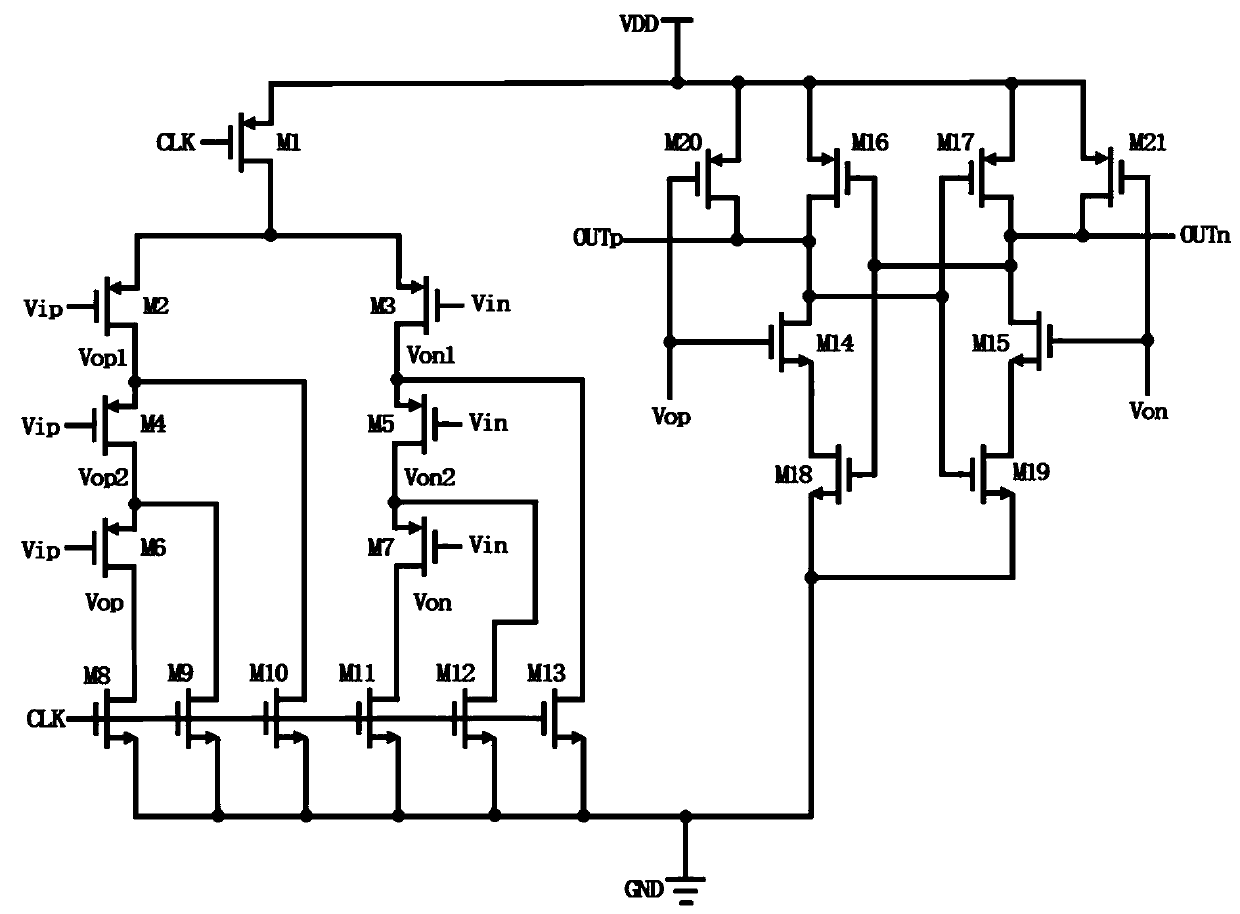

[0024] Such as figure 1 It is a cascaded input comparator, mainly including a pre-amplification circuit and a latch circuit. The pre-amplification circuit includes tail current tube M1, differential input tubes M2, M3, M4, M5, M6 and M7, reset tubes M8, M9, M10, M11, M12 and M13, among which M1, M2, M3, M4, M5, M6 and M7 are PMOS tubes, and M8, M9, M10, M11, M12 and M13 are NMOS tubes. The latch circuit includes M14, M15, M16, M17, M18, M19, M20 and M21 which form two NAND gates, wherein M16, M17, M20 and M21 are PMOS transistors, and M14, M15, M18 and M19 are NMOS transistors.

[0025] The specific structure of the cascaded input comparator is:

[0026] The gate of M1 is connected to the clock signal CLK; the source of M1 is connected to VDD; the drain of M1 is connected to the source of M2 and the source of M3 respectively; the gate of M2 is connected to the diffe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More