Inline ecc function for system-on-chip

An on-chip network and transaction technology, which is applied in the field of online error correction code function, can solve the problems that the bus structure is not suitable for system-on-chip integrated circuits, high cost, transaction blocking, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Various features are described below with reference to the accompanying drawings. It should be noted that the drawings may or may not be drawn to scale, and that elements of like structure or function are represented by like reference numerals throughout the drawings. It should be noted that the drawings are only intended to facilitate the description of the features. They are not intended as an exhaustive description of the claimed invention or as a limitation on the scope of the claimed invention. In addition, the illustrated examples do not necessarily have all the aspects or advantages shown. An aspect or advantage described in connection with a particular example is not necessarily limited to that example and can be practiced in any other example even if not so illustrated or explicitly described.

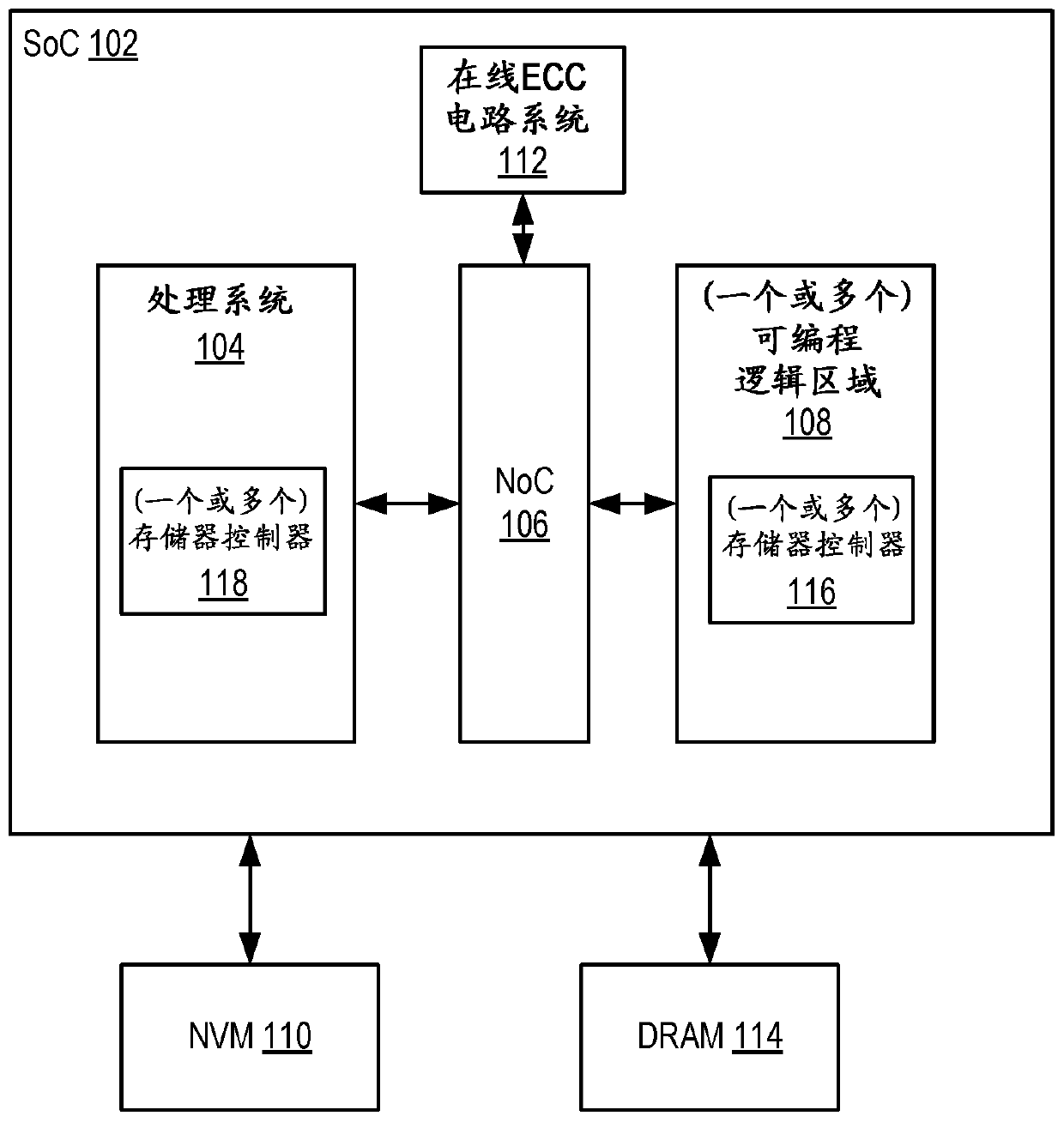

[0020] figure 1 is a block diagram depicting a system on chip (SoC) 102 according to one example. SoC 102 is an integrated circuit (IC) that includes a processing s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More