Wafer-level chip structure, multi-chip stacking interconnection structure and preparation method

A wafer-level chip and chip structure technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, semiconductor devices, etc., can solve problems such as the impact of signal transmission quality, improve signal distortion, and improve signal distortion , Improve the effect of bridging problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

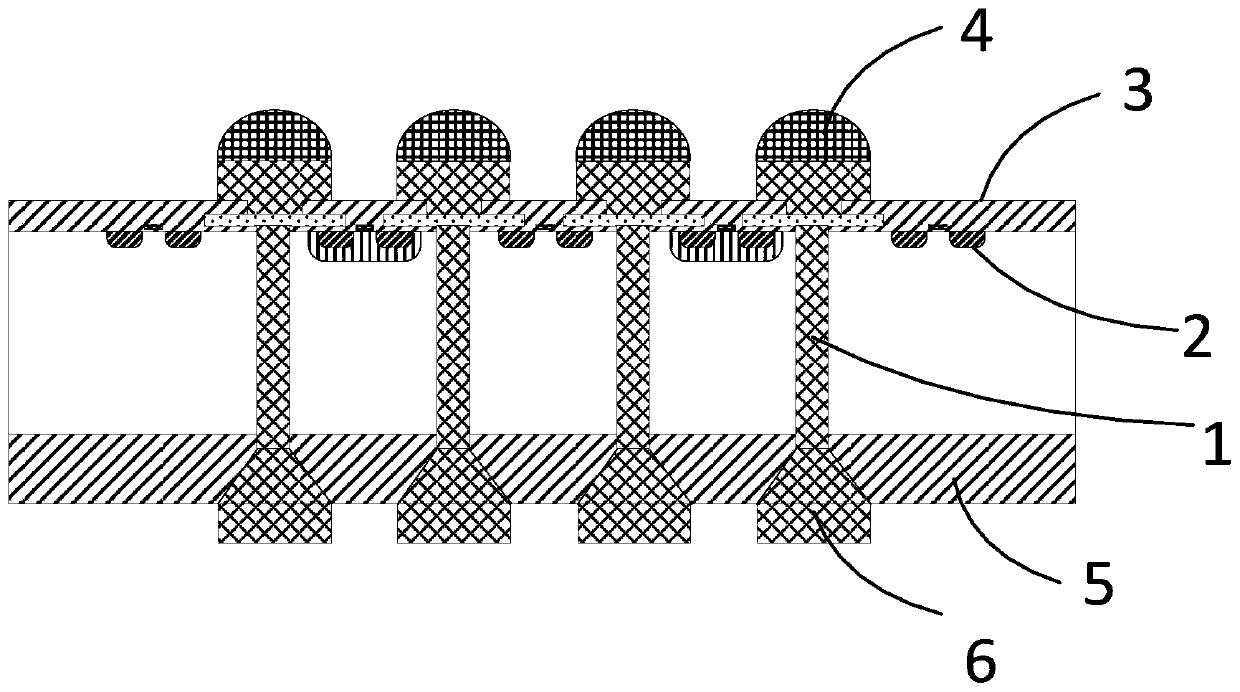

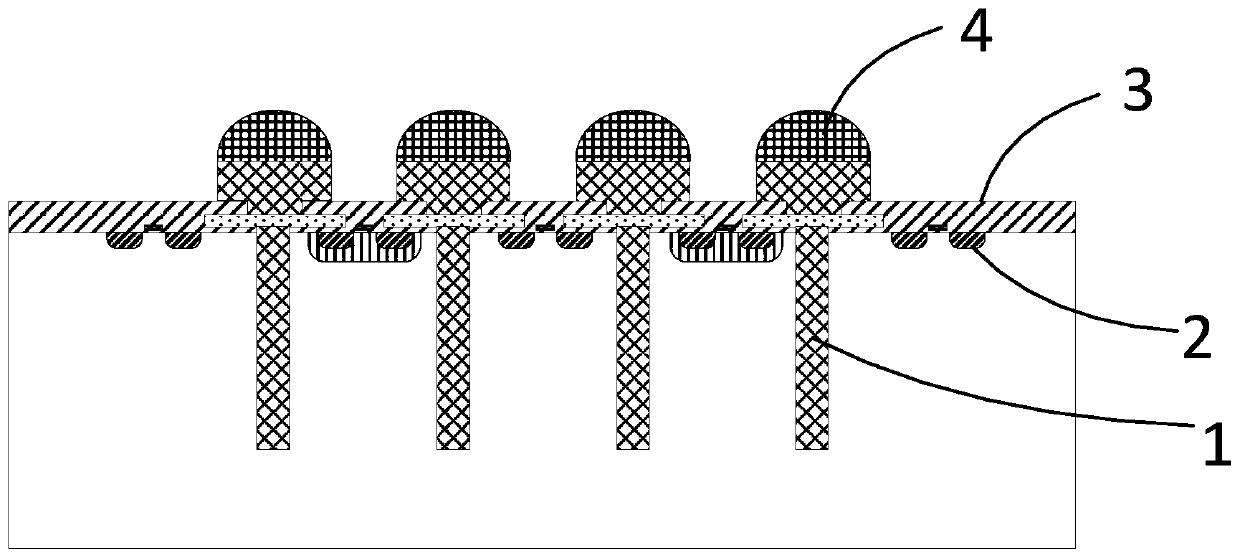

[0052] Embodiments of the present invention provide a wafer-level chip structure, such as figure 1 As shown, it includes: through-silicon via 1 through the wafer, its first surface includes: active region 2, multi-layer redistribution line layer 3 and bump 4, its second surface includes: insulating dielectric layer 5, and A frustum-conical transition structure 6 connected by through-silicon vias.

[0053] In the embodiment of the present invention, the material filled in the TSV 1 can be copper, the bump 4 can be a solder ball, the opening diameter of one end of the frustum-conical transition structure 6 is determined according to the size of the connected TSV, and the opening diameter of the other end is determined according to Bonding bump size determination. The frustoconical transition structure is based on SF 6 / CF 4 / CHF 3 / O 2 / Ar and other process gas inductively coupled plasma etching process, the height is about 2 ~ 6um (SiO 2 Deposition thickness and film stre...

Embodiment 2

[0062] An embodiment of the present invention provides a wafer-level multi-chip stacking interconnection structure, such as Figure 7 As shown, it includes: a chip bonder 7, a substrate 8 and a lead terminal 9, the chip bonder 7 is transferred to the first surface of the substrate 8, and the lead terminal 9 is formed on the second surface of the substrate, wherein,

[0063] The chip bonding body 7 includes a plurality of single wafer-level chips arranged in a stack, and the multiple single wafer-level chips are directly connected through a bonding layer. The single wafer-level chips include: a first chip structure 11, A second chip structure 12 and at least one third chip structure 13, the first chip structure 11 and the second chip structure 12 are respectively located at both ends of the chip bonding body 7, the at least one third chip structure 13, Located between the first chip structure 11 and the second chip structure 12; the third chip structure 13 is the wafer-level ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More