Array substrate, preparation method and display device

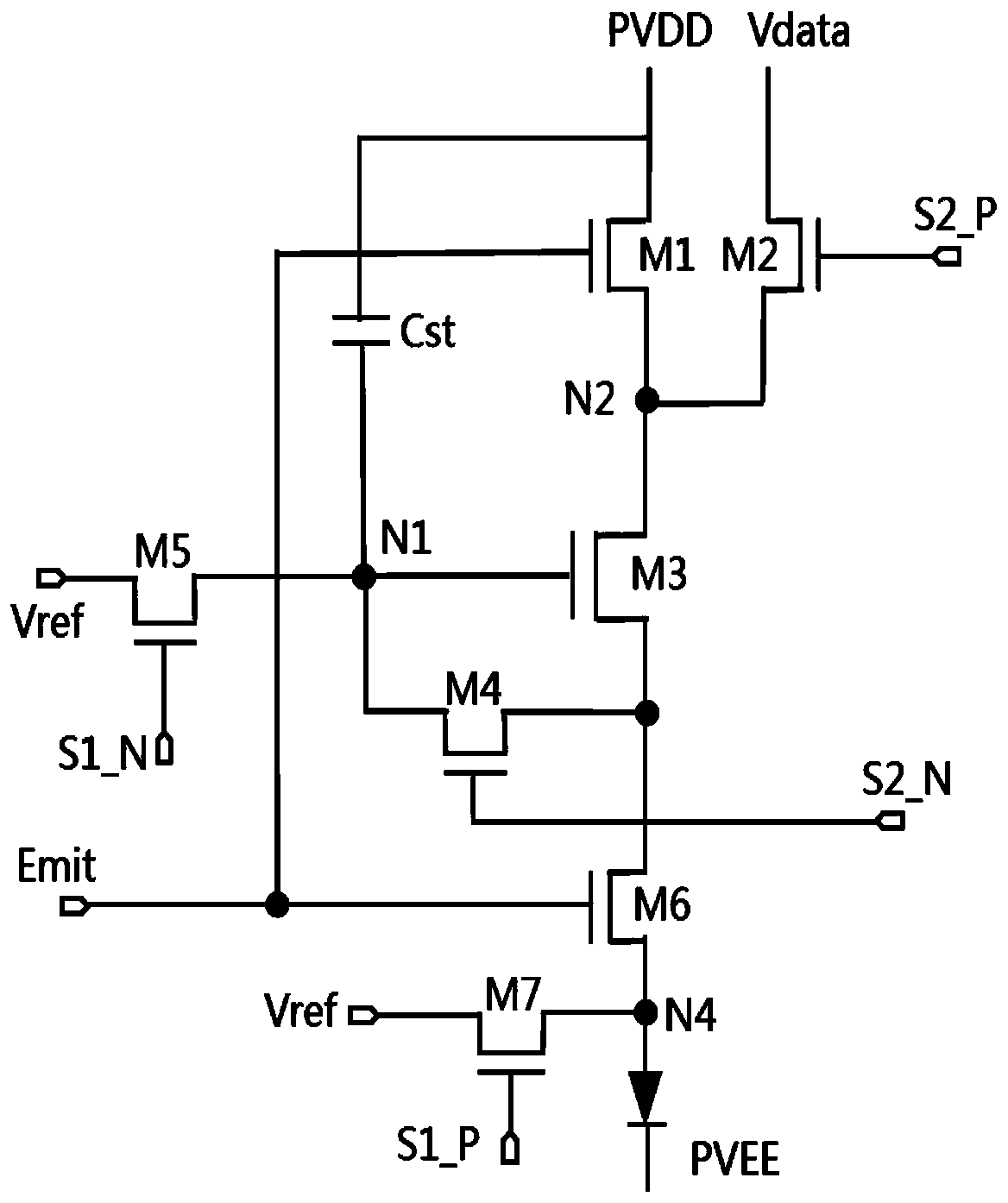

An array substrate and the same technology are applied in the fields of array substrates, preparation methods and display devices, and can solve the problems of large overall thickness of pixel circuits, increased process difficulty, large depth of etching holes of polysilicon transistors, etc., so as to reduce leakage current and reduce Process difficulty, the effect of reducing the overall thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0041] In addition, the present invention also provides a method for preparing the above-mentioned array substrate, including:

[0042] providing a substrate;

[0043] At least one first polysilicon island and at least one second polysilicon island are formed on one side of the substrate, and grooves are opened on the first polysilicon island;

[0044] blocking the second polysilicon island, and performing ion implantation on the first polysilicon island to form a P-type semiconductor;

[0045] blocking the channels of the second polysilicon island and the first polysilicon island, and performing ion implantation on the source and drain electrodes of the first polysilicon island to form an N-type semiconductor;

[0046] Metal oxide is filled in the groove of the first polysilicon island.

[0047] Through the above steps, the first thin film transistor whose active layer includes polysilicon and metal oxide arranged in the same layer can be prepared, so that in the pixel circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More