Configuration system and method of field programmable logic gate array

A technology for programming logic and configuration system, which is applied in the field of field programmable logic gate array to save board area, reduce development difficulty and save circuit overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

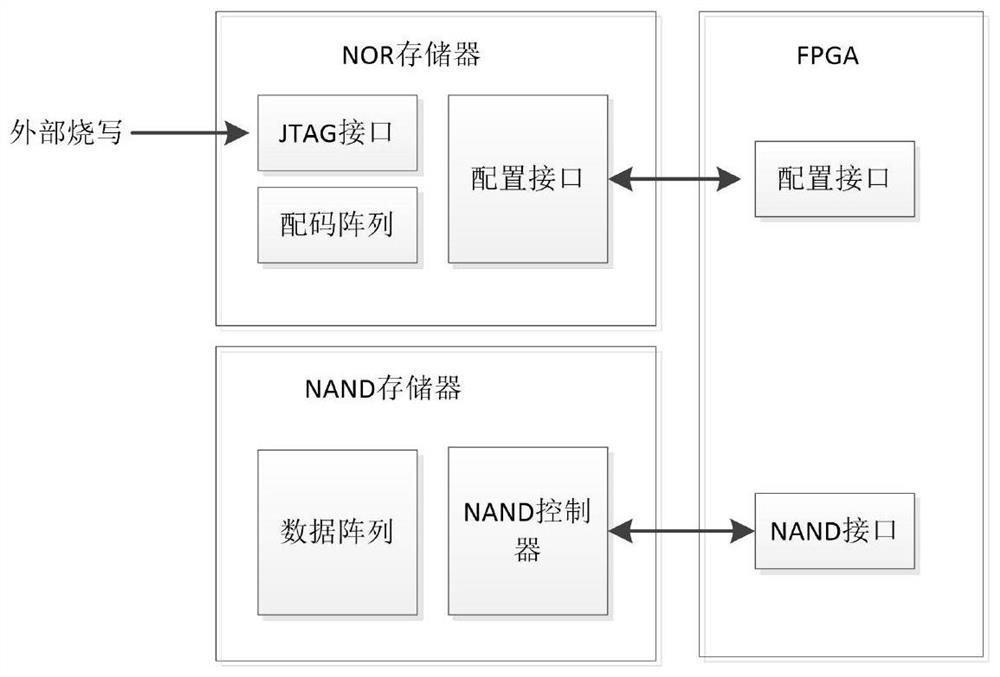

[0050] refer to figure 2 , figure 2 It is a structural schematic diagram of a field programmable logic gate array configuration system in an embodiment of the present invention.

[0051] In this embodiment, the field programmable logic gate array configuration system includes: NAND memory and FPGA.

[0052] The NAND memory includes: a data array, a coding array, a first configuration interface and a NAND controller, the FPGA includes: a second configuration interface and a NAND interface, the second configuration interface is connected to the first configuration interface, The NAND interface is connected with the NAND controller.

[0053] The matching array is used to store multiple versions of matching files.

[0054] The first configuration interface is used to read the first configuration code from the configuration array after power-on, and send the first configuration code to the second configuration interface, so that the FPGA to configure.

[0055] In this embodime...

no. 2 example

[0072] Based on the same inventive idea, such as image 3 As shown, the embodiment of the present invention also provides a configuration method of a field programmable logic gate array, the method is based on a configuration system of a field programmable logic gate array, and the system includes: a NAND memory and an FPGA; wherein the NAND memory includes: A data array, a coding array, a first configuration interface and a NAND controller, the FPGA includes: a second configuration interface and a NAND interface, the second configuration interface is connected to the first configuration interface, and the NAND interface is connected to the The NAND controller connection described above. The methods include:

[0073] Step S10: After the NAND memory is powered on, it reads a first configuration code from the configuration array through the first configuration interface, and sends the first configuration code to the second configuration code of the FPGA. The second is a config...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More