Dual-core system clock synchronization method and device based on timestamp marking circuit

A technology for marking circuits and system clocks, applied in time-division multiplexing systems, electrical components, multiplexing communications, etc., can solve the problems of not being applicable to dual-core dual systems, delay jitter, and clock synchronization accuracy being greatly affected , to achieve the effect of solving clock synchronization and reducing errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

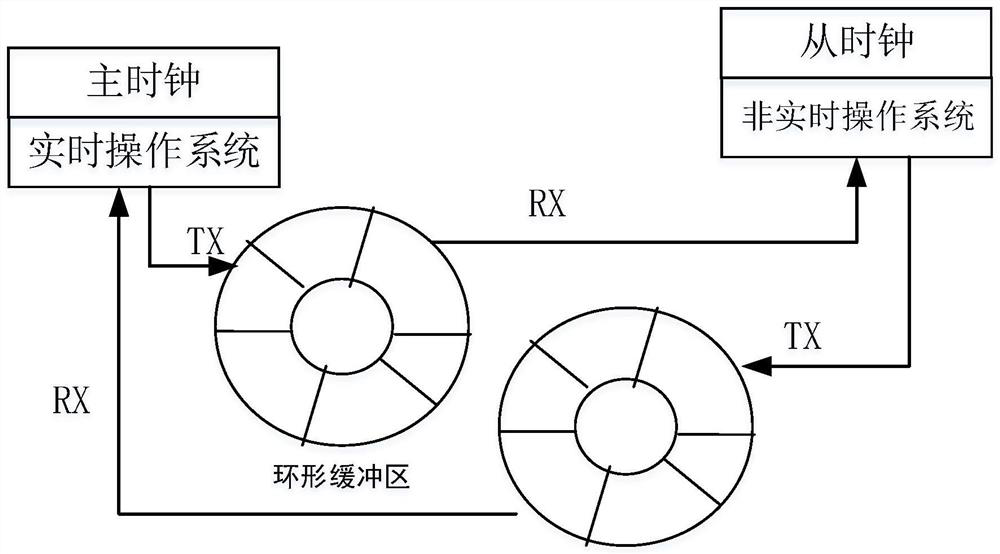

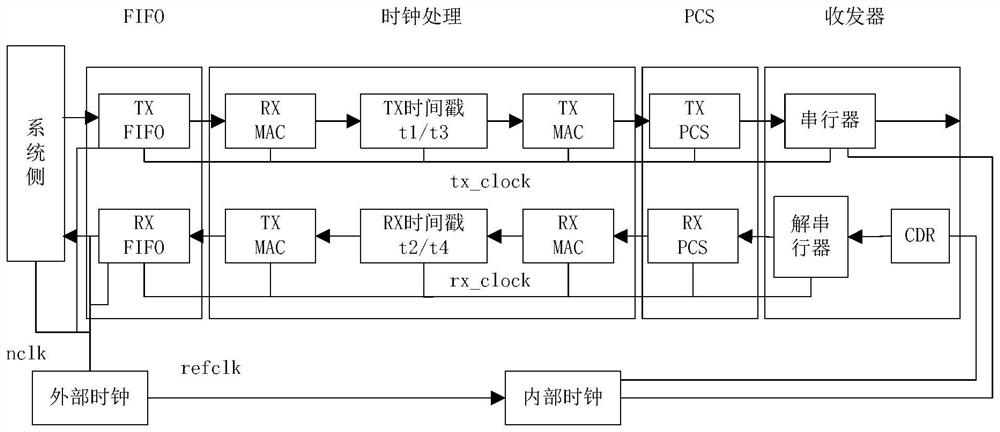

[0030] Such as figure 1 As shown, it is a schematic diagram of a dual-core system clock synchronization method based on a timestamp marking circuit disclosed in Embodiment 1 of the present invention, figure 2 A block diagram of the design implementation for obtaining timestamps inside the physical layer, figure 1 Among them, Ring buffer represents a ring buffer. Embodiment 1 of the present invention provides a dual-core system clock synchronization method based on a timestamp marking circuit. The method process is described in detail below:

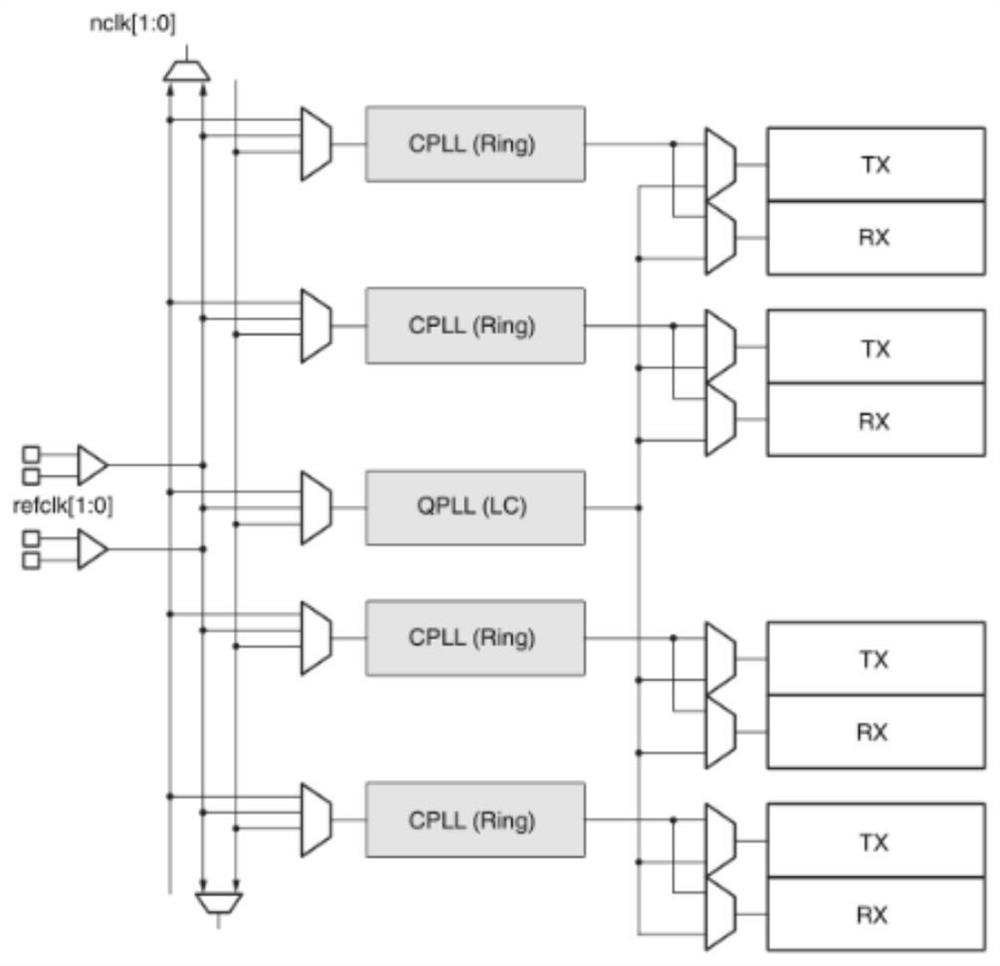

[0031] The clock synchronization method is applied to AIRT-ROS real-time systems and non-real-time systems, and the time stamp marking circuit includes a local clock unit, a frequency compensation register, a synchronization message / and a delay request detection circuit, and a synchronization message / delay request time Latches, the first base address data register, the second base address data register and the time event status register...

Embodiment 2

[0052] Corresponding to Embodiment 1 of the present invention, Embodiment 2 of the present invention also provides a dual-core system clock synchronization device based on a timestamp marking circuit, which is applied to an AIRT-ROS real-time system and a non-real-time system, and the timestamp-based marking circuit includes a local Clock unit, frequency compensation register, synchronous message / and delay request detection circuit, synchronous message / delay request time latch, first base address data register, second base address data register and time event status register, first CPU Write the frequency compensation value into the frequency compensation register through the bus interface, start the local clock unit as the local clock reference; write the address of the second base address data register into the first base address data register, and write the address of the second base address data register to the second base address data register Write the address of the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More