LDMOS transistor and preparation method thereof

A transistor and body technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as HCI failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

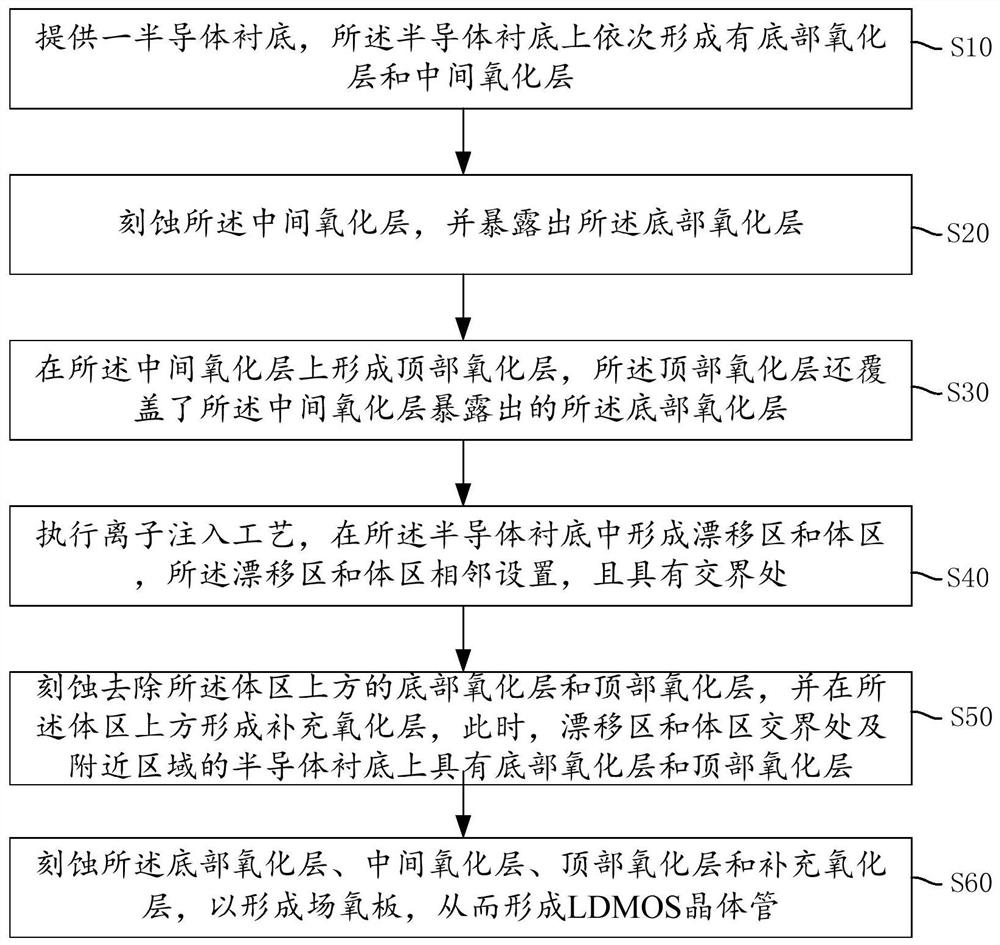

[0046] figure 2 is a schematic flow chart of a method for fabricating an LDMOS transistor in this embodiment. like figure 2 As shown, the preparation method of an LDMOS transistor provided in this embodiment includes the following steps:

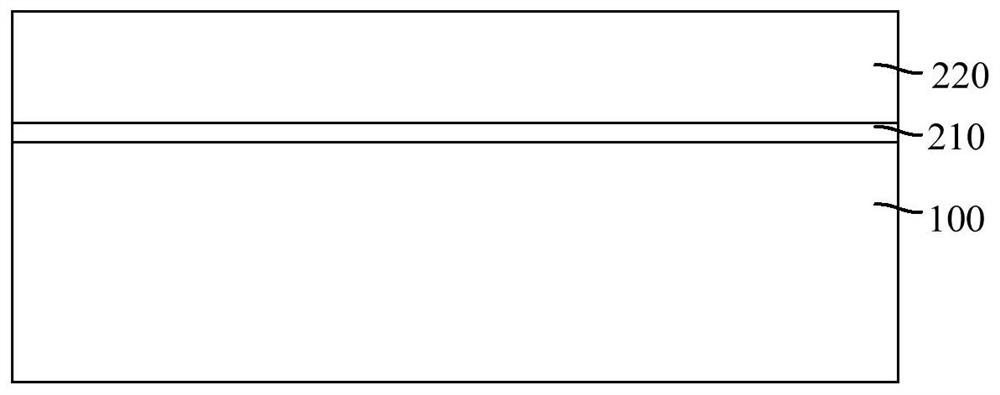

[0047] Step S10: providing a semiconductor substrate, on which a bottom oxide layer and an intermediate oxide layer are sequentially formed;

[0048] Step S20: etching the middle oxide layer, and exposing the bottom oxide layer;

[0049] Step S30: forming a top oxide layer on the middle oxide layer, the top oxide layer also covering the bottom oxide layer exposed by the middle oxide layer;

[0050] Step S40: performing an ion implantation process to form a drift region and a body region in the semiconductor substrate, the drift region and the body region are arranged adjacently and have a junction;

[0051]Step S50: removing the bottom oxide layer and the top oxide layer above the body region to expose the semiconductor substrate, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More