Multi-chip 3D packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, applied in semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve problems affecting product performance, restricting product miniaturization, etc., and achieve the effect of reducing process difficulty and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0085] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

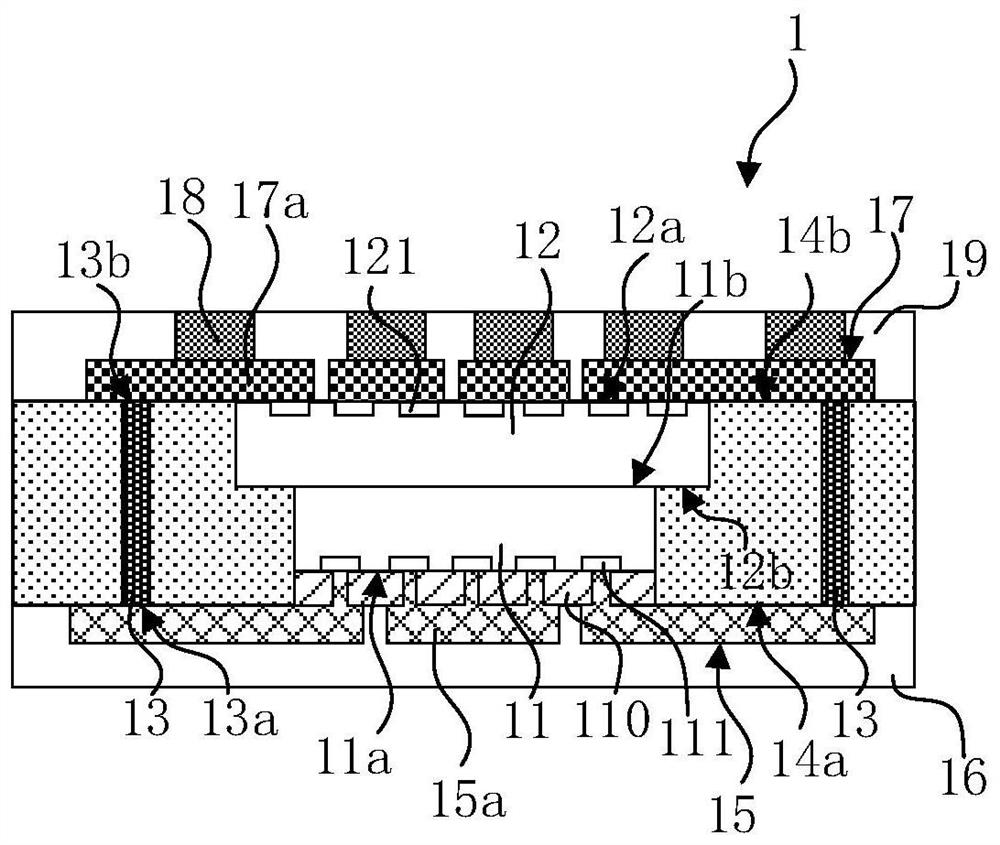

[0086] figure 1 is a schematic cross-sectional structure diagram of the multi-chip 3D packaging structure according to the first embodiment of the present invention.

[0087] refer to figure 1 As shown, the multi-chip 3D packaging structure 1 includes:

[0088] The first die 11 and the second die 12, the first die 11 includes a number of first pads 111, the first pad 111 is located on the active surface 11a of the first die 11, the second die 12 includes a number of second The pad 121, the second pad 121 is located on the active surface 12a of the second die 12; the first die 11 and the second die 12 are arranged back to back;

[0089] The protection layer 110 covers the active surface 11a of the first die 11, and the protection layer 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More