A Circuit for Rapid Gain Calibration of Phase-Locked Loop Digital-to-Time Converters

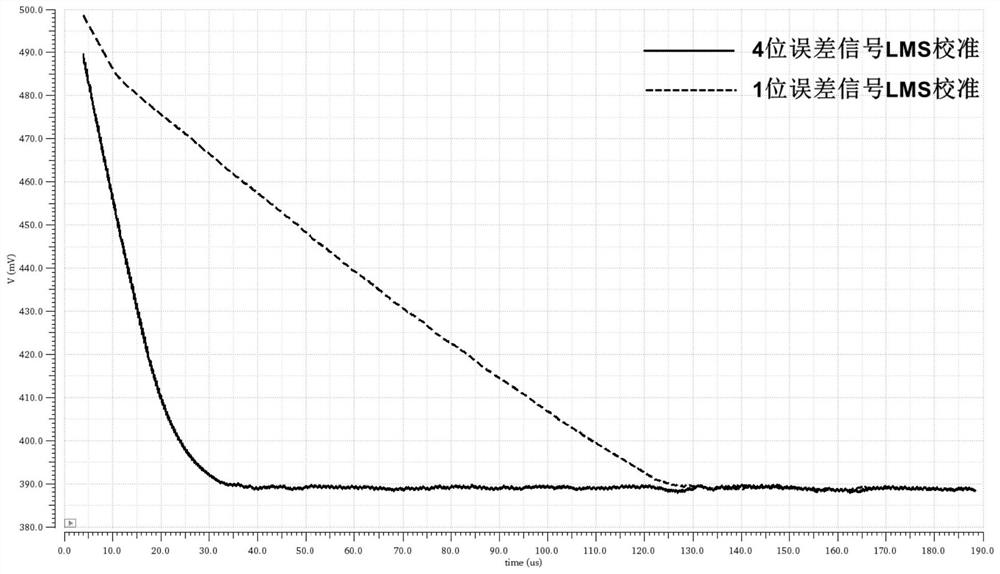

A digital time and converter technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of limited error information and slow calibration speed, and achieve the effect of improving the calibration speed and accelerating the LMS calibration process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

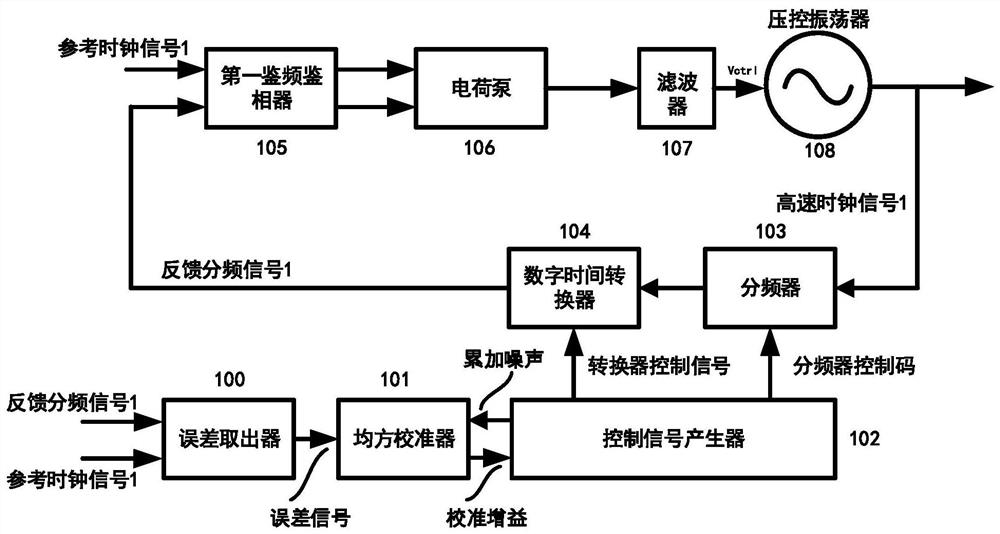

[0013] The circuit that the present invention proposes carries out fast gain calibration to the digital time converter of phase-locked loop, its structure is as follows figure 1 shown, including:

[0014] Error extractor 100, mean square calibrator 101, control signal generator 102, frequency divider 103, digital time converter 104, first frequency and phase detector 105, charge pump 106, filter 107 and voltage controlled oscillator 108 ; Wherein, the output end of described error extractor 100 is connected with the error input end of described mean square calibrator 101; The noise input terminal is connected, the output terminal of the mean square calibrator 101 is connected with the calibration gain input terminal of the control signal generator 102, and the converter control signal output terminal of the control signal generator 102 is connected with the digital time converter 104. The input end is connected, the frequency division control code output end of the control si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More