Forming method of chip metal bump

A technology of metal bumps and forming methods, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., to achieve the effects of improving the quality of balls, reducing costs, and increasing the amount of tin plating

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] In this embodiment, the first electroplating layer 50 is electroplated after all the photoresist layers are formed, and after the panes are formed on all the photoresist layers, electroplating is performed in the lowermost pane. In the first electroplating layer 50 After the electroplating is formed, the metal bump 60 is formed by electroplating on the upper surface of the first electroplating layer 50 , that is, the first electroplating layer 50 and the metal bump 60 are sequentially electroplated and formed.

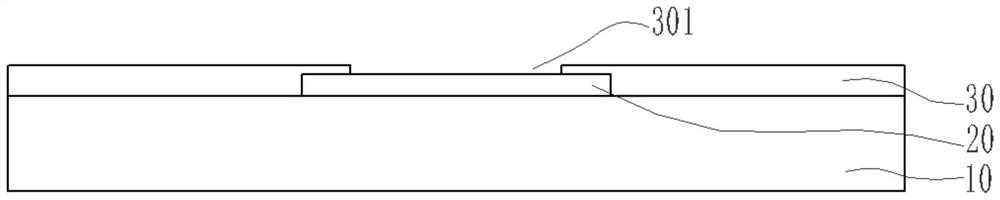

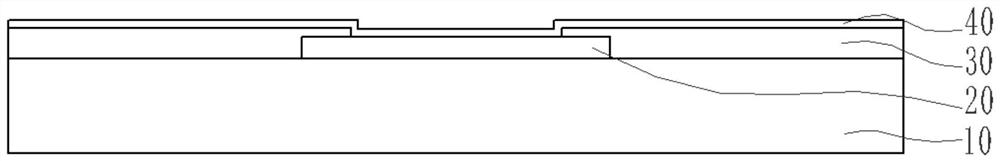

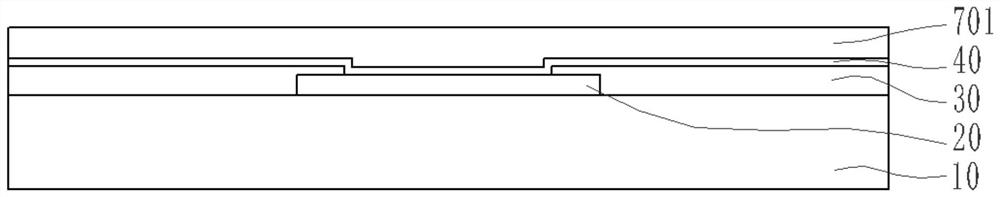

[0050] Specifically, such as Figure 3-9 As shown, there are three photoresist layers formed in this embodiment, namely the first photoresist layer 701, the second photoresist layer 702 and the third photoresist layer 703; correspondingly, the first photoresist layer 701, the second photoresist layer Corresponding first panes 801 , second panes 802 and third panes 803 are respectively formed on the resist layer 702 and the third photoresist layer 703 . The firs...

Embodiment 2

[0053] In this embodiment, the first electroplating layer 50 is formed by electroplating before all the photoresist layers are formed, and the metal bump 60 is formed by electroplating after all the photoresist layers are formed.

[0054] The first electroplating layer 50 is formed by electroplating in the lowermost pane before forming the last photoresist layer; the metal bump 60 is formed on the first electroplating layer 50 after all the photoresist layers are formed.

[0055] The first electroplating layer 50 can be electroplated and formed in the lowermost pane after the lowermost photoresist layer forms the pane, and formed on the upper surface and the lowermost side of the first electroplating layer 50 after forming the first electroplating layer 50. A photoresist layer is formed on the upper surface of the lower photoresist layer, and the panes formed on the photoresist layer cover the first electroplating layer 50 . Then continue to form multi-layer photoresist layers...

Embodiment 3

[0059] In the above-mentioned embodiments, the metal bumps 60 are directly formed on the first electroplating layer 50. Although they can continue to grow on other positions in the pane, due to the part of the photoresist layer exposed through the pane The seed layer is not covered so the shape of the metal bumps 60 formed at these locations is not good. In this embodiment, in order to better realize the growth of the metal bump 60, before the last photoresist layer is formed and after the first plating layer 50 is formed on the lowermost pane, the penultimate layer of photoresist The upper surface of the layer, the upper surface of the first electroplating layer 50 and the upper surface of the part of the photoresist layer exposed outward through the window pane cover the second seed layer 90; the metal bump 60 is formed after the last layer of photoresist layer forms the window pane Electroplating is formed on the upper surface of the second seed layer 90 . In this solution...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More