Communication link layer message single event effect fault tolerance method and device

A single event effect and communication link technology, which is applied in the field of a communication link layer message single event effect fault tolerance method and device, and achieves the effects of high reliability, prevention of false export, and high real-time performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

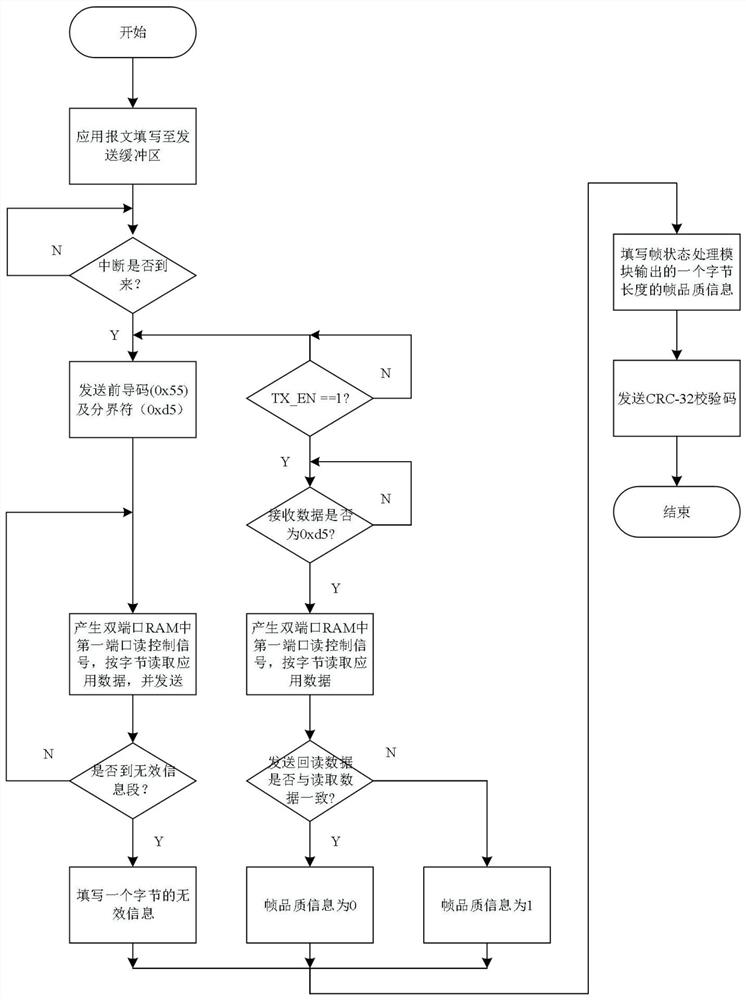

[0034] The present invention will be further described in detail below in conjunction with specific implementation methods and descriptions.

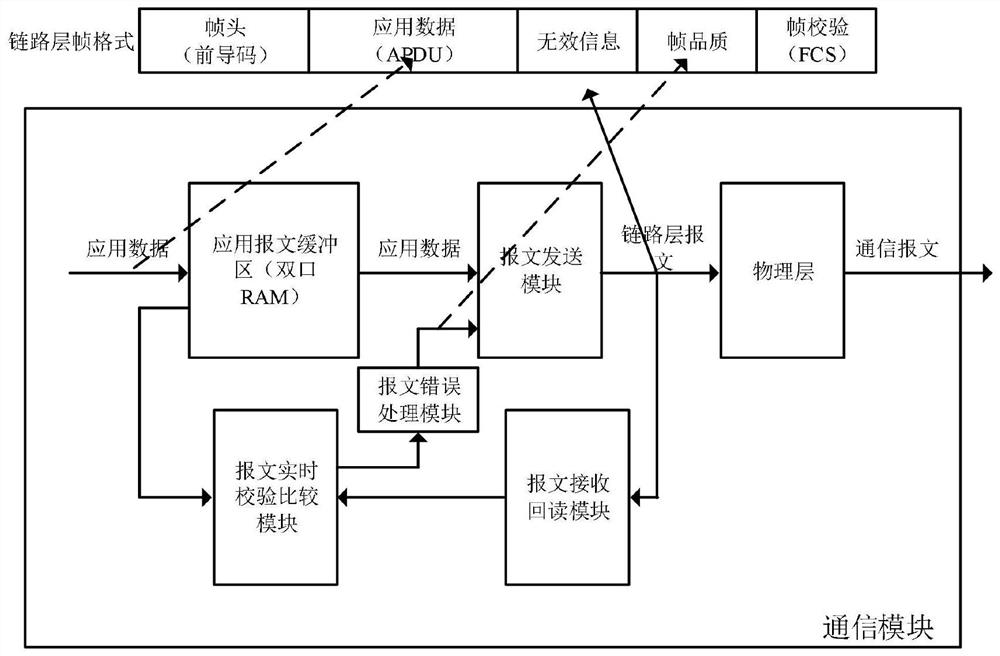

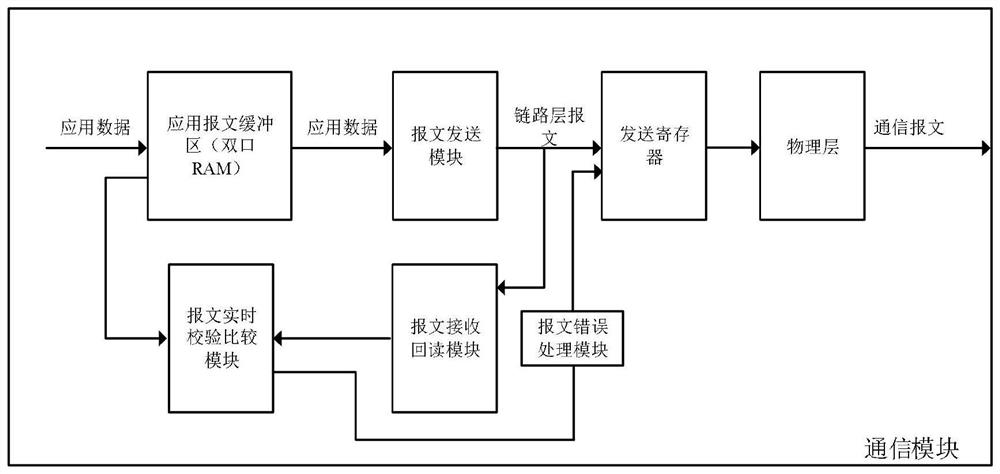

[0035] Such as figure 2 As shown, the communication link layer message single event effect fault-tolerant device of the present invention includes an application message buffer, a message sending module, a message receiving and reading back module, a message real-time verification and comparison module, and a message error processing module . The application message buffer is connected to the physical layer through the message sending module. The input end of the message receiving and reading back module is connected between the message sending module and the physical layer, and the output end of the message receiving and reading back module is connected with the message real-time verification and comparison module. A message error processing module is connected between the message real-time verification and comparison module and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More