Thermoelectric refrigeration method for chip-level electronic equipment

A technology for electronic equipment and thermoelectric refrigeration, which is applied in the directions of thermoelectric device parts, circuits, electrical components, etc., can solve the problems of slow progress in thermoelectric cooling technology research, insufficient application performance of heat transfer characteristics of heating electric cooling systems, etc. Electronically quiet, high reliability, small size and weight

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

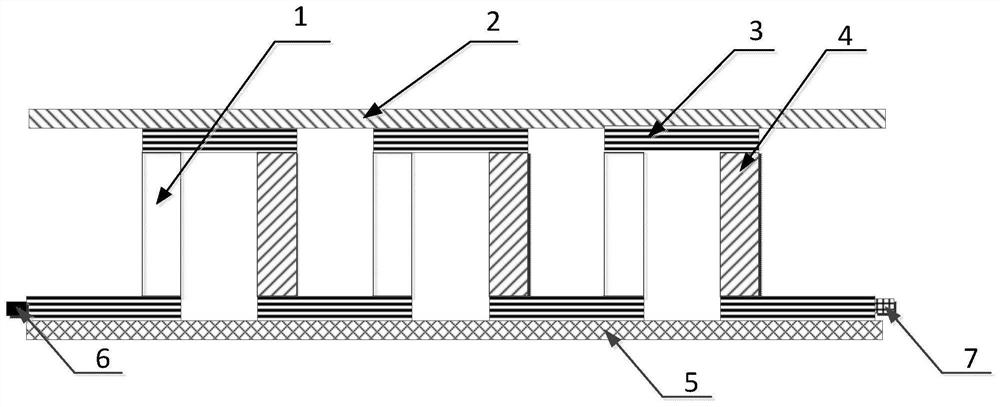

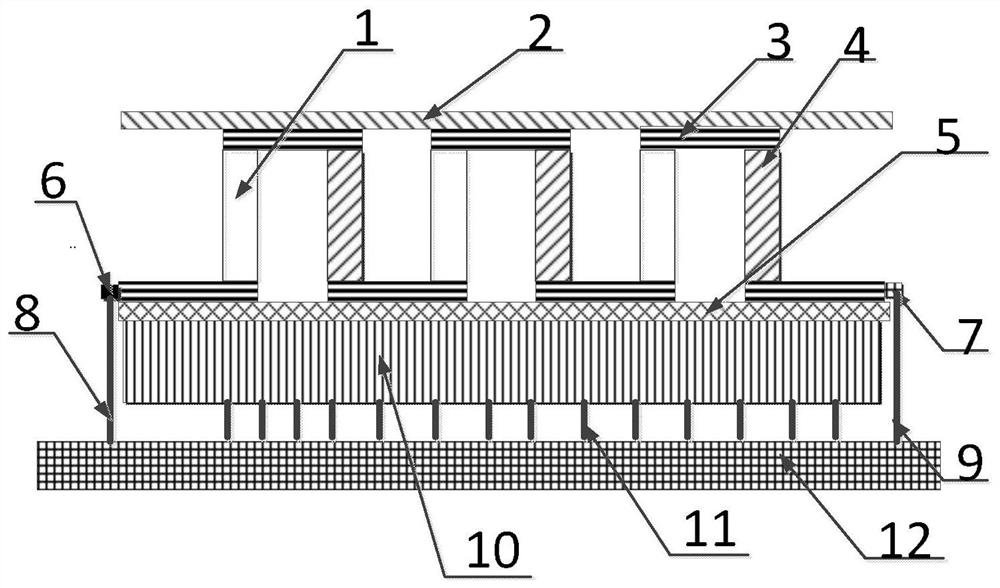

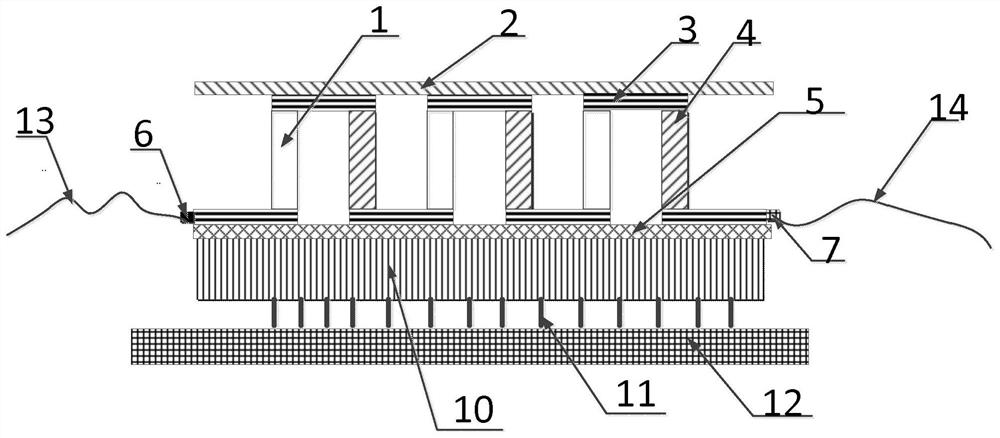

[0015] refer to figure 1. According to the present invention, when conditions such as P-type semiconductor chip 1 and power supply permit, N bow-shaped wave-connected cooling plate conductive plates 3 are laid alternately and flatly on the space between the thermal conductor heat dissipation panel 2 and the thermal conductor cooling panel 5 according to the line interval. On the inner side wall, the thermal conductor cooling panel 5 is in close contact with the chip through the thermal interface material to absorb the heat of the pseudo-chip, and the thermal conductor cooling panel 2 is in close contact with the next-level heat sink; then the P-type semiconductor chip 1 and the N-type semiconductor chip 4. Two semiconductor materials of different polarities, P-type and N-type, are vertically fixedly connected to the two ends of the conductive plate 3 of the bow-shaped corrugated refrigerating plate, and are connected into galvanic couple pairs, and the bow-shaped corrugated th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More