Power failure monitoring method and device, electronic equipment and computer readable storage medium

A technology of electronic equipment and storage media, which is applied to the detection of faulty computer hardware, faulty hardware testing methods, calculations, etc., and can solve problems such as power loss and inability to record logs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0059] 1) PSU information detection design

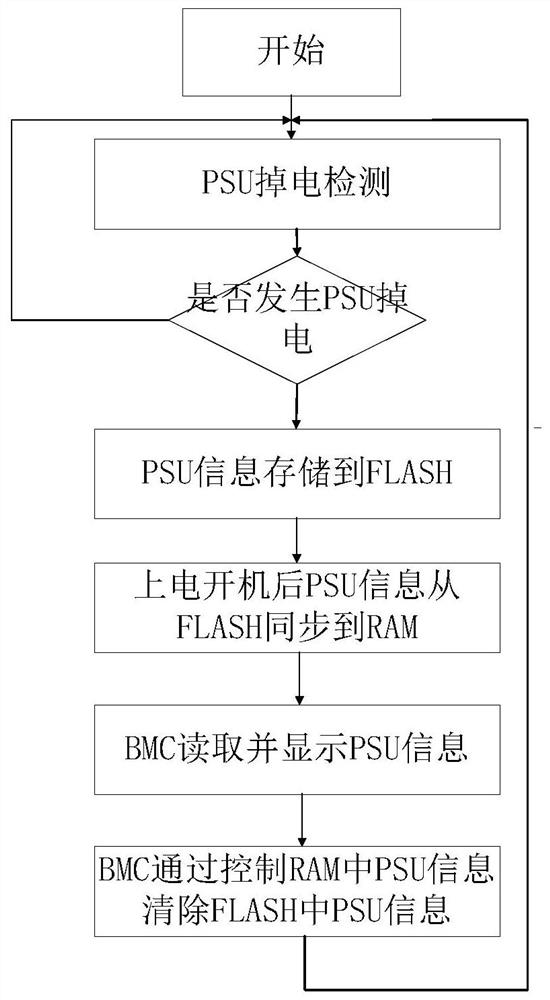

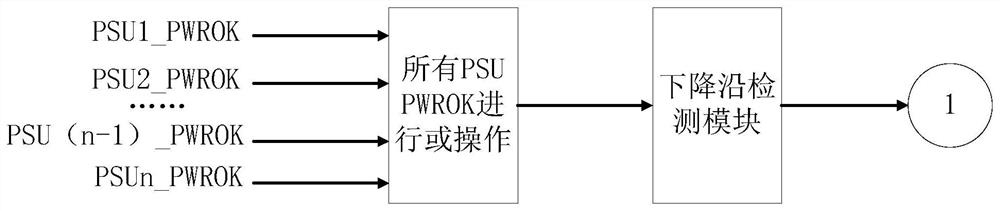

[0060] Through the CPLD / FPGA high-speed system clock, the falling edge of the PWROK signal indicating that the working status information of each PSU is normal is monitored in real time. When all PSU PWROK signals are detected to be abnormal, the PSU power-off indication signal is obtained. Schematic diagram of PSUPWROK power supply indication detection module function such as figure 2 shown.

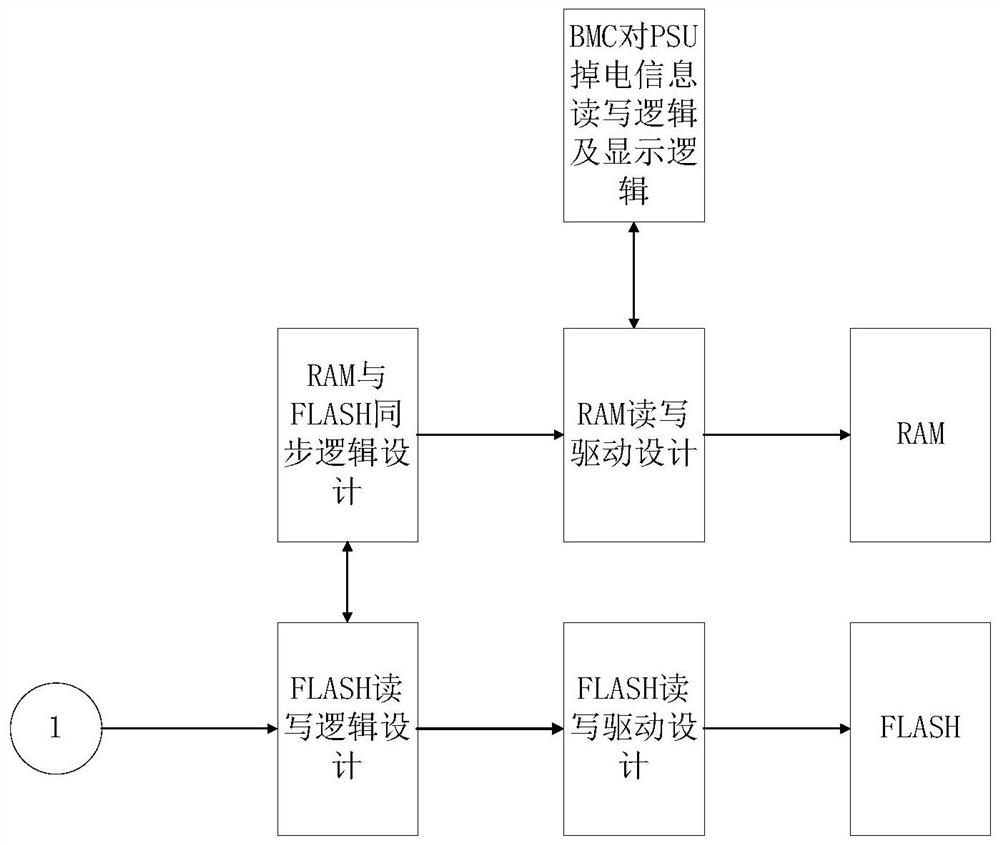

[0061] 2) FLASH reading design

[0062] When the PSU PWROK signal is abnormal, write operation to FLASH, especially, this is carried out by following the FLASH timing through the state machine. When the PSU PWROK signal returns to normal, perform a read operation on the FLASH. When the upper controller clears the FLASH PSU indicator bit, it writes the FLASH PSU indicator bit and writes the current PSU PWROK normal information. In particular, for CPLD, PSU information can be stored in its own user FLASH, and for FPGA, PSU information can ...

Embodiment 2

[0068] 1) based on embodiment one principle based on CPLD / FPGA and BMC design switch PSU power down failure information record and display system;

[0069] 2) Compile the CPLD / FPGA and BMC program, and update the CPLD / FPGA and BMC burning image;

[0070] 3) Plug and unplug the PSU, verify the effectiveness of the strategy and optimize the PSU power-down information recording and protection system of the switch.

[0071] The PSU power-off information recording and display system proposed by the present invention can not only be applied to the switch system, but also can be used in the server system. At the same time, FLASH can not only record the PSU power-off information, but also can record any information that is lost or expected to be saved when the power is off.

[0072] It should be noted that like numerals and letters denote similar items in the following figures, therefore, once an item is defined in one figure, it does not require further definition and explanation in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More