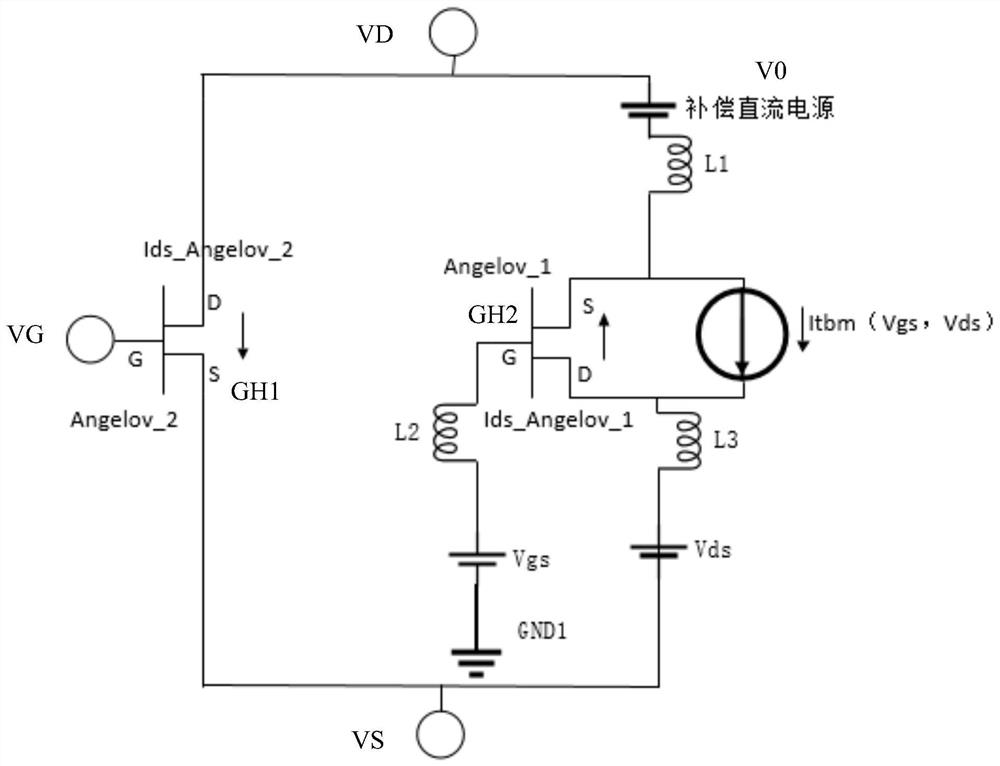

GaN HEMT scaling model circuit topological structure

A circuit topology and model technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of look-up table range and huge data, discontinuous relationship, difficult to guarantee accuracy, etc., to solve model accuracy and The problem of ductility, meeting the requirements of circuit simulation, and the effect of meeting temperature change characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the technical means realized by the present invention easier to understand, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the related application, not to limit the application. In addition, it should be noted that, for ease of description, only parts relevant to the present application are shown in the drawings.

[0026] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. The present application will be described in detail below with reference to the accompanying drawings and embodiments.

[0027] see figure 1 , the present invention provides a GaN HEMT scaling model circuit topology, which is a GaN HEMT (HEMT is a high electron mobility transistor) scaling model cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More