System-on-chip development environment building method and system

A development environment and component technology, applied in the direction of creating/generating source code, program control design, program loading/starting, etc., to achieve the effect of good application prospects, convenient construction process, and ensure system stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the purpose, technical solution and advantages of the present invention more clear and understandable, the present invention will be further described in detail below in conjunction with the accompanying drawings and technical solutions.

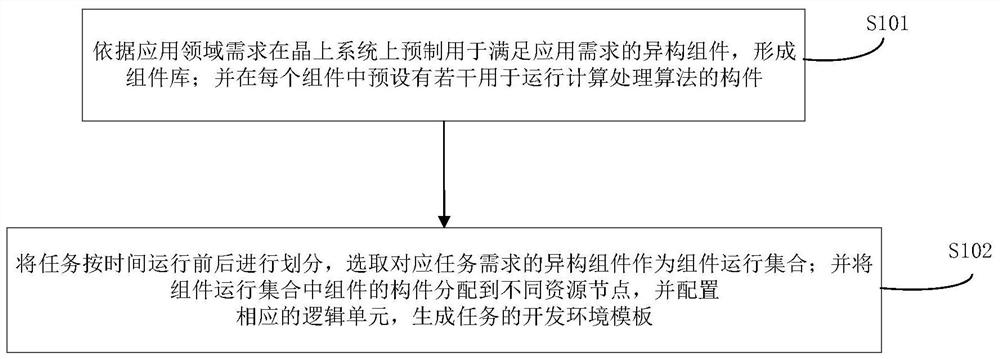

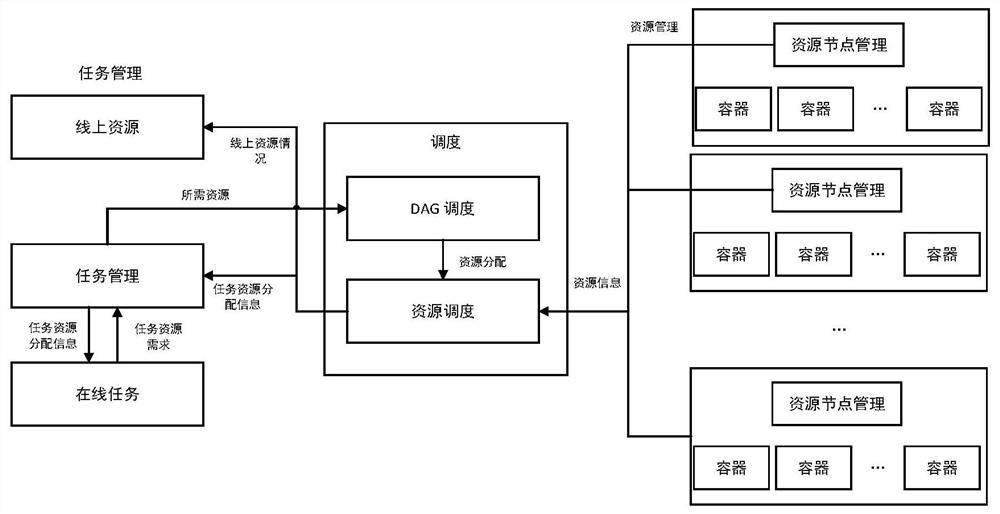

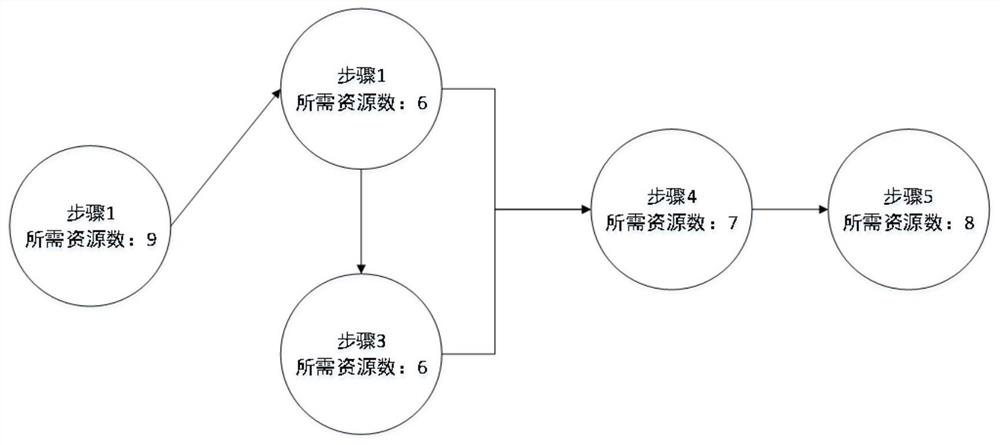

[0029] The system on chip integrates the system in a single chip, and its core function lies in the integration of multi-functional modules. The technical advantage is mainly compared with SoC chips and PCB-based integration technologies. Come change. The on-chip system has a good development prospect, but its huge computing resources and complex interconnection have brought great challenges to the compilation system. How to make full use of system resources and provide users with a convenient and easy-to-use development environment. Embodiment of the present invention, see figure 1 As shown, a method for building an on-chip system development environment is provided, see figure 1 As shown, it contains the following...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More