Interlayer connection of stacked microelectronic components

A technology of interlayer connection and microelectronics, applied in the direction of electrical components, electrical solid devices, semiconductor/solid device parts, etc., can solve impractical problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] overview

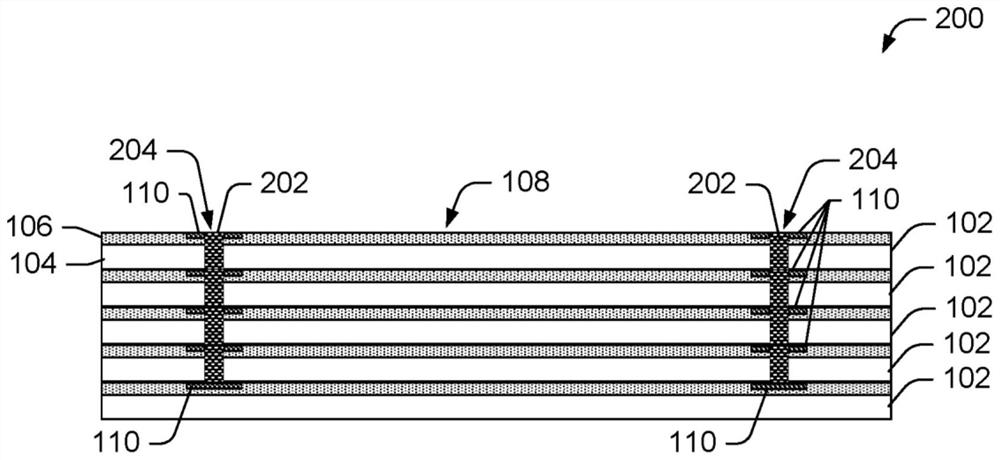

[0031] In various embodiments, techniques and devices may be employed to simplify the common electrical connection of all desired dies and / or wafers in a die-to-die stack, a die-to-wafer stack, or a wafer-to-wafer stack, particularly when the stack 2 1 or more dies and / or wafers. Discussions herein in relation to dies also refer to wafers or other substrates in such stacks.

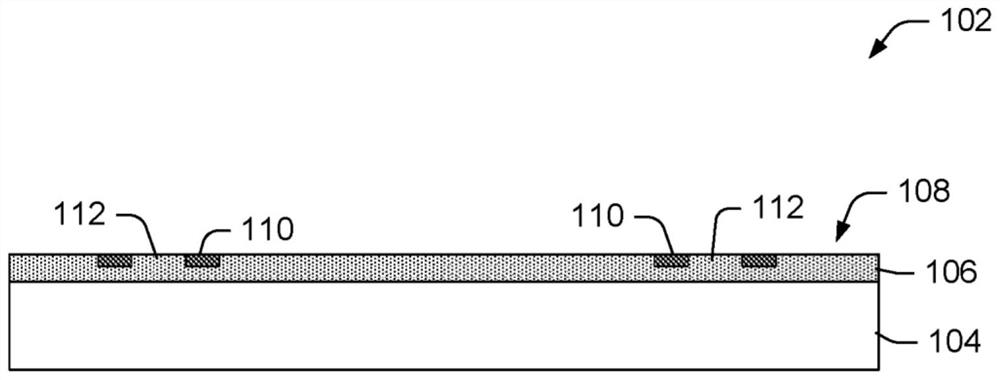

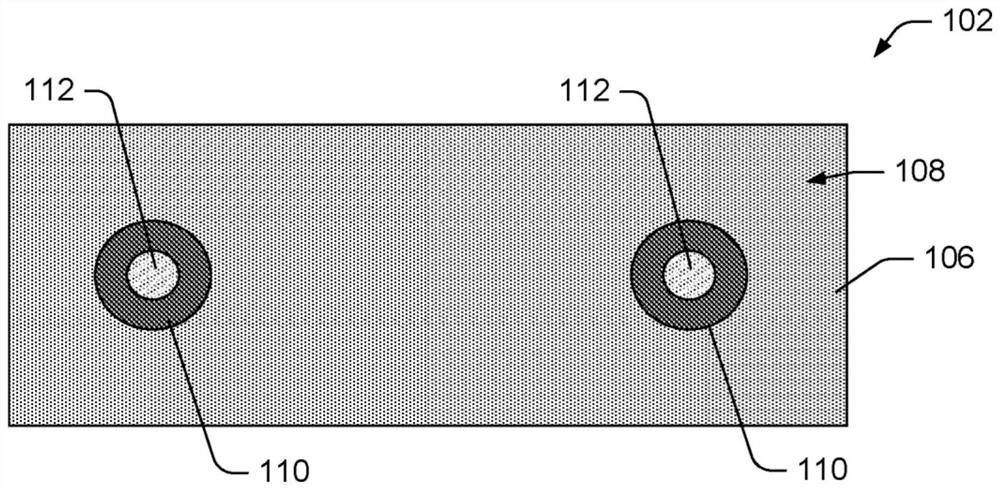

[0032] see Figure 1A (which shows a cross-sectional profile view) and Figure 1B (which shows a top view), the patterned metal and oxide layers are often used as hybrid bonds, or The surface layer is disposed on a die, wafer, or other microelectronic substrate (hereinafter referred to as "die 102"). A representative device die 102 may be formed using various techniques to include a base substrate 104 and one or more insulating or dielectric layers 106 . The base substrate 104 may be composed of silicon, germanium, glass, quartz, a dielectric surface, a direct gap semiconductor mater...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com