Method for ensuring data crash consistency in secure nonvolatile memory and processor

A non-volatile and consistent technology, applied in electrical digital data processing, memory systems, memory address/allocation/relocation, etc., can solve problems such as high transaction execution delay and write amplification cannot be effectively balanced, to avoid persistence Order constraints, reduce waiting delay, and improve the effect of scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

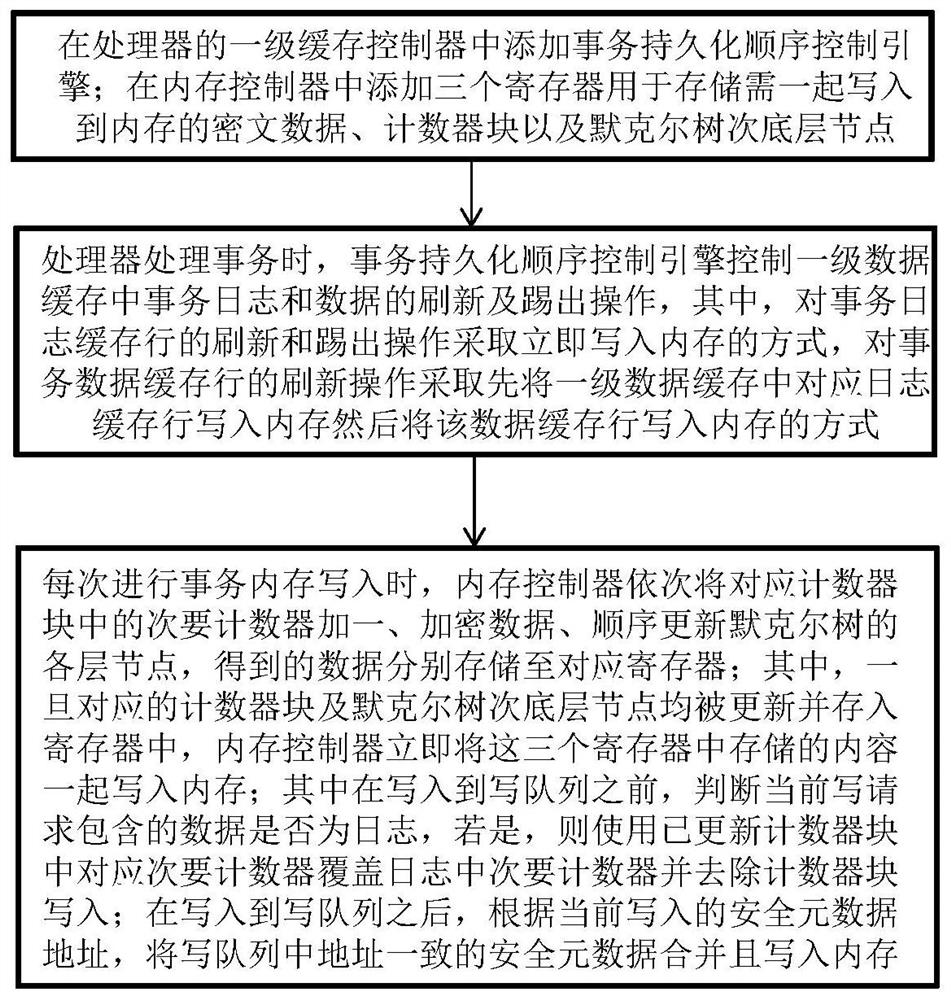

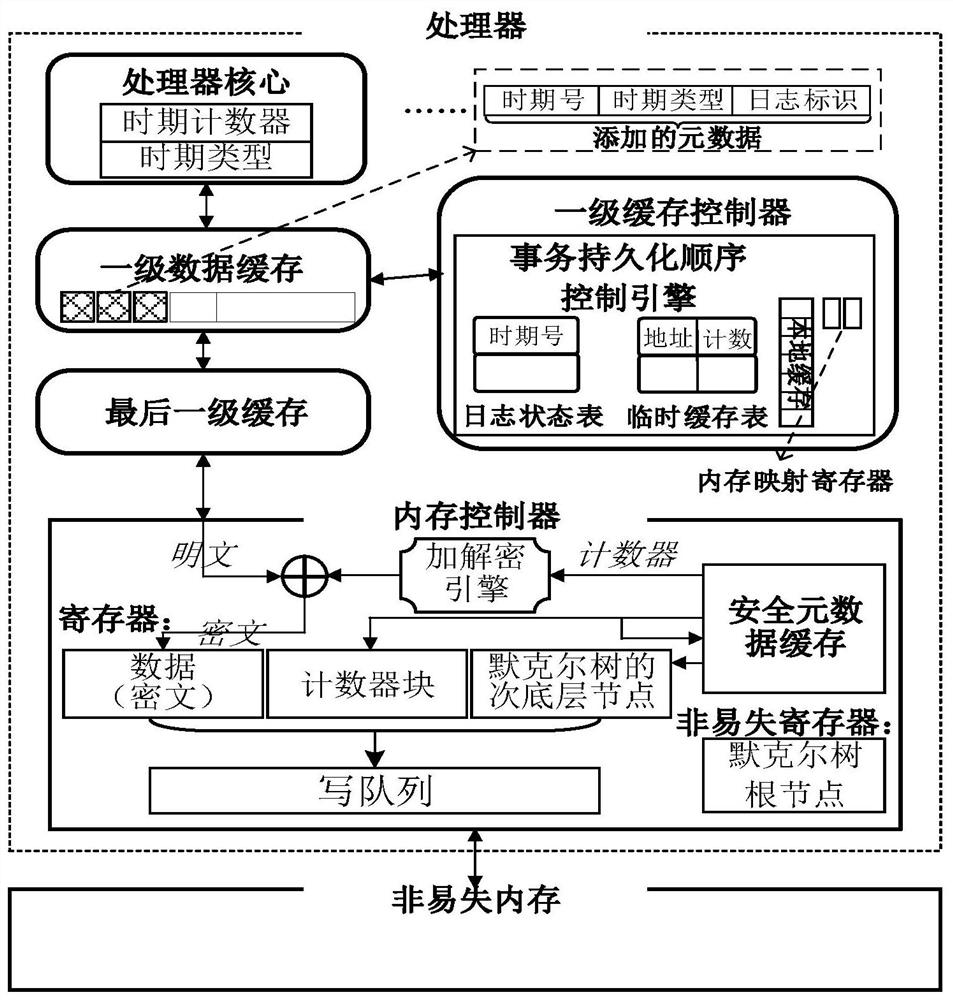

[0039] A method for guaranteeing data crash consistency in secure non-volatile memory, such as figure 1 As shown, including: adding a transaction persistence sequence control engine in the processor's first-level cache controller; adding three registers in the memory controller to store the ciphertext data, counter blocks, and default The sub-bottom node of the Kerr tree, and the steps for the above processor to process transactions include:

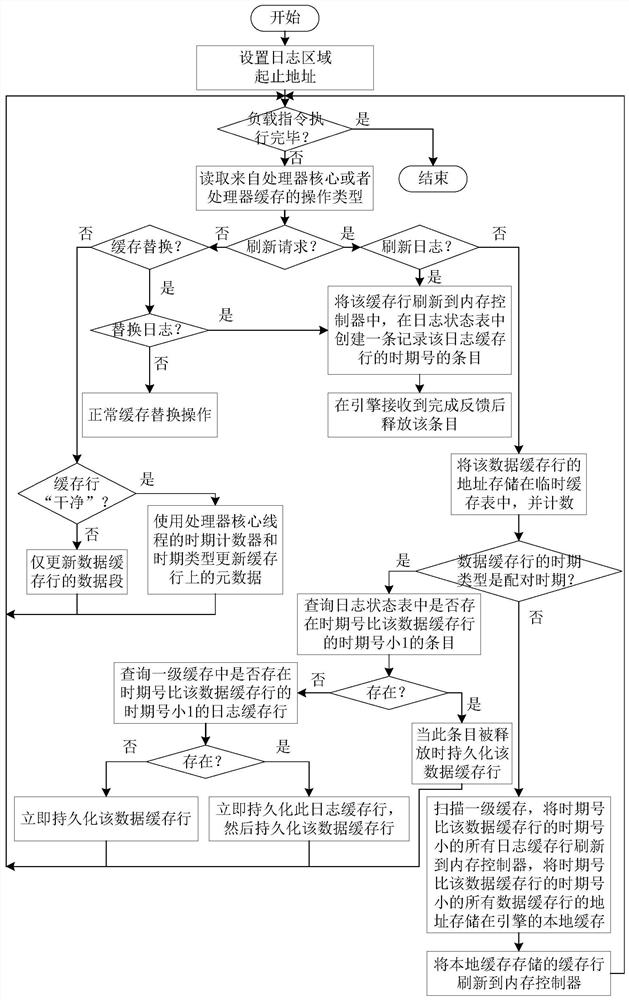

[0040] (1) The transaction persistence sequence control engine controls the refresh and kick-out operations of transaction logs and data in the first-level data cache. The refresh and kick-out operations of transaction log cache lines are immediately persisted (that is, written) to memory In this way, the refresh operation of the transaction data cache line adopts the method of first persisting the corresponding log cache line in the first-level data cache and then persisting the data cache line;

[0041] The method of this embodiment a...

Embodiment 2

[0055] A processor that guarantees data crash consistency in a secure non-volatile memory, including: a processor core, a first-level data cache, a first-level cache controller, and a memory controller, wherein the first-level cache controller includes a transaction persistence sequence Control engine; the memory controller includes three registers for storing the ciphertext data, the counter block, and the sub-bottom node of the Merkle tree that need to be persisted to the memory together; among them,

[0056] The transaction persistence sequence control engine is used to control the refresh and kick operations of transaction logs and data in the first-level data cache. Among them, the refresh and kick operations of transaction log cache lines are immediately written into memory, and the transaction data cache The line refresh operation takes the method of first writing the corresponding log cache line in the first-level data cache into the memory, and then writing the data ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com