Novel parallel-serial conversion circuit

A serial conversion and circuit technology, applied in the field of new parallel-serial conversion circuits, can solve the problems affecting the accuracy of data transmission, high clock rate requirements, and increased bit error rate, achieving strong practicability, strong scalability, and reducing input bandwidth. the effect of the request

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further elaborated below in conjunction with embodiment.

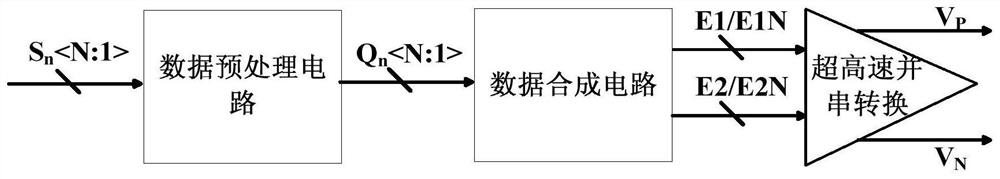

[0031] A new type of parallel-to-serial conversion circuit, such as Figure 1-3 As shown, including data preprocessing circuit, data synthesis circuit and driver circuit,

[0032] The data preprocessing circuit sends the preprocessed N-bit data Q n , Q n ,...,Q n 、Q n To the data synthesis circuit, and use the reverse data Q of the Nth preprocessed data n N with input N-bit parallel data S n , S n ,...,S n 、S n Do XOR logic and XOR logic operations, the specific formula is as follows

[0033]

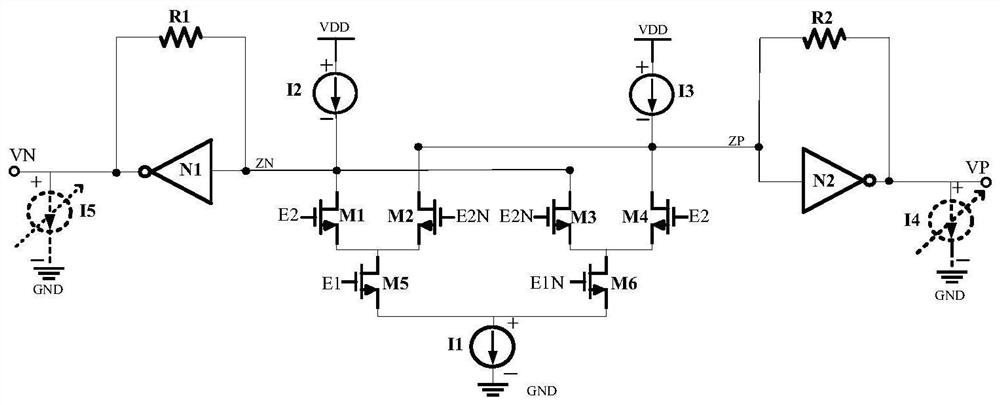

[0034] The data synthesis circuit preprocesses the data Q according to the received N bits n-1 , using a related data synthesis structure, such as a tree structure or a parallel structure, to convert it into two sets of differential parallel data information E1, E1N, E2, E2N, where one set of differential data information E2, E2N is compared with the oth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com