Dielectric temperature coefficient corrected deep energy level transient spectrum testing method

A technology of temperature coefficient and test method, applied in the direction of semiconductor/solid-state device test/measurement, circuit, electrical components, etc., can solve inaccurate problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

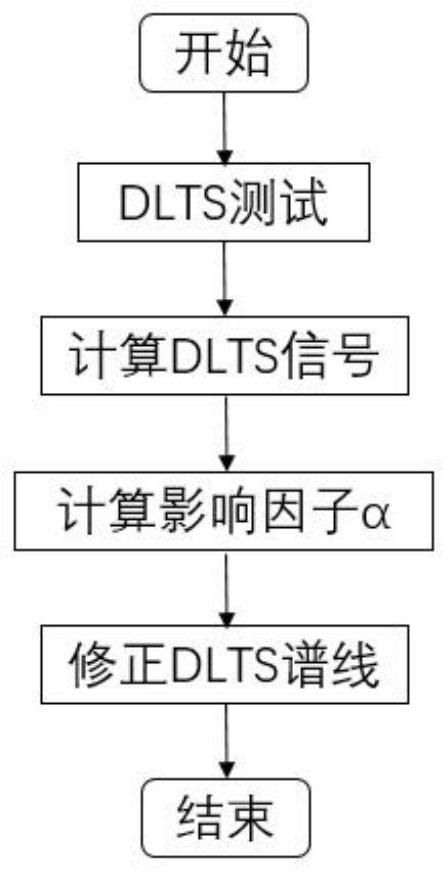

[0035] Specific embodiments: a method for testing deep-level transient spectrum with dielectric temperature coefficient correction. In this embodiment, the target sample is a MOS device with a metal-oxide layer-semiconductor layer structure.

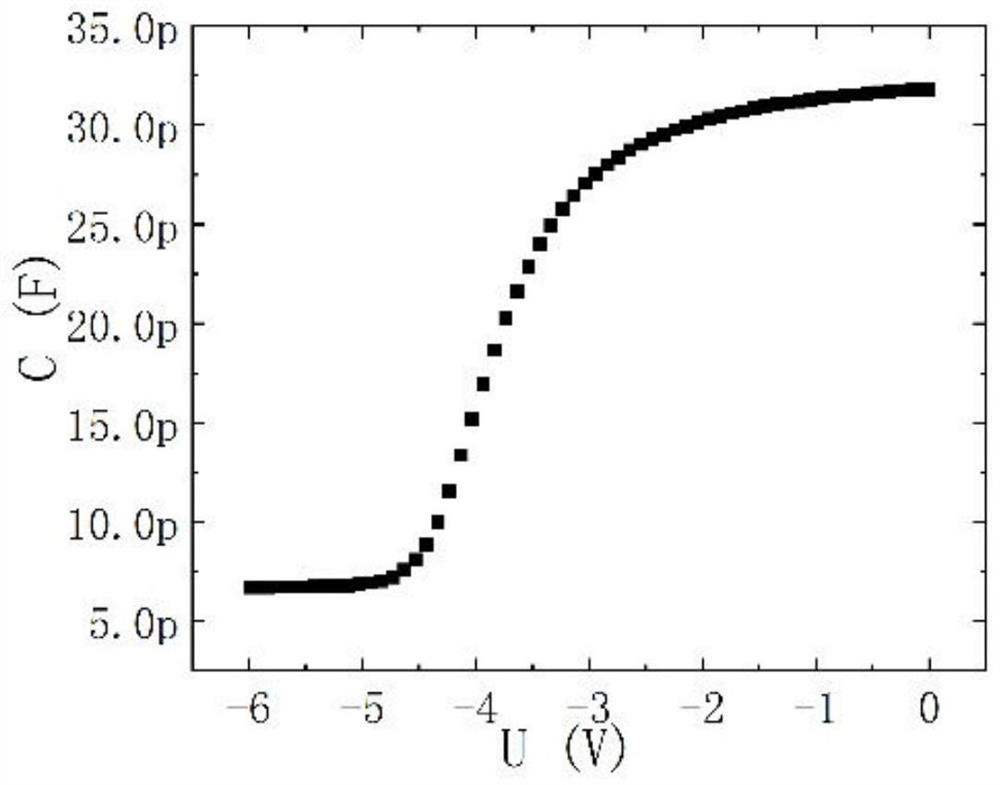

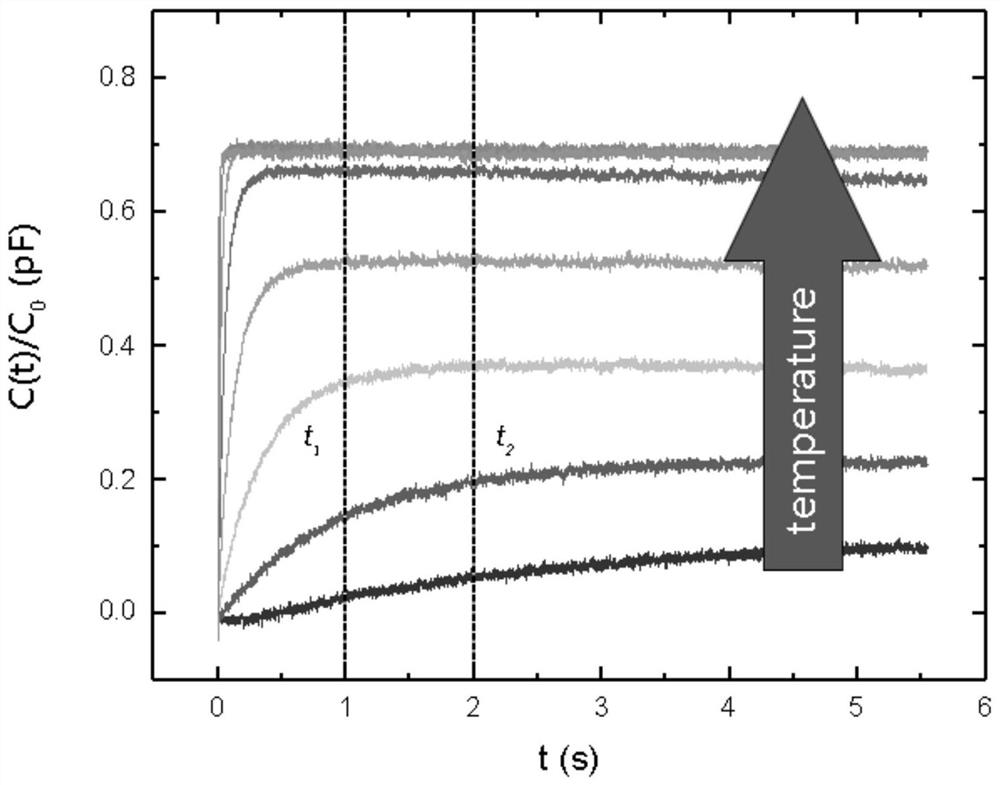

[0036] Step 1: carry out C-V test to target sample (such as figure 2 ) and determine that the sample bias voltage is -5V, the pulse height is 3V and the pulse width is 10ms. Ensure that the test parameters are within the range of the test system. The samples were tested by DLTS, and the capacitance transient information of the samples at different temperatures was collected for analysis. Get the capacitance transient C-t curve at different temperatures, and then select two fixed times t 1 , t 2 (Such as image 3 ) and its corresponding capacitance change can be expressed as:

[0037]

[0038] where C(t 1 ), C(t 2 ) is t1 , t 2 Test capacitance at moment, n T is the electron concentration in the trap, C 0 is the defect capac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More