A multi-clock domain concurrent test system and test method for SoC chips

A multi-clock domain and test system technology, which is applied in the field of multi-clock domain concurrent test system, can solve problems such as low test efficiency, inability to test work, and only one test can be started, so as to improve test efficiency, reduce test cost, and solve low-cost problems. effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

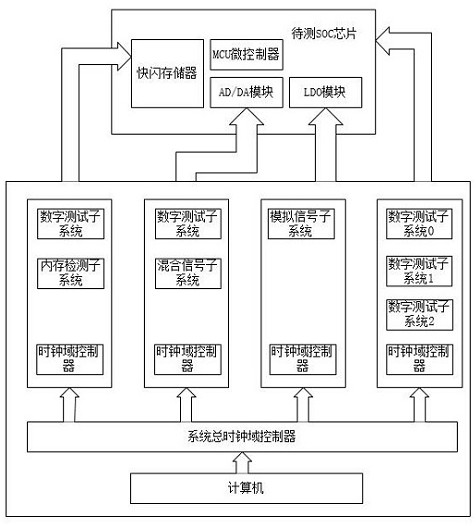

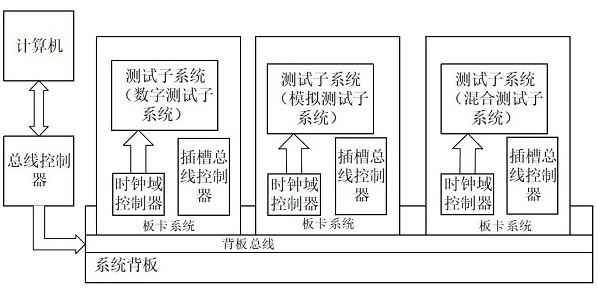

[0030] Such as figure 1 with figure 2As shown, a multi-clock domain concurrent test system for SOC chips, the system includes a system backplane, a backplane bus, a bus controller and a board system, the system backplane is provided with a backplane slot, and the board system passes through the backplane The board slot is installed on the system backplane, and the backplane bus is set on the system backplane through the bus slot. The backplane bus realizes the connection between the boards. The system backplane is connected to the computer through the bus controller. and the clock domain controller, slot bus controller and test subsystem arranged on the board, the clock domain controller is connected to the test subsystem and the slot bus controller, and the slot bus controller is connected to the backplane bus; the slot bus The controller implements data exchange and synchronization between board systems on the backplane slot; the clock domain controller is responsible for ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More