DDR4 address control line mapping and Ball arrangement method for T-type topological structure

A DDR4, address control technology, used in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as increased wiring area, uncontrollable factors, inconsistent delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

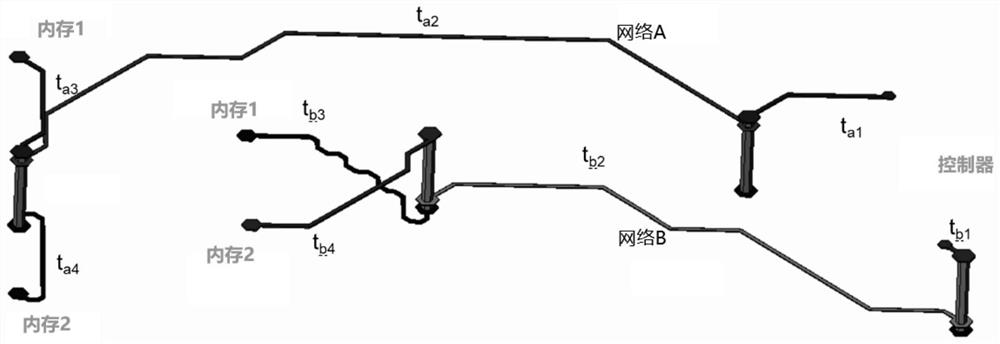

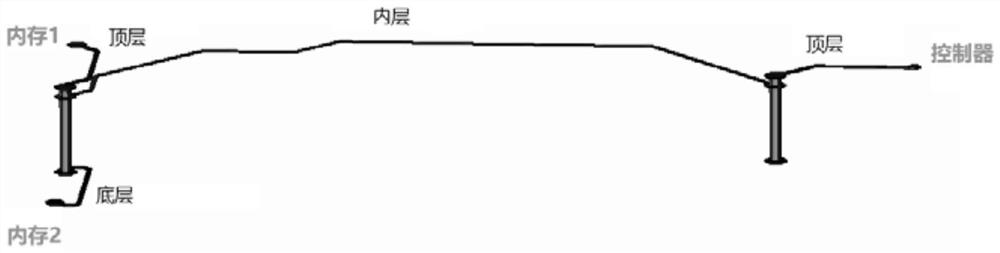

[0014] figure 1 It is an application case of the DDR4 address control line mapping and Ball arrangement method for the T-type topology of this embodiment. A and B are two address / control signals in the same group. The delay of each segment is as shown in the figure below. For the convenience of discussion, it is assumed that the branches after the T type are equal, that is, t a3 =ta4,t b3 =tb4. At the receiving end of any memory, the delay of the address control line satisfies Equation 1. According to the previous discussion, the delay of the signals in the same group, network A and network B will affect the size of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com