FPGA-based prototype verification method and encoding device

A prototype verification and configuration file technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as low error checking efficiency, failure to troubleshoot problems, and long test file cycle, so as to improve flexibility and shorten Error troubleshooting cycle, the effect of speeding up the debugging cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

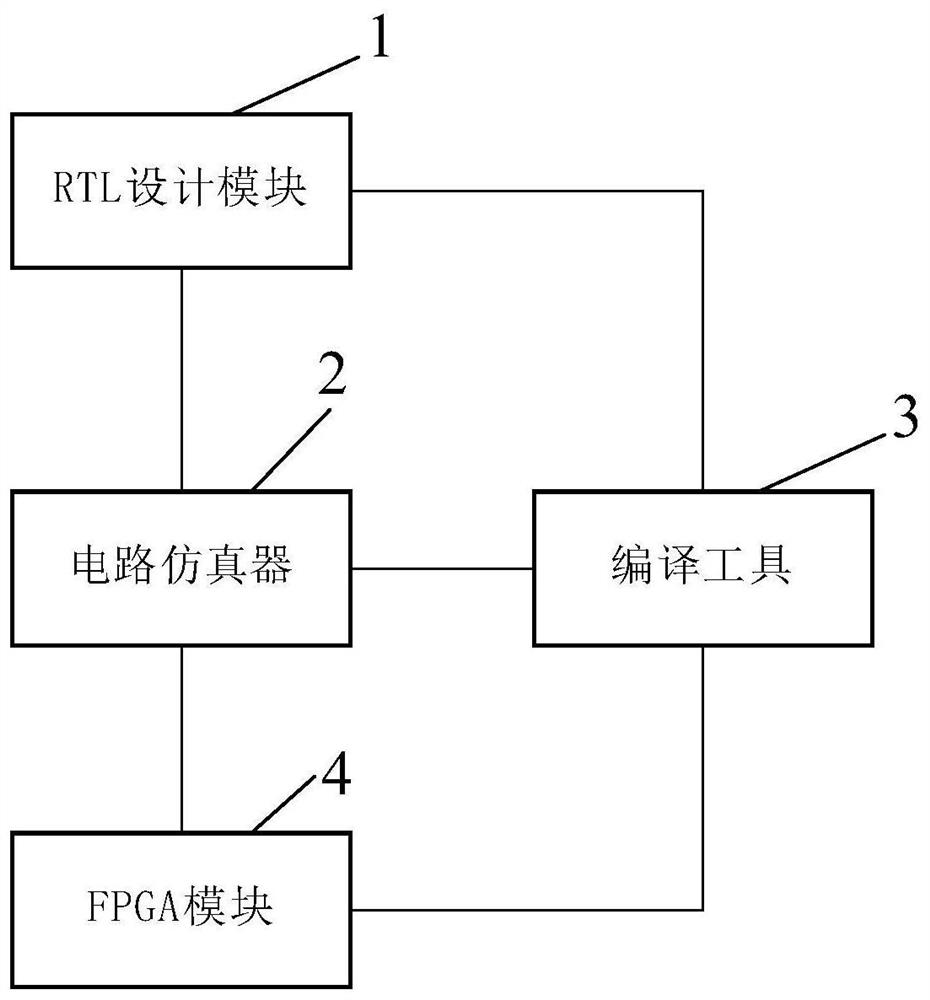

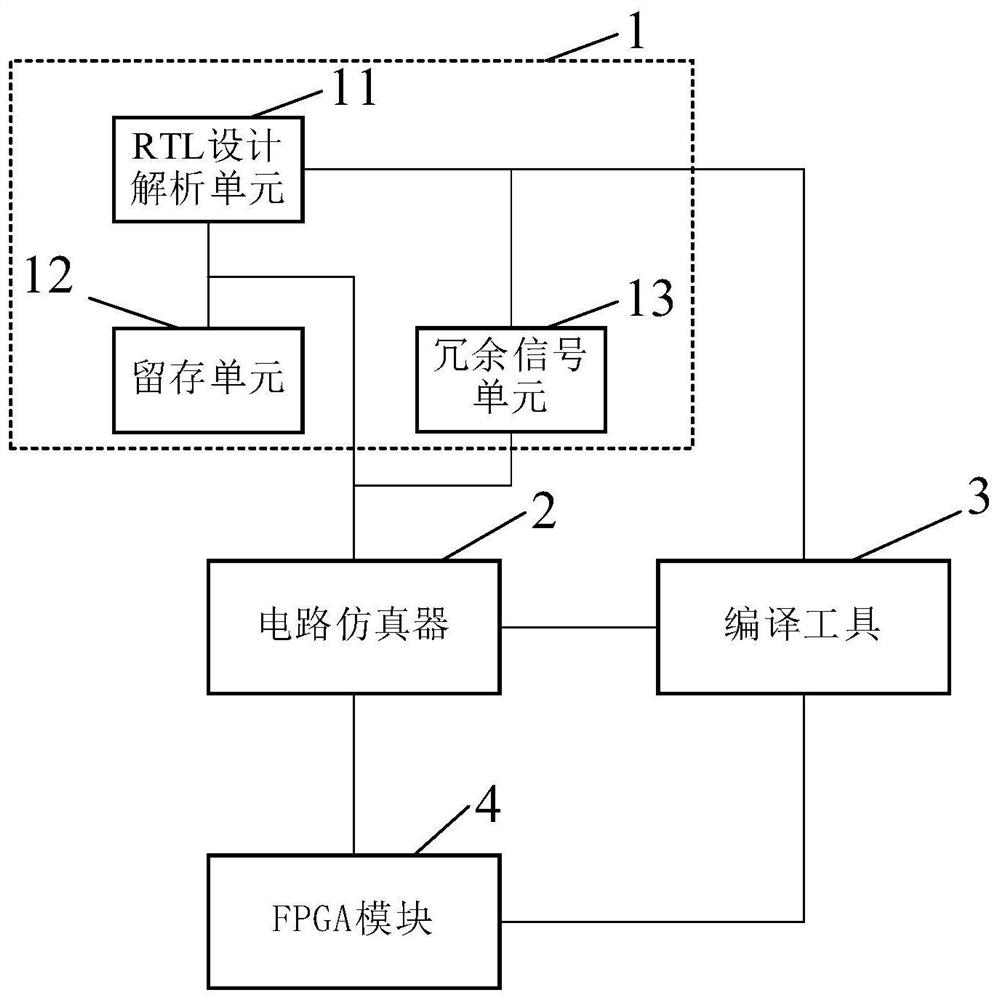

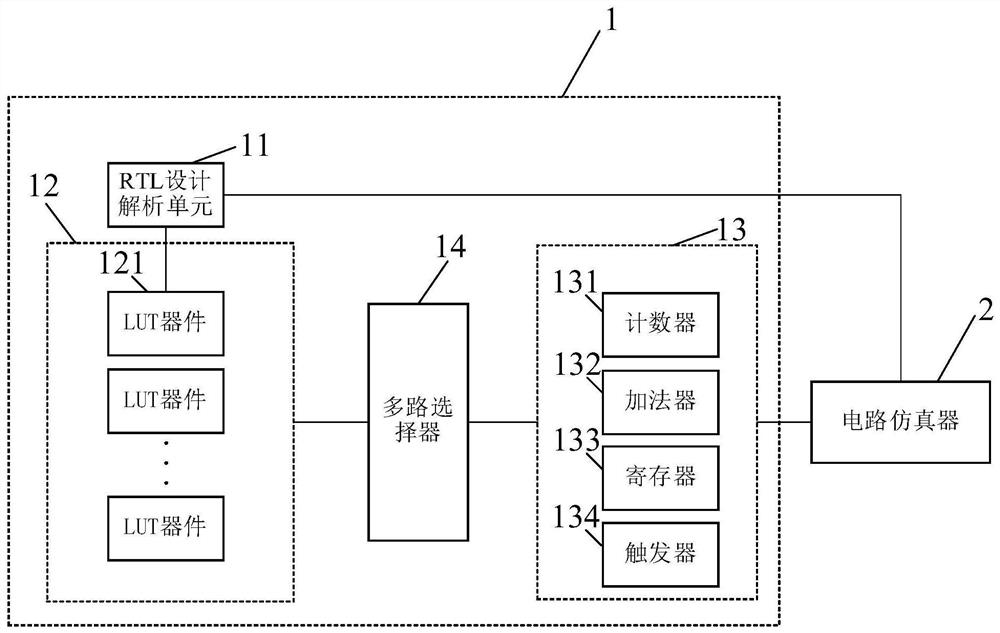

[0020] Various embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so as to better understand the purpose, features and advantages of the present invention. It should be understood that the embodiments shown in the drawings are not intended to limit the scope of the present invention, but only to illustrate the essence of the technical solutions of the present invention.

[0021] In the following description, for the purposes of explaining the various disclosed embodiments, certain specific details are set forth in order to provide a thorough understanding of the various disclosed embodiments. One skilled in the relevant art will recognize, however, that an embodiment may be practiced without one or more of these specific details. In other instances, well-known devices, structures and techniques associated with the present application may not have been shown or described in detail in order to avoid unnecessarily...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More