Patents

Literature

89 results about "Sigaction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, sigaction is a function API defined by POSIX to give the programmer access to what should be a program's behavior when receiving specific OS signals.

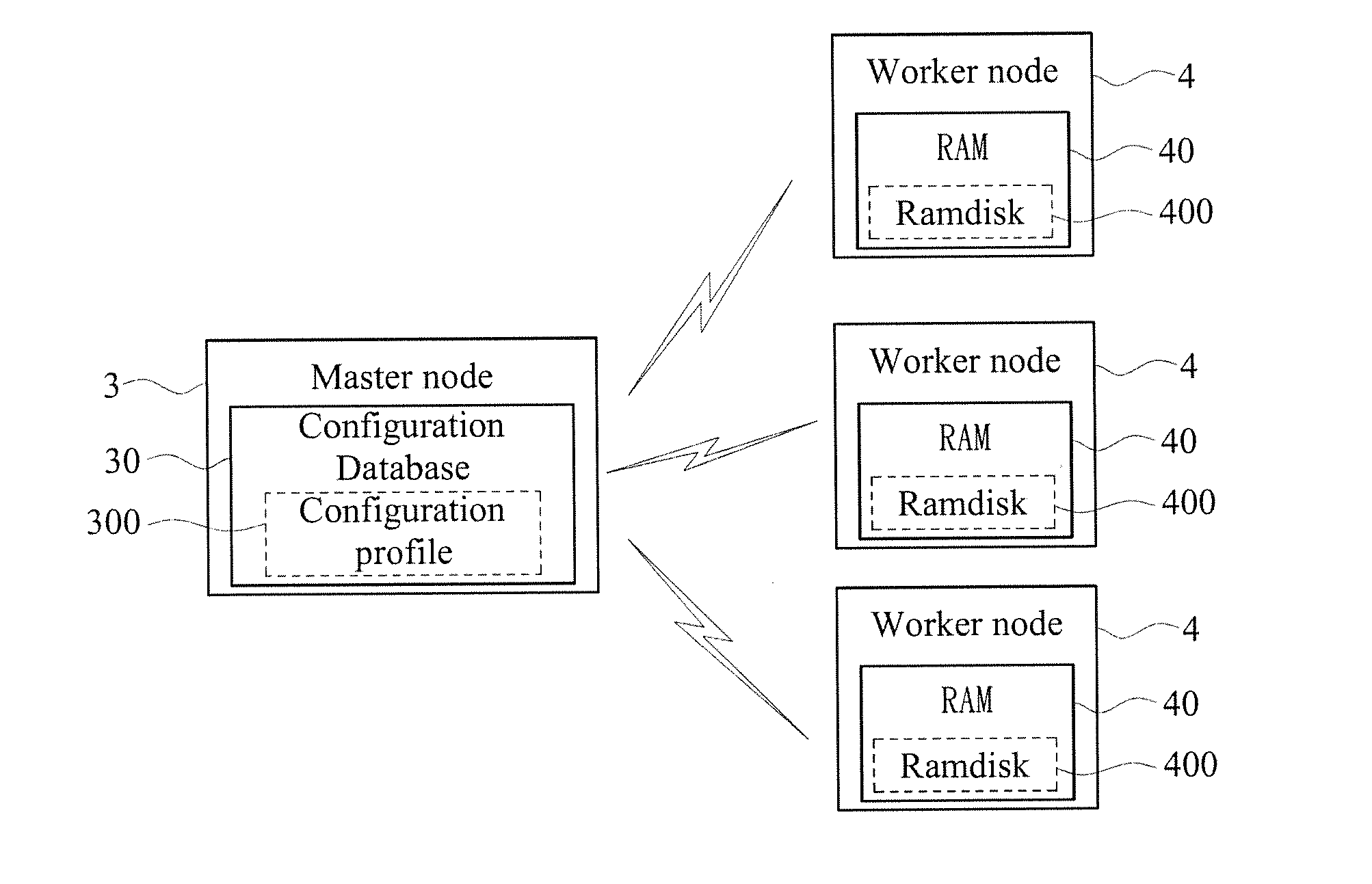

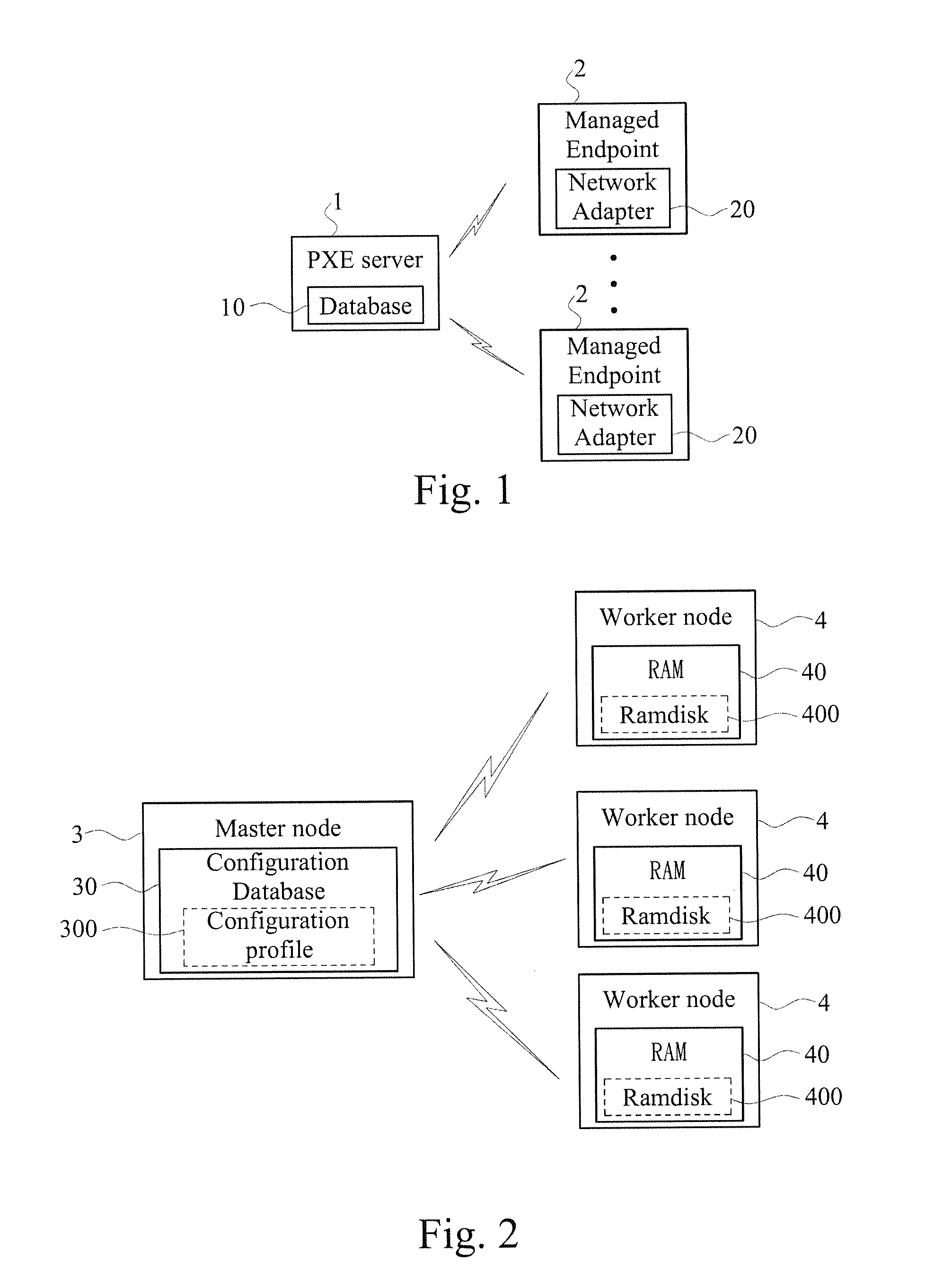

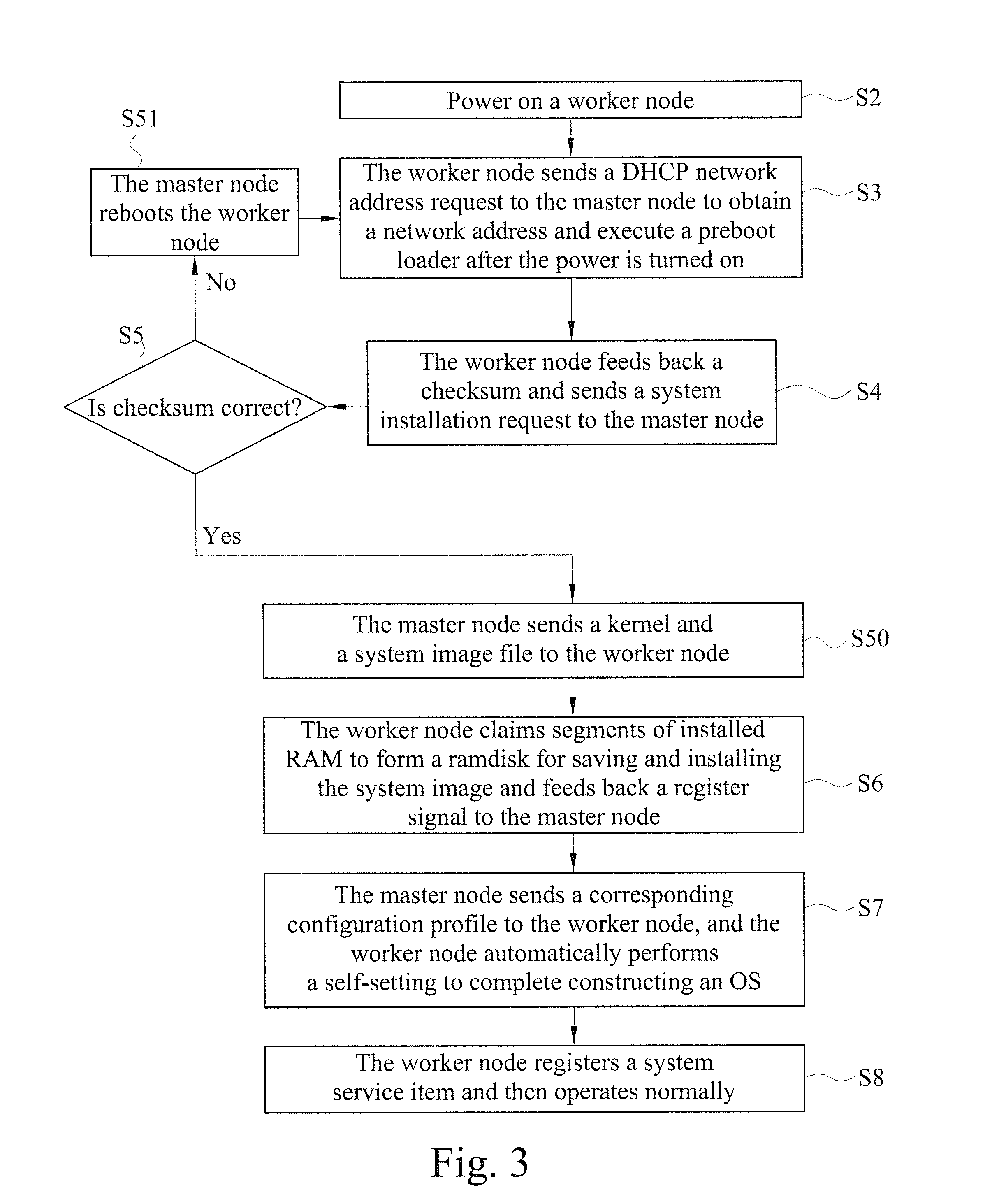

Fast and automatic deployment method for cluster system

InactiveUS20140053149A1Improve efficiencyLong service lifetime for pumpProgram loading/initiatingMemory systemsCluster systemsOperating system

Disclosed is a fast and automatic deployment method for a cluster system by using a ramdisk. A master node is provided for sending a kernel and a system image file after pre-booting at least one worker node in a cluster system via a network. The worker node claims segments of installed RAM to form a ramdisk and buffer the system image file, and after the kernel is executed to install the system image file, a register signal is sent to the master node to request a configuration profile, and related service setup and OS installation are completed by self-setting. Therefore, the fast reading property of the RAM expedites the effect of building and automatically deploying the entire cluster system to simplify the construction complexity and maintenance effort and operation costs.

Owner:ETU

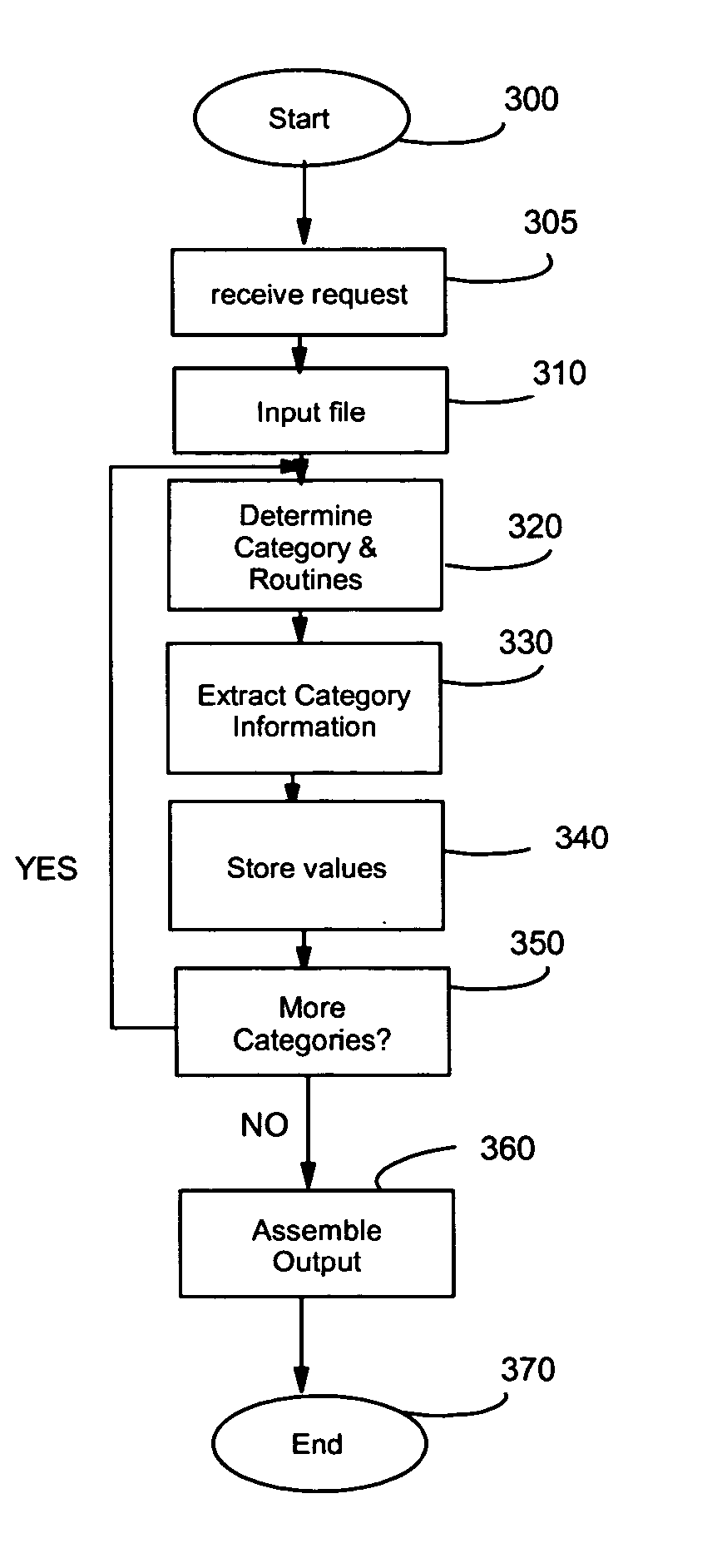

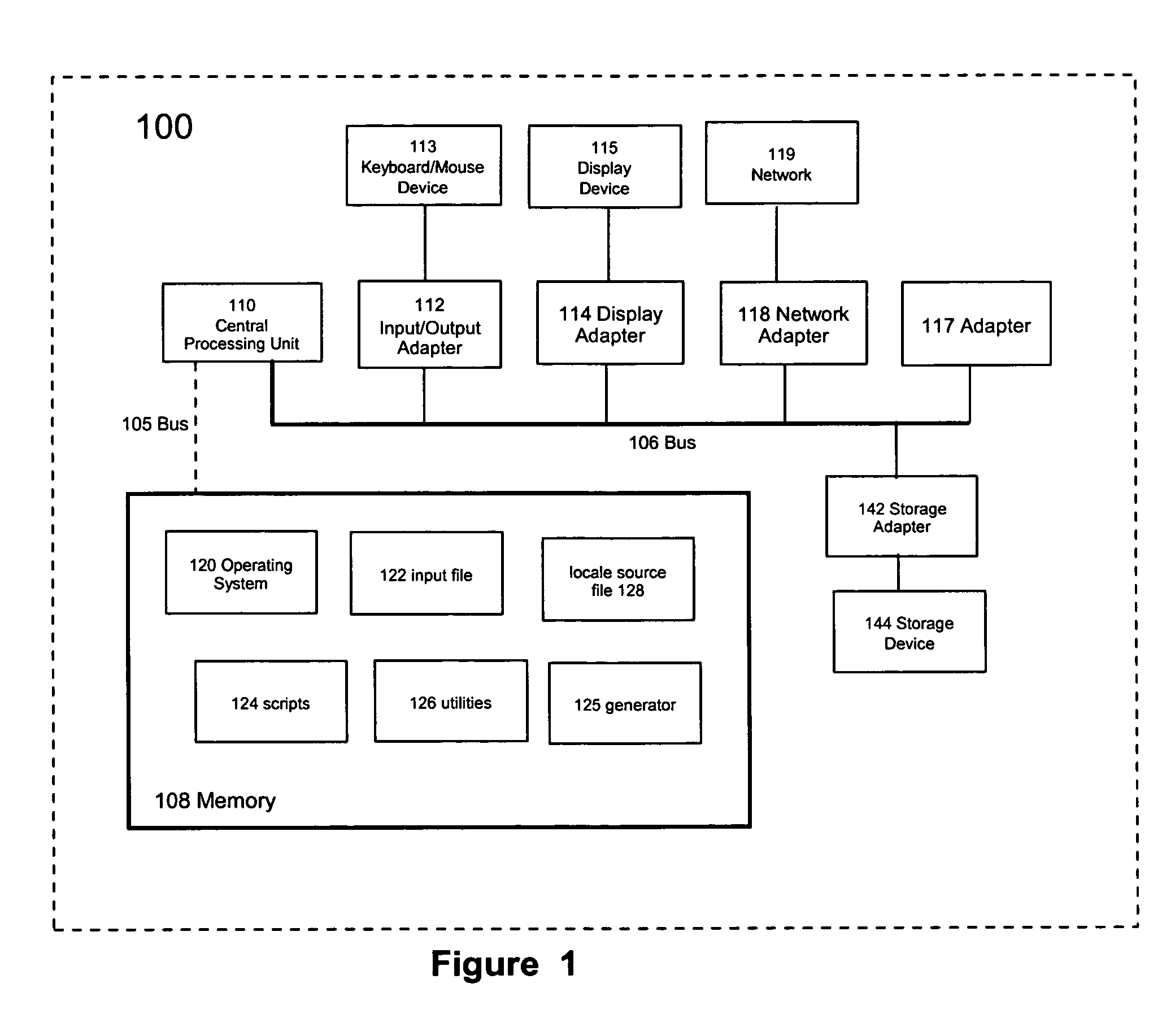

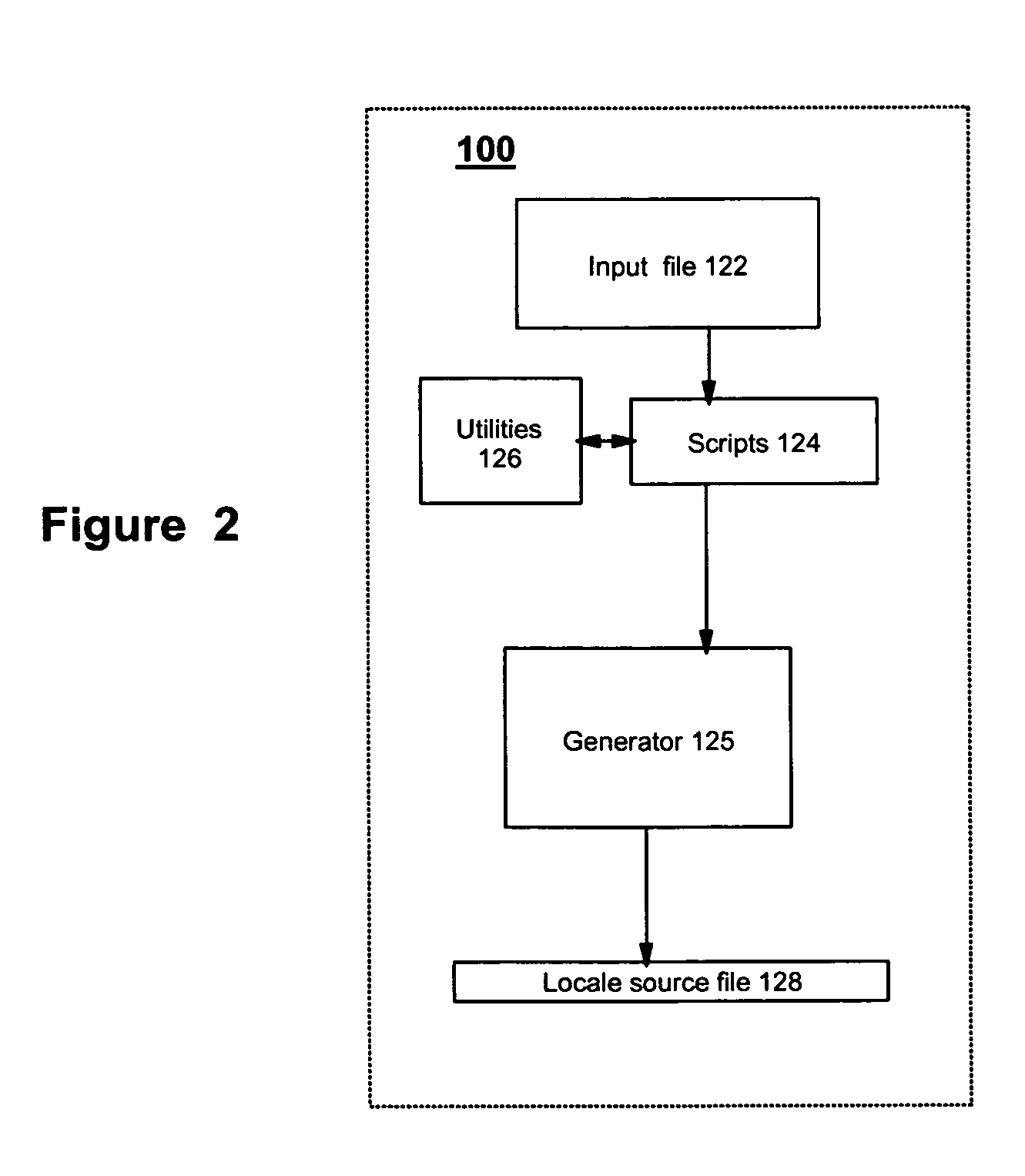

On-demand creation of Java locale source

InactiveUS20050137846A1Natural language data processingExecution for user interfacesJavaSoftware engineering

A method, system, program product and signal bearing medium are provided for creating a specific Java style locale source file on demand in a computer suitable for application use. In particular the method comprises receiving a request submitted for the specific Java style locale and obtaining a plurality of localization values related to the specific Java style locale. Next operation determines a category containing elements therein within the plurality of localization values and selecting process routines dependent upon the category and the element therein. The method continues by selectively extracting the localization values pertaining to the category by the selected routines and storing the extracted localization values into a memory of the computer. The method completes with assembling the extracted information into the Java style locale source file for application use. The method further comprises determining additional categories, for each additional category, selecting process routines dependent upon the additional category containing elements therein, and selectively extracting the localization values pertaining to the additional category and the elements therein by the selected process routines; and the storing of the extracted localization values into a memory of the computer.

Owner:IBM CORP

Multithreading hard real-time control method based on Linux

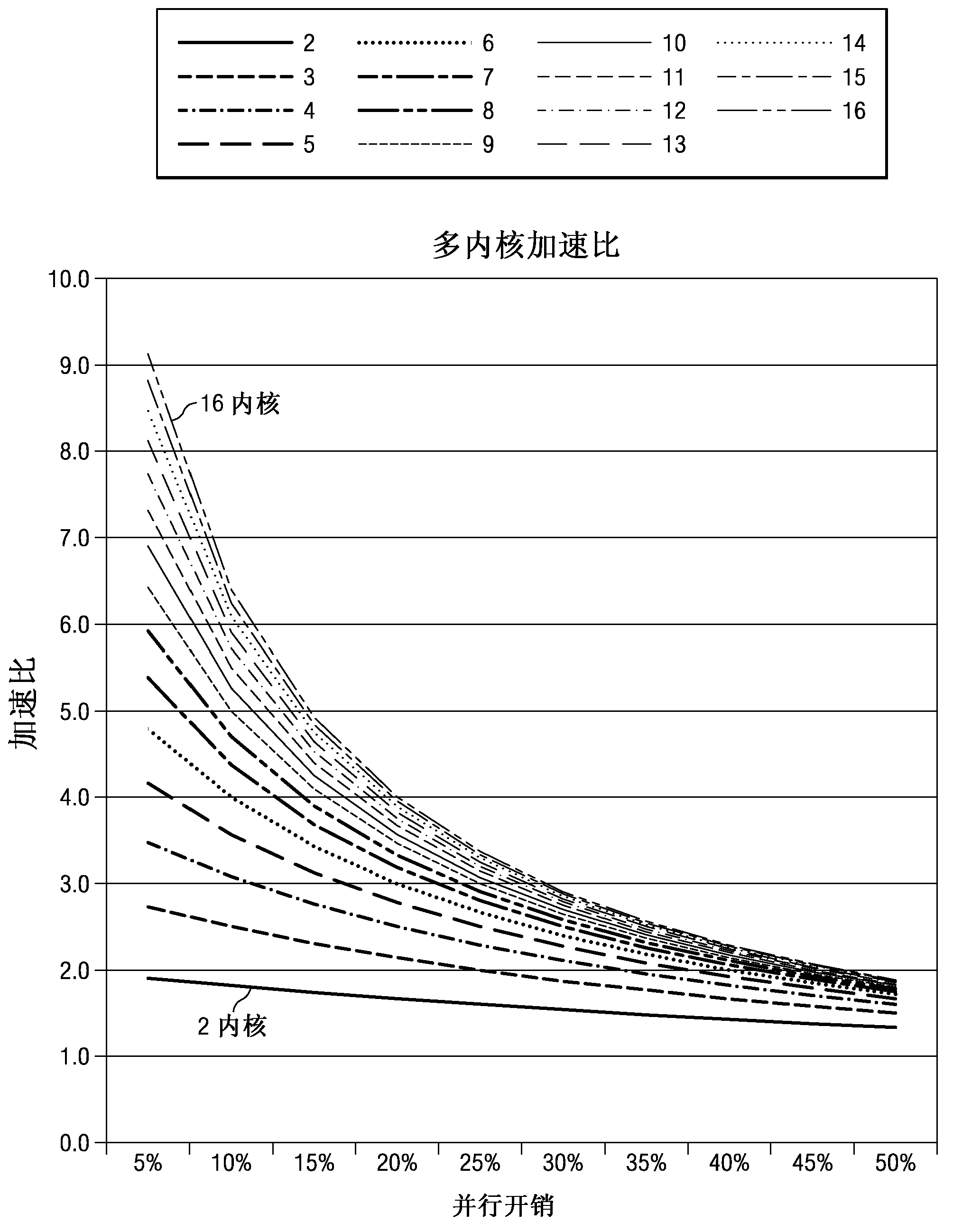

ActiveCN103345422ATo achieve the purpose of real-time controlMeet the requirements of hard real-timeMultiprogramming arrangementsParallel computingInit

The invention discloses a multithreading hard real-time control method based on Linux. The multithreading hard real-time control method based on Linux comprises the following steps that step 1, an overall situation mutual exclusion lock is defined and initialized; step 2 a master control thread and a controlled thread are created; step 3, a mutual exclusion lock is applied in the master control thread and signal registration is conducted in the controlled thread; step 4, the master control thread is monitored in real time, whether the controlled thread needs to be suspended or not by the master control thread in real time is detected, if the answer is positive, a step 5 is conducted; if the answer is negative, whether the controlled thread needs to be recovered or not by the master control thread is detected, and if the answer is positive, a step 6 is conducted; if the answer is negative, the step 4 is conducted in a circulating mode; step 5, the master control thread conducts the operation of suspending the controlled thread and the step 4 is conducted; step 6, the controlled thread is recovered by the master control thread; step 7, a mutual exclusion lock is applied again by the master control thread and the step 4 is conducted. The high priority of signal transmission and the characters of the mutual exclusion locks are used, so that the purposes that the controlled thread is suspended in real time and recovered in real time are achieved, and the requirement for hard real time is satisfied.

Owner:XIAMEN YAXON NETWORKS CO LTD

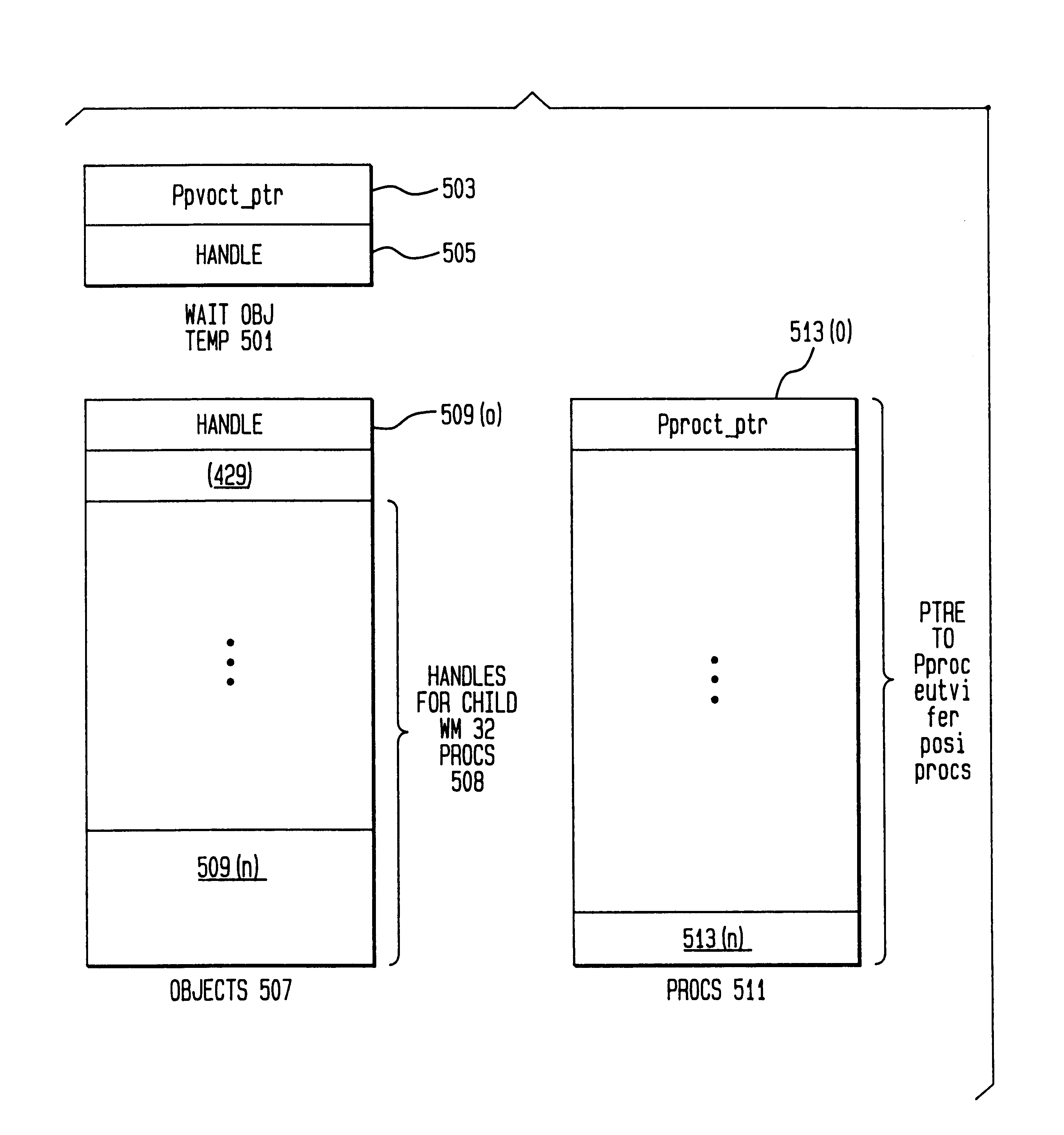

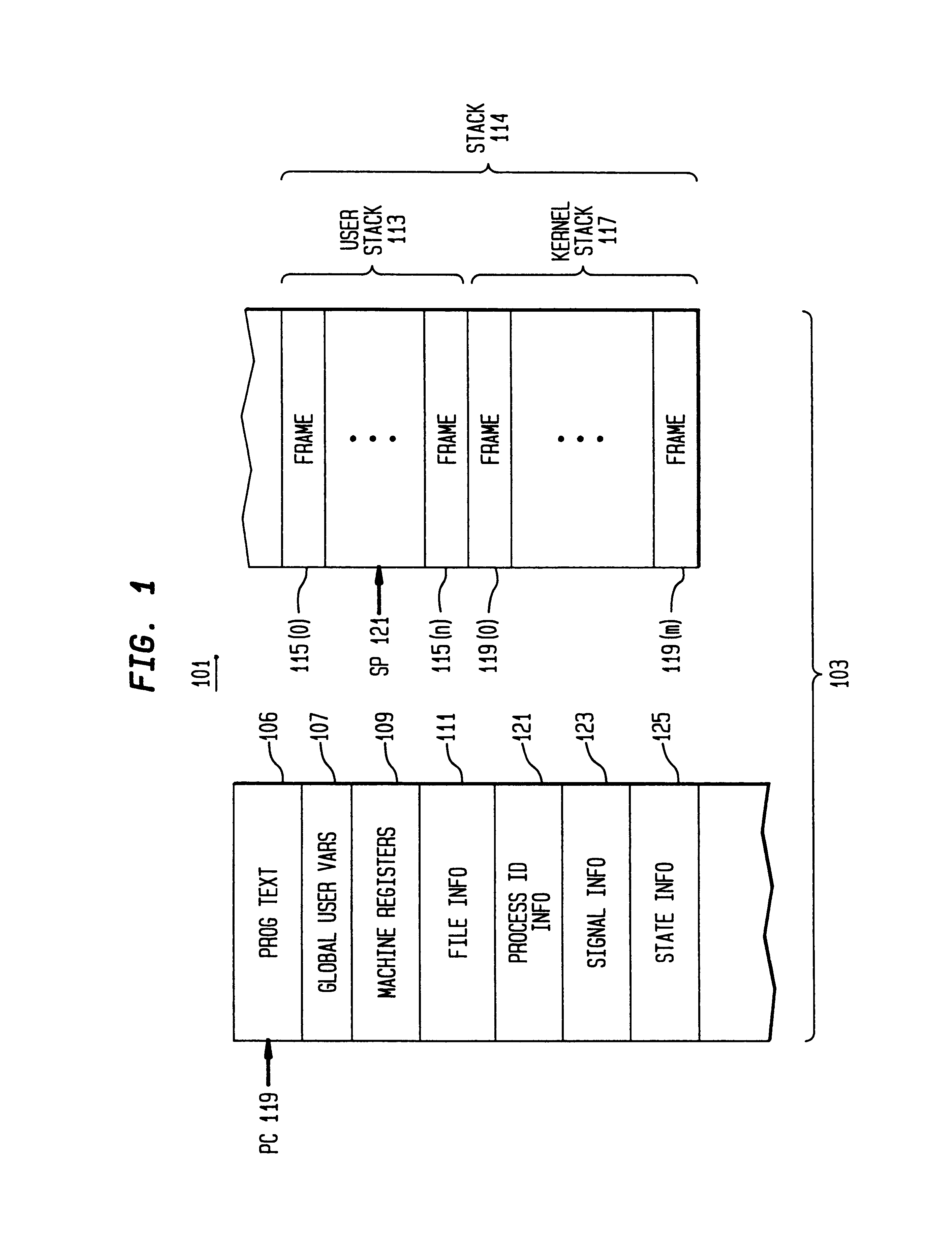

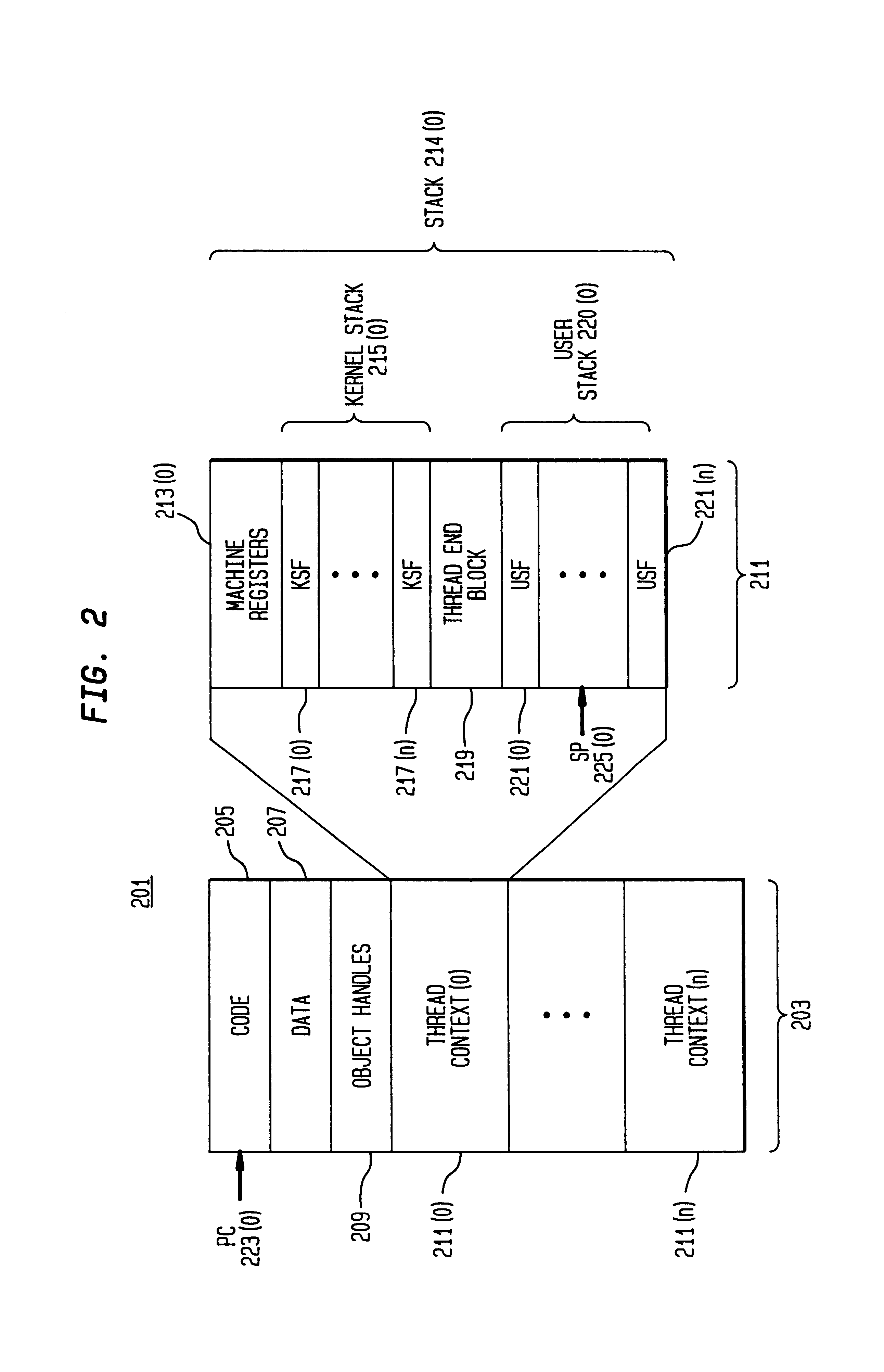

Porting POSIX-conforming operating systems to Win32 API-conforming operating systems

InactiveUS6708194B1Multiprogramming arrangementsProgram code adaptionOperational systemSignal processing

Techniques for porting operating systems of a first class whose representatives include operating systems implementing the POSIX standard to operating systems of a second class whose representatives include operating systems implementing the Win32 API. Processes belonging to operating systems of the first class are characterized by a single thread, parent-child relationships, and signal handlers that execute on the top of the stack; processes belonging to operating systems belonging to the second class have multiple threads, do not have parent-child relationships and do not necessarily execute their signal handlers at the top of the stack. Techniques are disclosed for implementing signal handling as required for operating systems of the first class and providing a signal to a parent process of the first class when one of its child processes terninates. Processes of the second class adapted for implementing processes of the first class are disclosed, as well as implementations of the POSIX fork and exec functions using those processes.

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

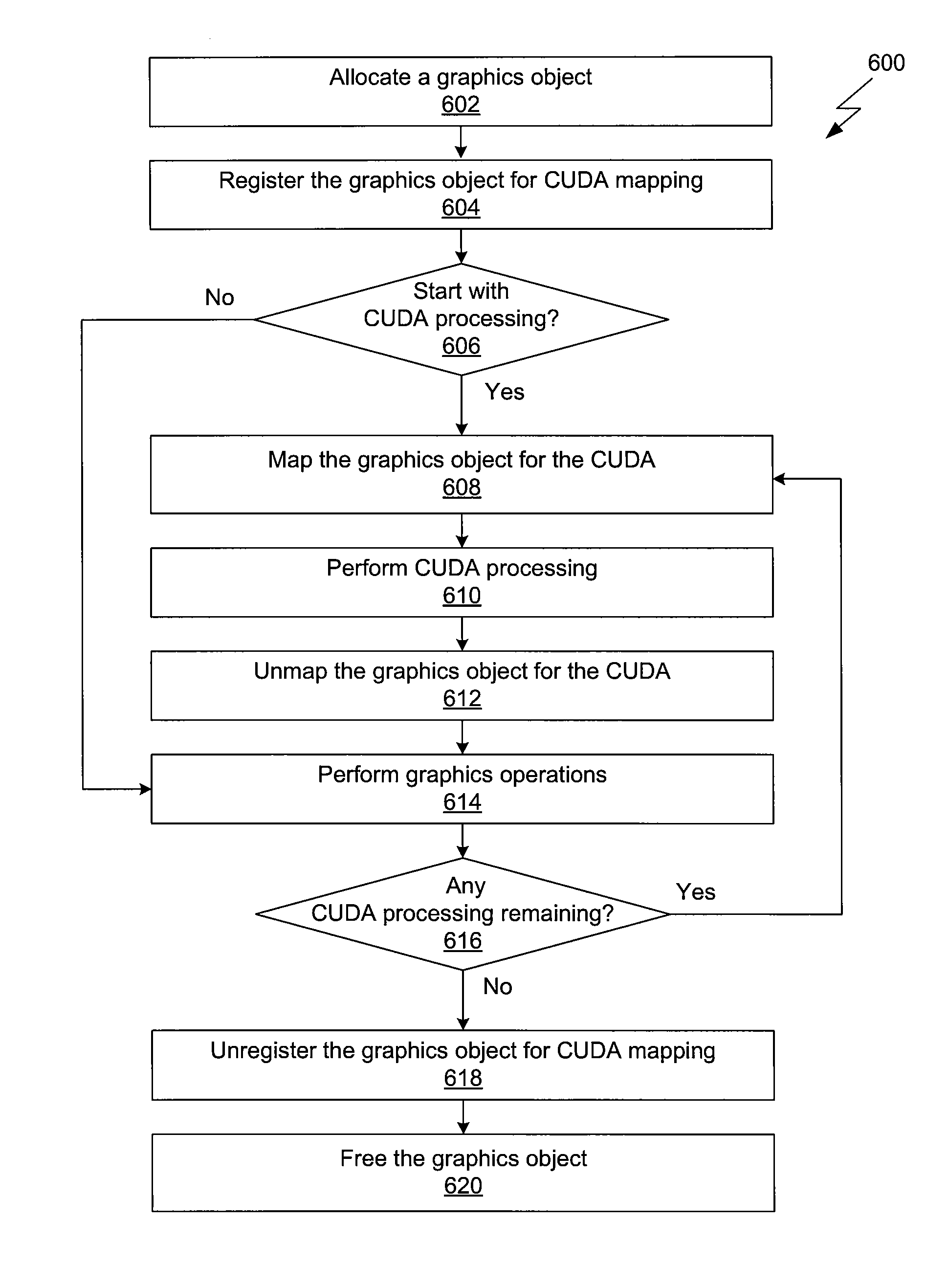

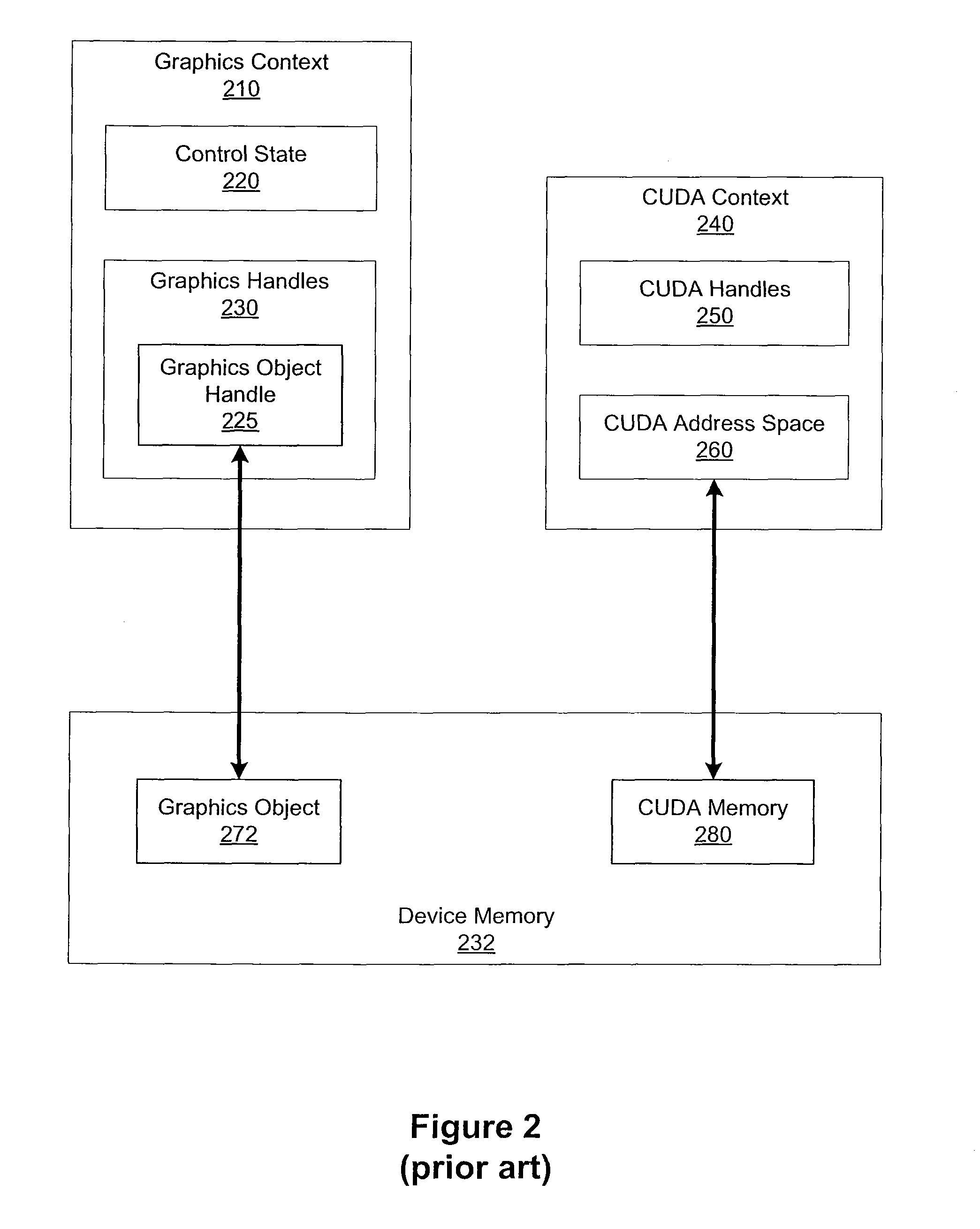

System and method for enabling interoperability between application programming interfaces

ActiveUS8402229B1Effectively ensureCathode-ray tube indicatorsMemory systemsGraphicsInteroperability

One embodiment of the present invention sets forth a method for sharing graphics objects between a compute unified device architecture (CUDA) application programming interface (API) and a graphics API. The CUDA API includes calls used to alias graphics objects allocated by the graphics API and, subsequently, synchronize accesses to the graphics objects. When an application program emits a “register” call that targets a particular graphics object, the CUDA API ensures that the graphics object is in the device memory, and maps the graphics object into the CUDA address space. Subsequently, when the application program emits “map” and “unmap” calls, the CUDA API respectively enables and disables accesses to the graphics object through the CUDA API. Further, the CUDA API uses semaphores to synchronize accesses to the shared graphics object. Finally, when the application program emits an “unregister” call, the CUDA API configures the computing system to disregard interoperability constraints.

Owner:NVIDIA CORP

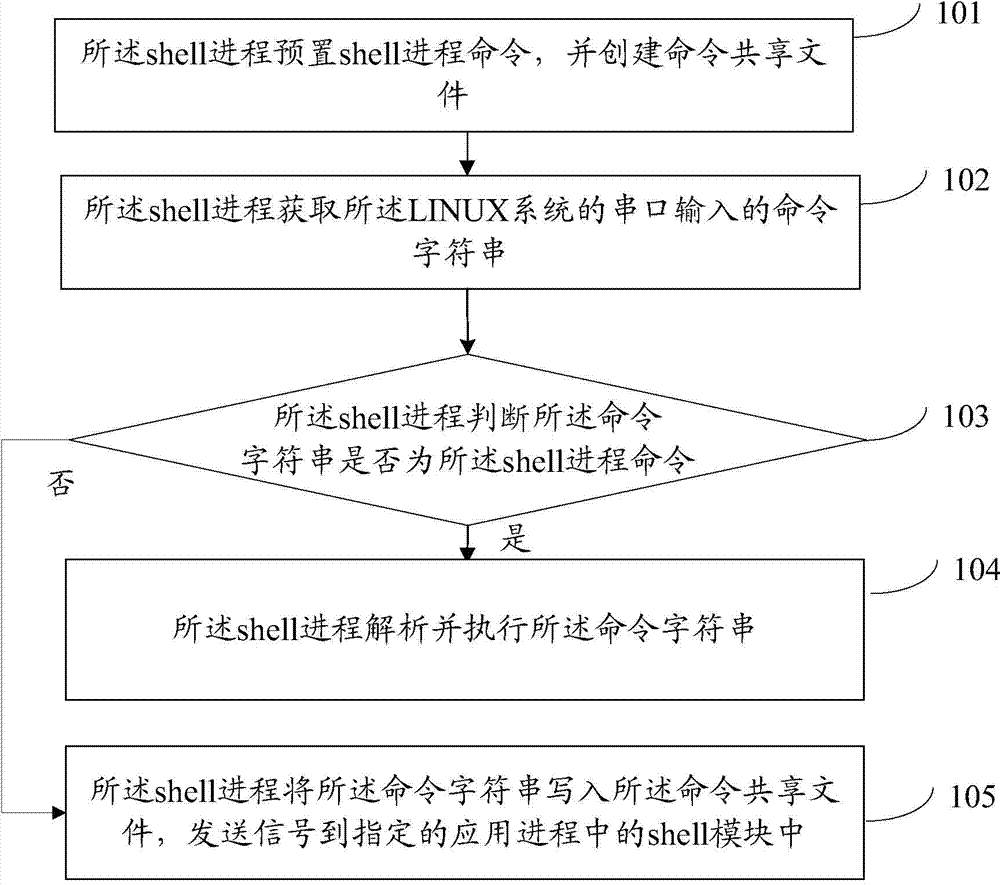

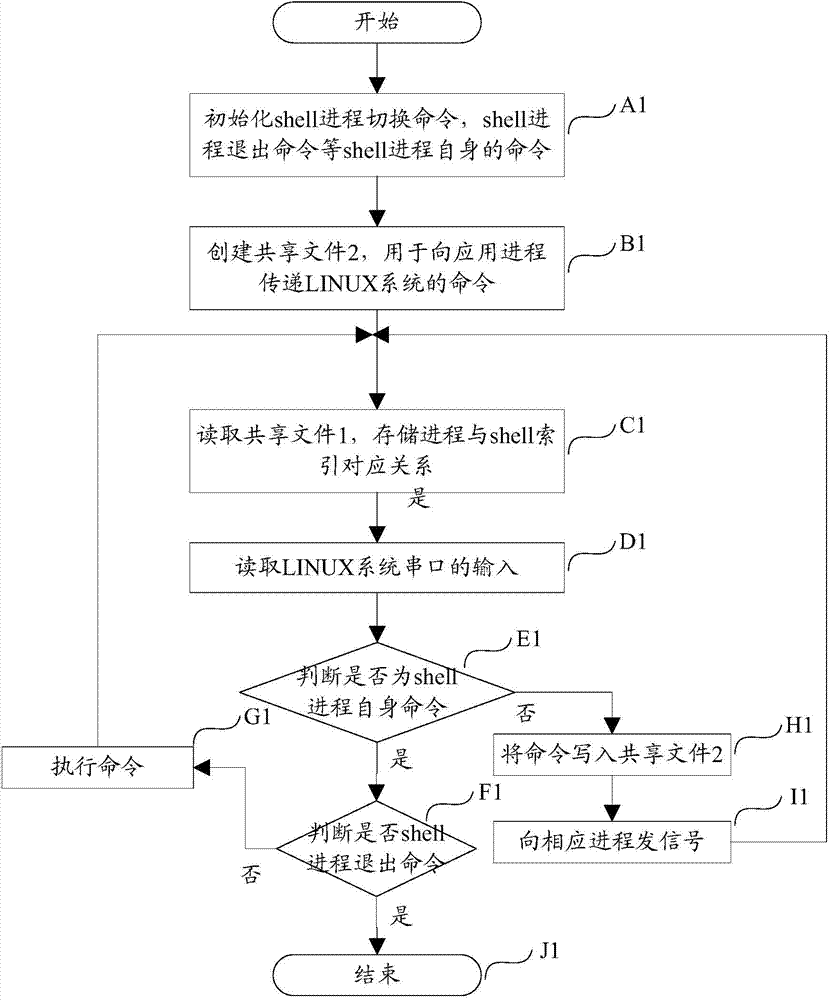

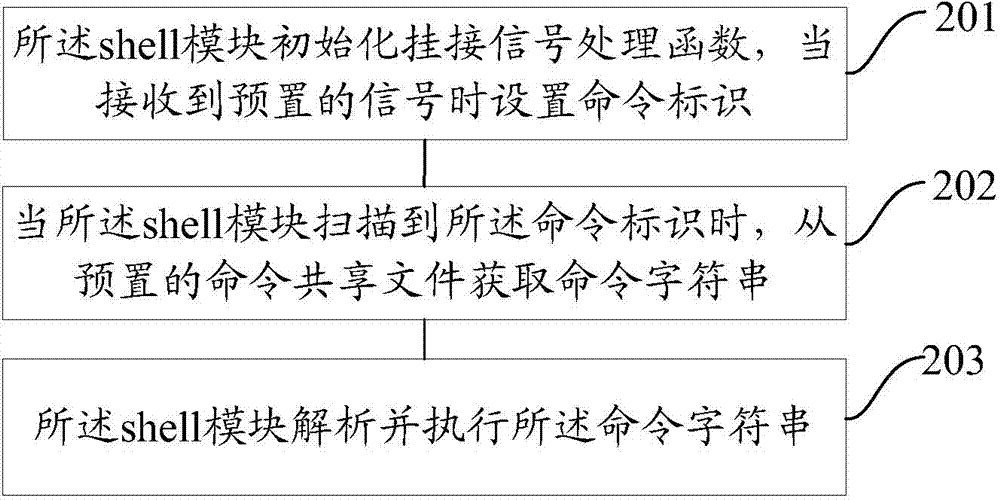

Method and device for processing application process commands in Linux system

ActiveCN103593239AImprove real-time performanceReduce resource usageProgram initiation/switchingSpecific program execution arrangementsGNU/LinuxComputer module

The invention provides a method and a device for processing application process commands in a Linux system. In an application progress in the Linux system, threads are increased and a shell module is generated; a shell progress is introduced into the Linux system; the shell progress interacts with the shell module in the application progress. The method includes pre-setting a shell progress command and creating a command shared file by the shell progress; acquiring a command string input from a serial port of the Linux system by the shell progress; judging whether the command string is a shell progress command or not by the shell progress; if yes, analyzing and executing the command string by the shell progress, and if not, writing the command string into the command shared file and sending a signal to the shell module in the designated application progress by the shell progress; acquiring the command string from the command shared file by the shell module after receiving the signal. By the method and the device, execution conditions of the application progress can be checked at any time under the condition that normal operation of the application progress is not affected.

Owner:DATANG MOBILE COMM EQUIP CO LTD

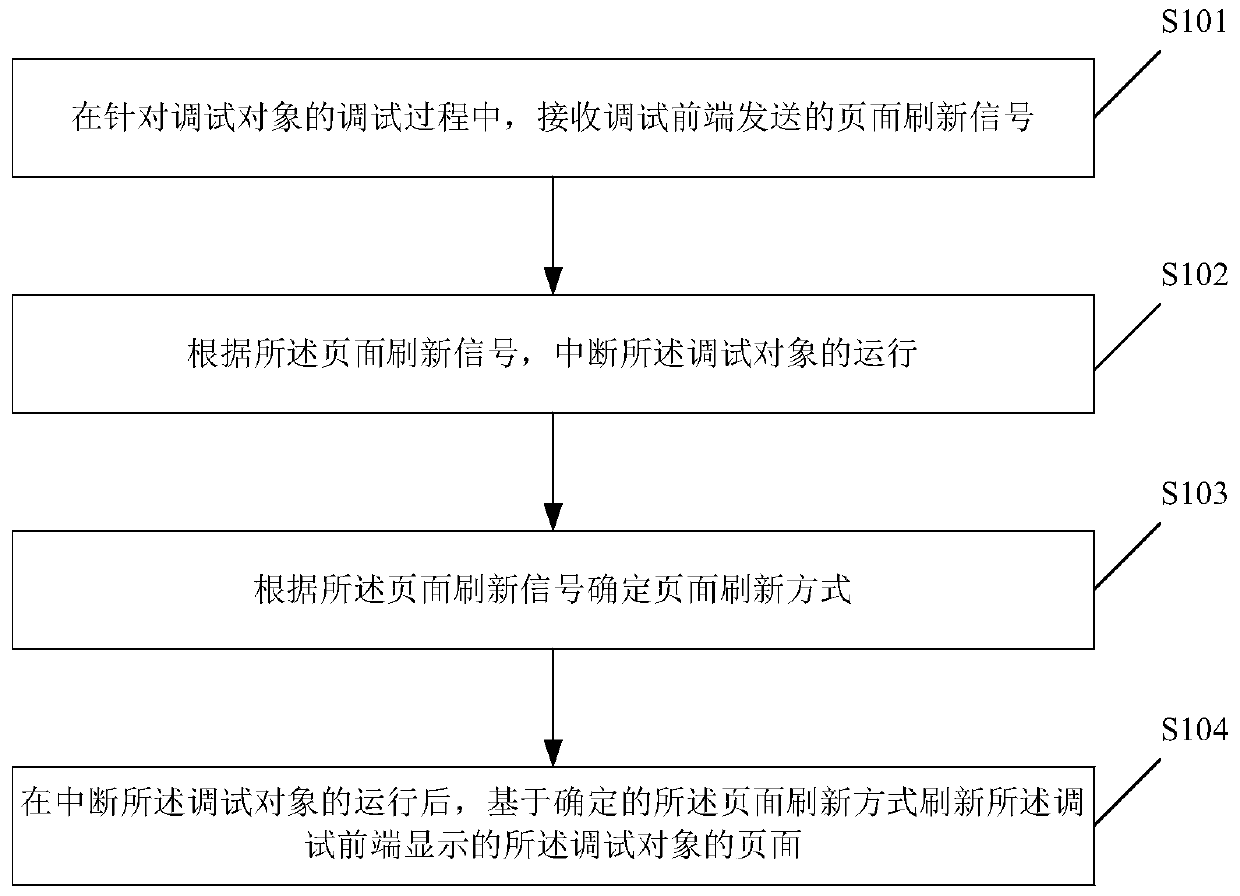

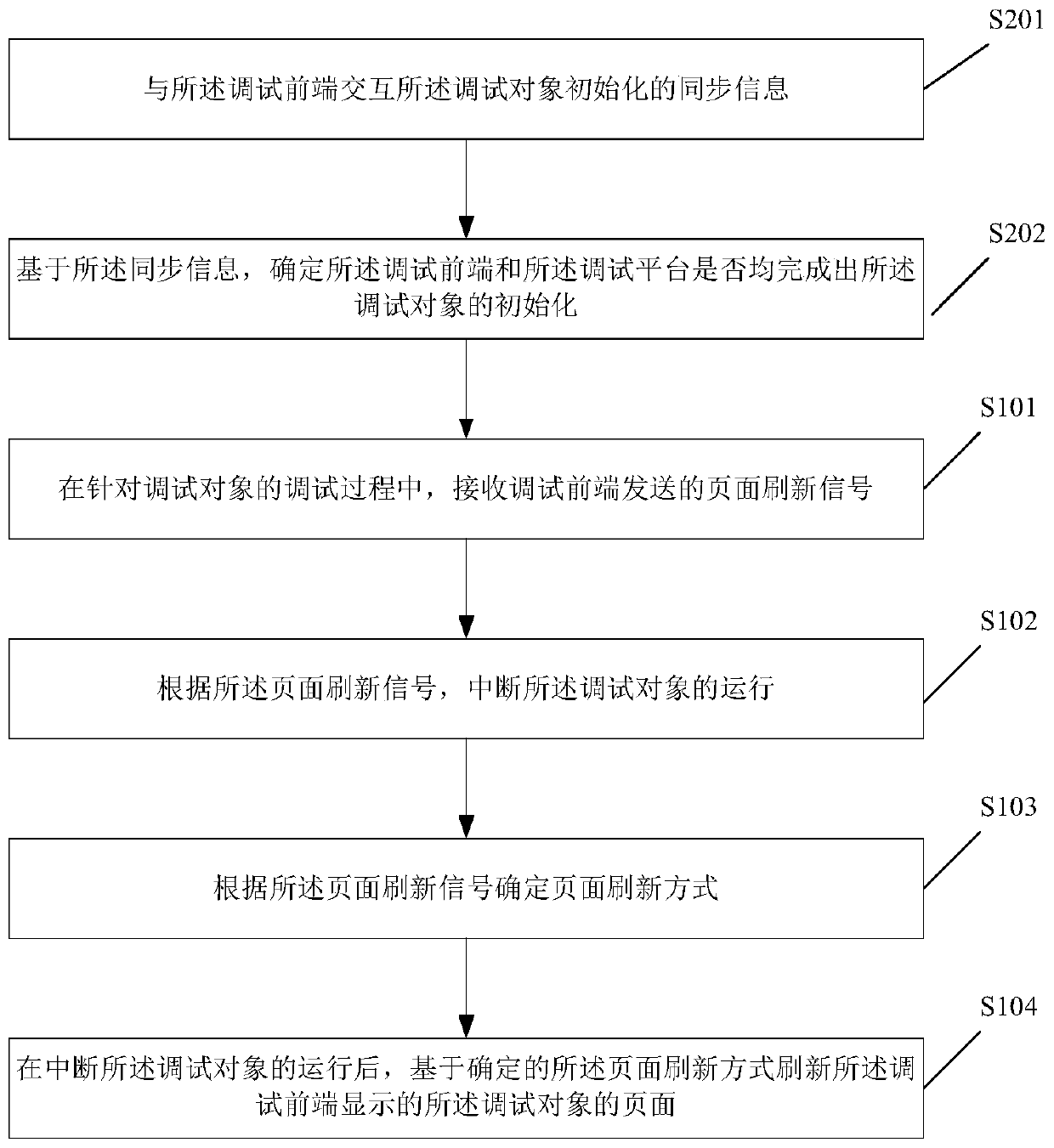

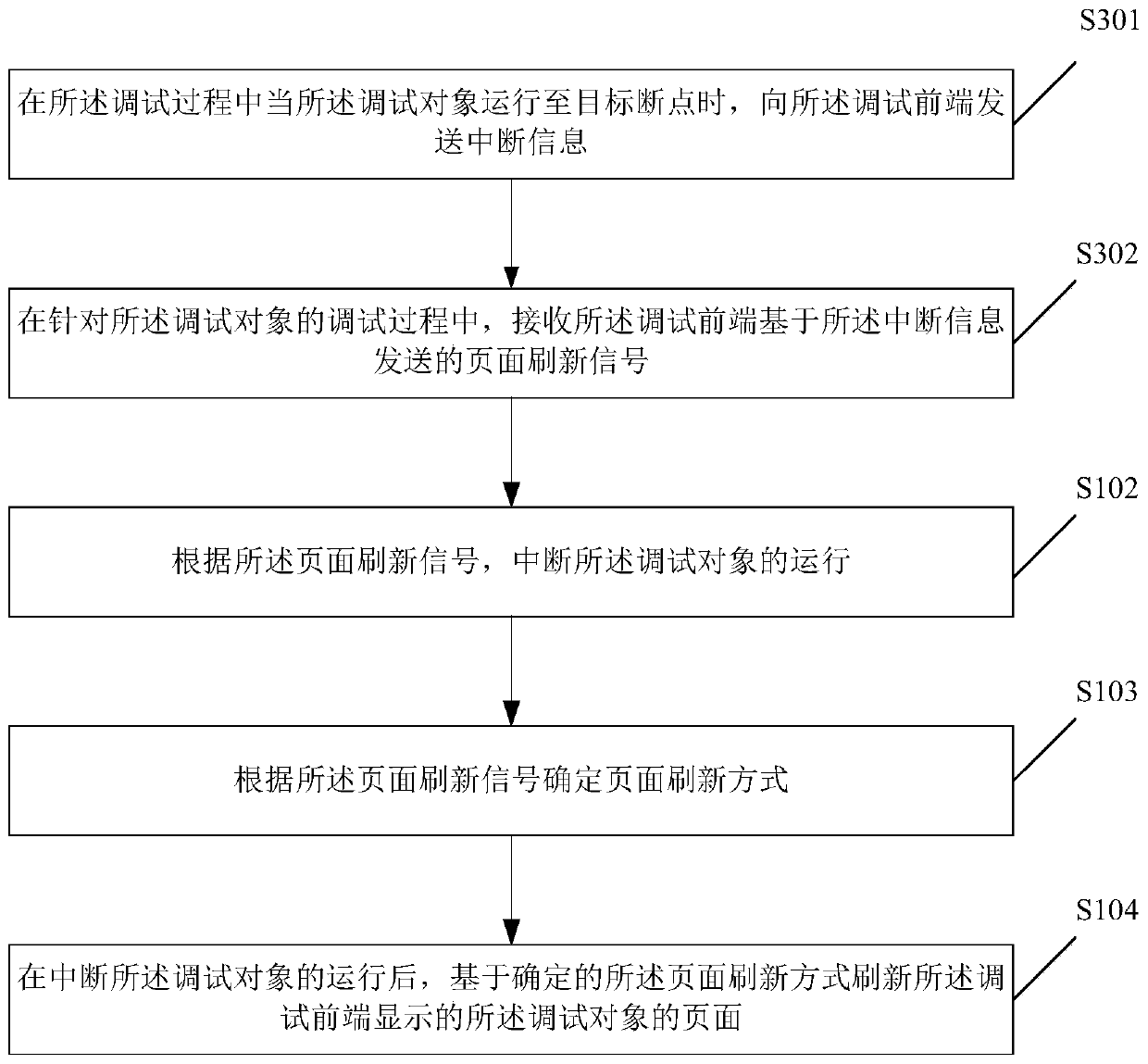

Program debugging method and device and storage medium

ActiveCN110781080AImprove debugging efficiencyProgram initiation/switchingSoftware testing/debuggingProgramming languageEngineering

The invention relates to a program debugging method and device and a storage medium. The method comprises the steps of in the debugging process of a debugging object, receiving a page refreshing signal sent by a debugging front end wherein the debugging object comprises a fast application and / or a small program; interrupting the operation of the debugging object according to the page refreshing signal; determining a page refreshing mode according to the page refreshing signal; and after the operation of the debugging object is interrupted, refreshing the page of the debugging object displayedby the debugging front end based on the determined page refreshing mode. According to the technical scheme, different refreshing modes are provided for selection, the debugging front end and the debugging platform do not need to be restarted when the page is refreshed each time, and therefore the debugging efficiency is improved.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

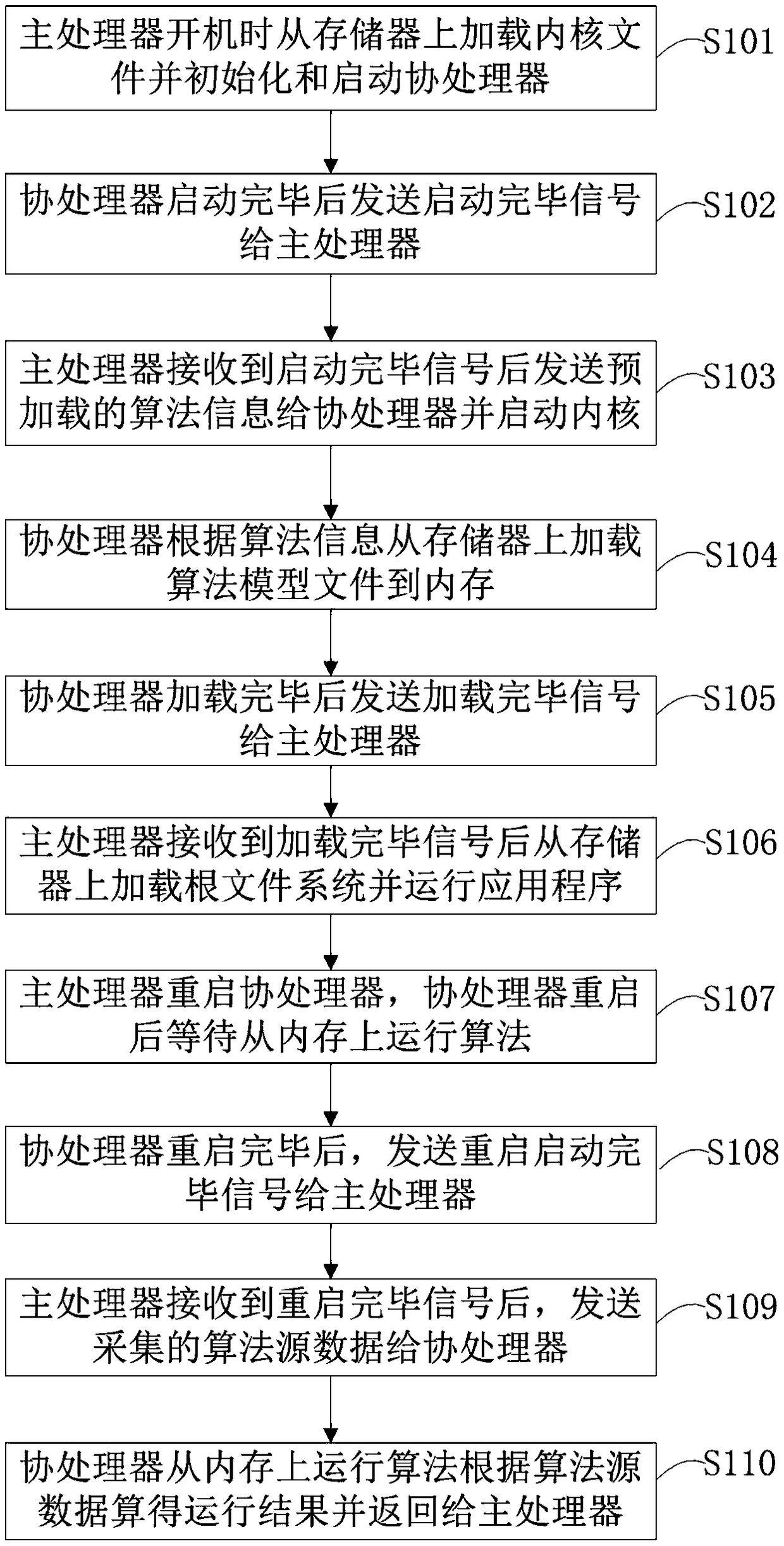

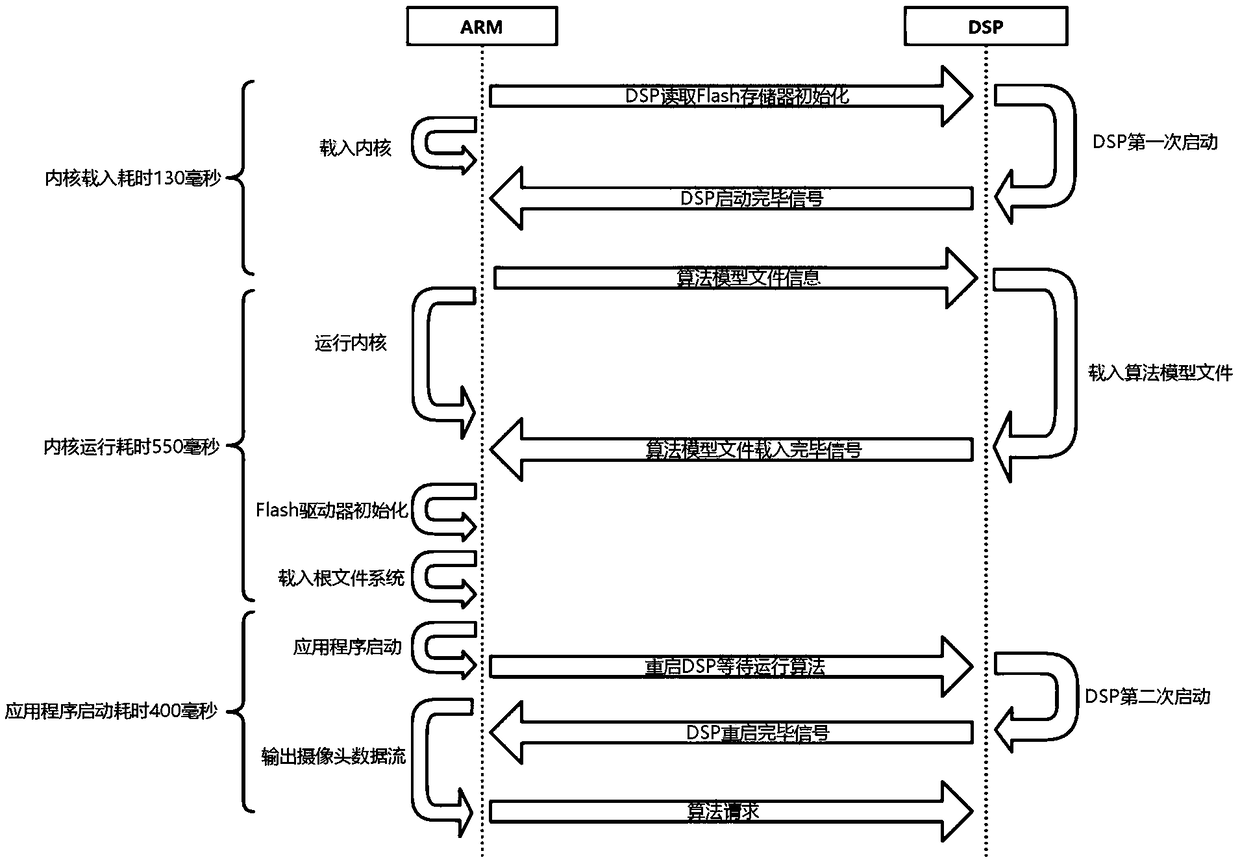

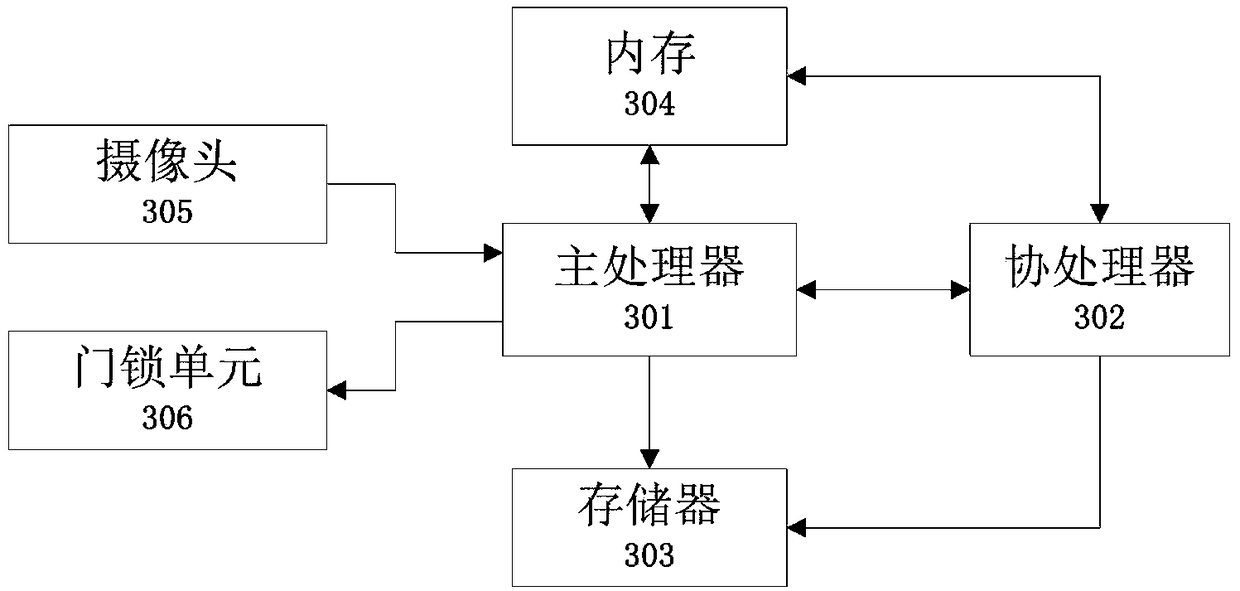

A method and a device for quickly starting a machine

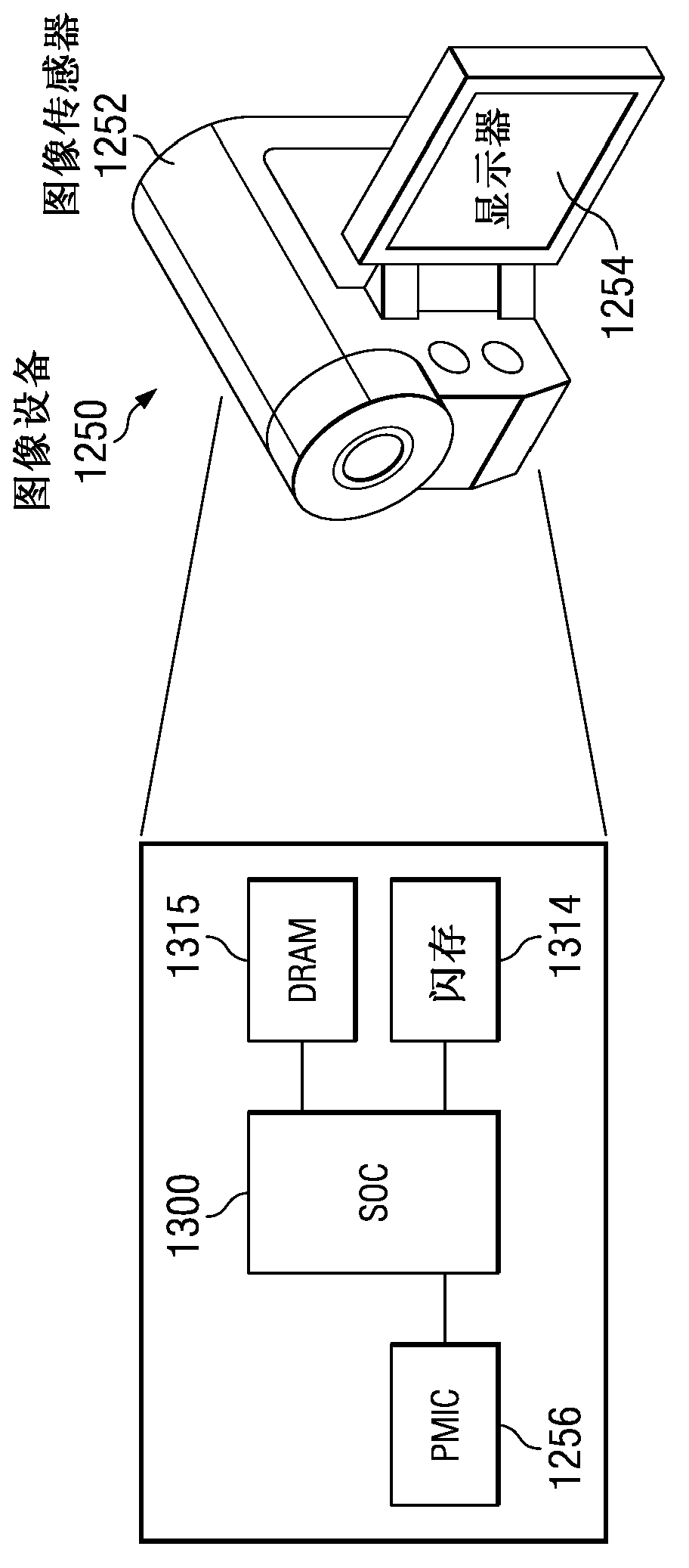

ActiveCN109460260AAchieve normal operationSolve the problem of long boot timeCharacter and pattern recognitionDigital data authenticationCoprocessorFile system

The invention discloses a method and a device for fast boot-up, which comprises the following steps: after the coprocessor is loaded, a loading complete signal is sent to the main processor; After receiving the loading signal, the main processor loads the root file system from the memory and runs the application program. The main processor restarts the coprocessor, and the coprocessor waits for the algorithm to run on the slave memory after the coprocessor restarts; After the restart of the coprocessor is completed, a restart completion signal is sent to the main processor. After receiving therestart signal, the main processor sends the collected algorithm source data to the coprocessor, and the coprocessor calculates the running result according to the algorithm source data from the memory and returns it to the main processor. In the technical proposal, the algorithm model file is loaded by the coprocessor during the time of loading and running the kernel by the main processor, and then the algorithm can be run after the main processor is turned on, thereby solving the problem that the existing algorithm is loaded again after the kernel is finished, and the boot-up time of the algorithm is long.

Owner:FUZHOU ROCKCHIP SEMICON

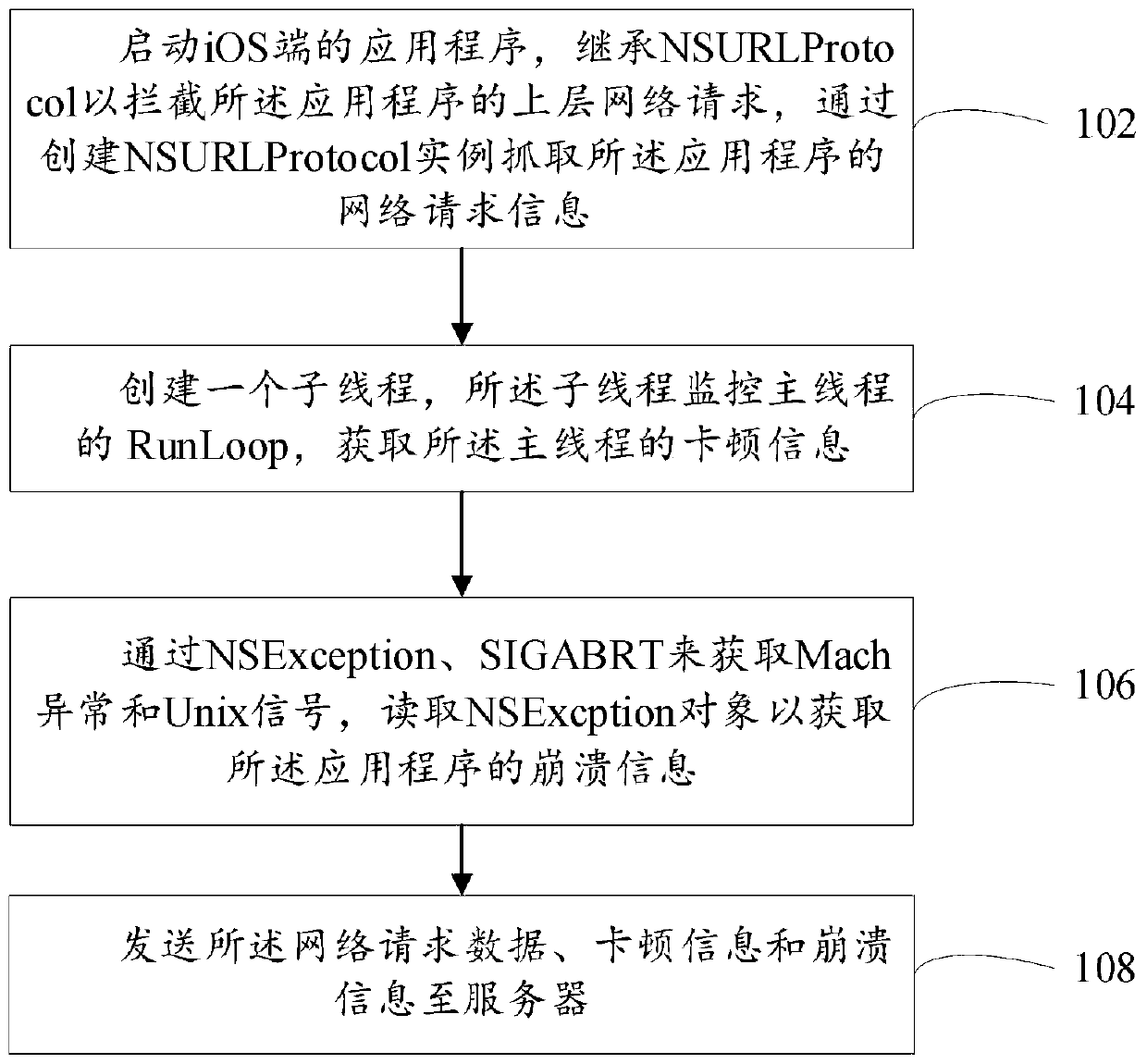

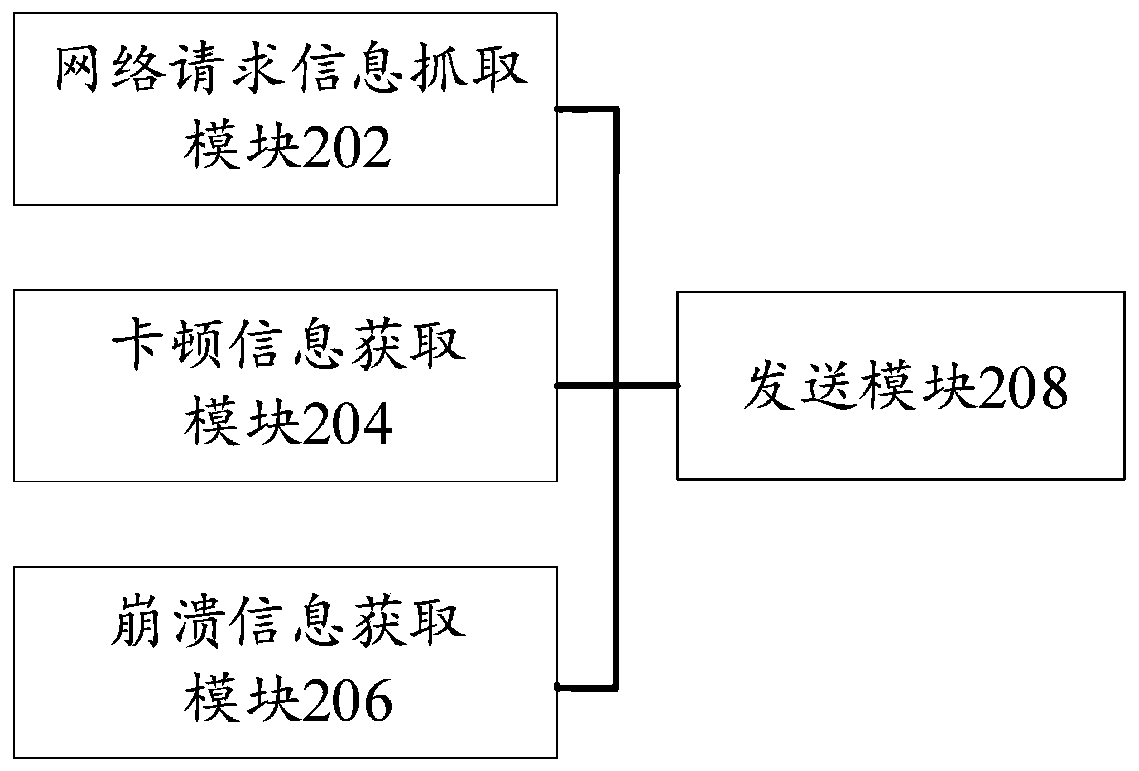

Method and device for monitoring performance of iOS terminal application program

The invention provides a method for monitoring the performance of an iOS terminal application program. The method comprises the steps of starting an application program of an iOS terminal, inheritingthe NSURLProtol to intercept an upper-layer network request of the application program, and capturing the network request information of the application program by creating an NSURLProtol instance; creating a sub-thread, monitoring the RunLoop of the main thread by the sub-thread, and acquiring the lag information of the main thread; acquiring a Mach exception and a Unix signal through NSExceptionand SIGABRT, and reading an NSException object so as to acquire crash information of an application program; and sending the network request data, the lag information and the crash information to a server. According to the invention, the network request information, the crash information and the lagging information can be dynamically obtained, and the real-time monitoring of the performance of the iOS terminal application program is realized.

Owner:北京思特奇信息技术股份有限公司

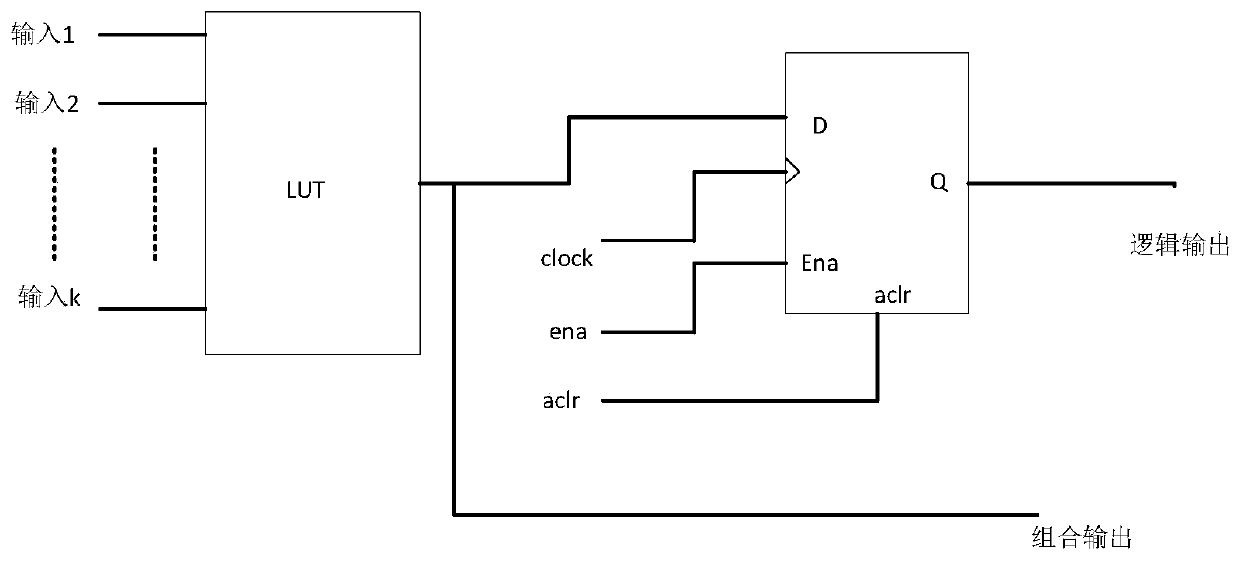

Method and system for automatically generating netlist file for testing software and hardware

ActiveCN111400169AImprove test efficiencyImprove test coverageSoftware testing/debuggingEnergy efficient computingTest efficiencyComputer architecture

The invention discloses a method and a system for automatically generating a netlist file for testing software and hardware, which can effectively improve the testing efficiency of FPGA software, canreduce the technical requirements on testing personnel and can greatly improve the testing coverage rate of the FPGA software. The method comprises the following steps: (1) generating a batch of signals through scripts; (2) performing BLE structure analysis and netlist information establishment; (3) performing IO structure analysis and netlist information establishment; and (4) sequentially writing the related information into the netlist file according to the structural characteristics of the netlist file, and establishing the netlist file.

Owner:EHIWAY MICROELECTRONIC SCI & TECH SUZHOU CO LTD

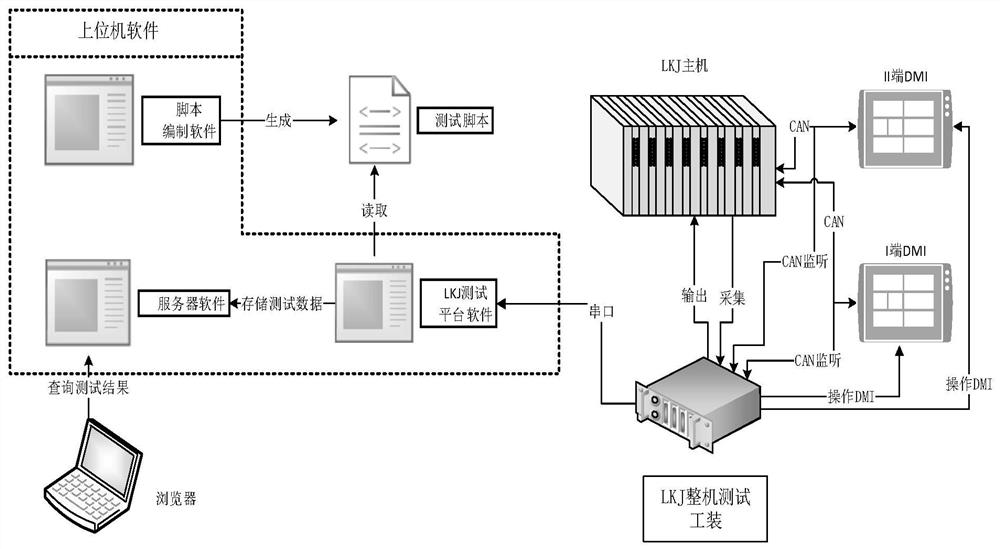

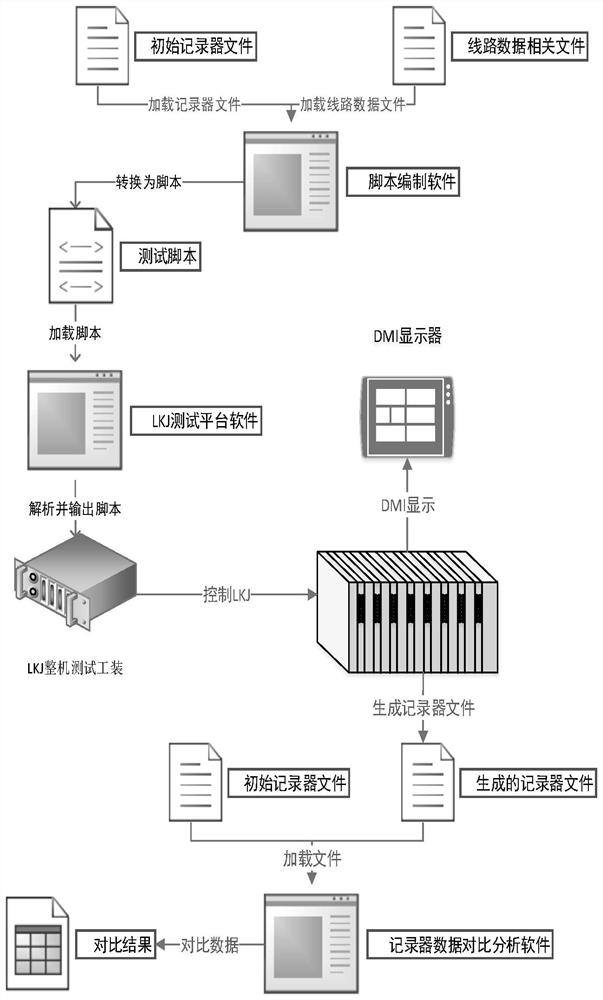

LKJ test system capable of automatically generating test scripts

PendingCN112162916AEasy to prepareImprove test efficiencySoftware testing/debuggingTest scriptDocument transformation

The invention discloses an LKJ test system capable of automatically generating test scripts comprises an LKJ complete machine test tool and upper computer software, the LKJ complete machine test toolis used for outputting signals required by an LKJ host and collecting signals generated by the LKJ host, and the upper computer software comprises script compiling software, LKJ test platform softwareand server software; LKJ test platform software can load the test scripts, analyze the content of the test scripts and send the analyzed test scripts to the LKJ complete machine test tool through a serial port, and the LKJ complete machine test tool drives an LKJ simulation locomotive to operate according to the scripts content to perform automatic test. The invention has the technical advantagesthat the LKJ test system can record manual test steps and convert manual test steps into test scripts, record key operation of DMI of the LKJ and convert the key operation into the test scripts, andan LKJ recorder file is converted into the test scripts. Script compiling and testing efficiency is improved.

Owner:BEIJING JIAODA SIGNAL TECH

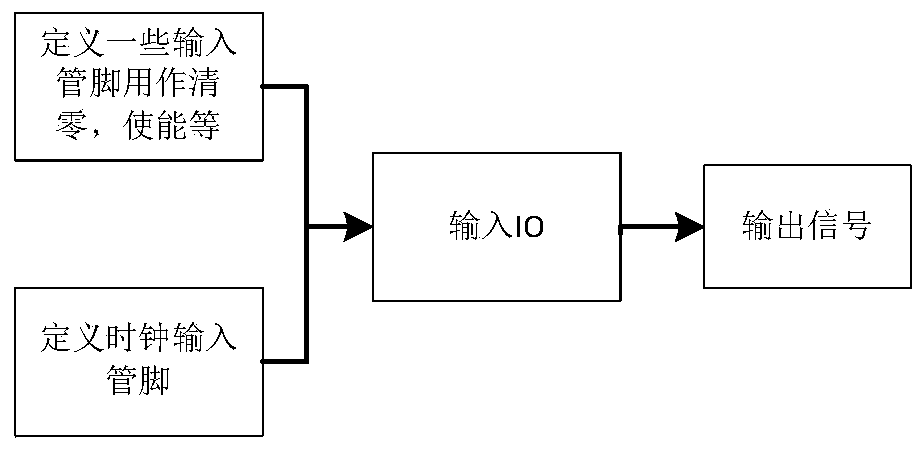

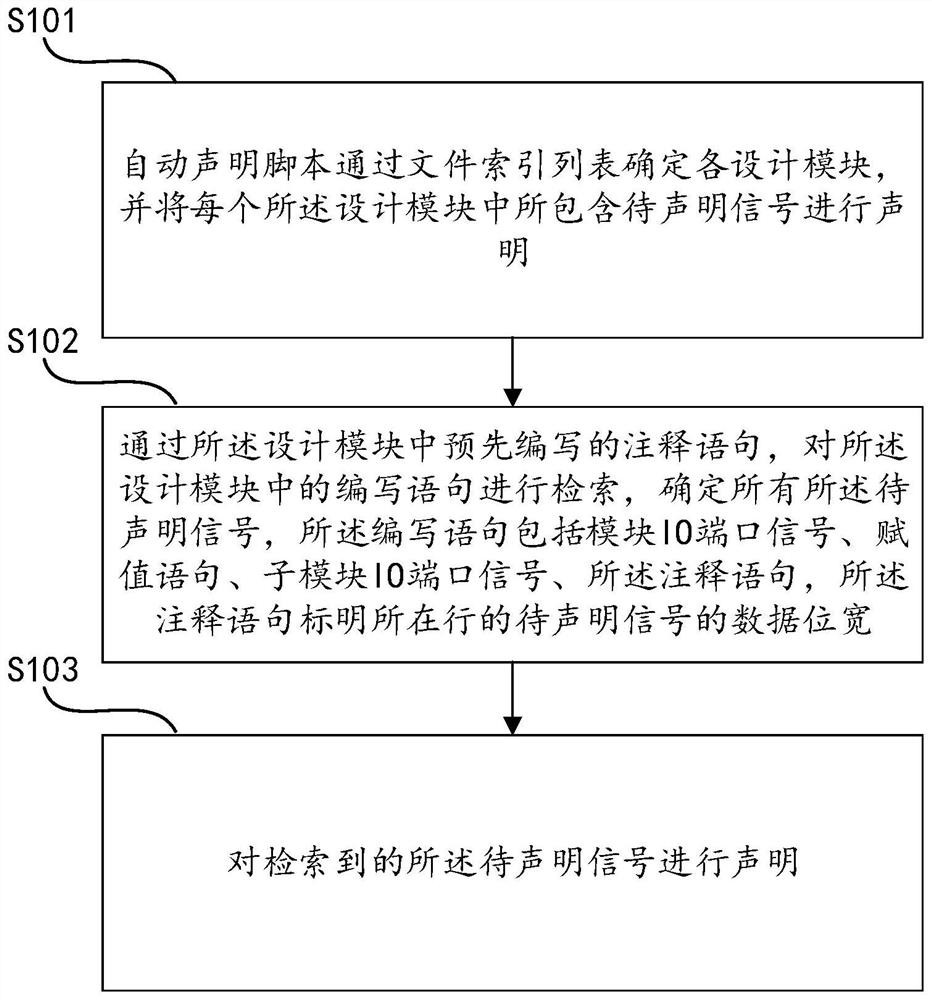

Signal declaration system, method and device in digital logic design and medium

PendingCN112083897AGuaranteed accuracyReduce workloadCode compilationDigital output to print unitsProgramming languageSoftware engineering

The invention discloses a signal declaration system, method and device in digital logic design and a medium, and the system comprises design modules which comprise a corresponding writing statement; afile index list which comprises file names corresponding to the design modules; an automatic declaration script which is used for retrieving writing statements in the design module through annotationstatements and determining all to-be-declared signals, and declaring the retrieved to-be-declared signal. By designing the annotation statement in the module, all signals to be declared can be accurately positioned by using the automatic declaration script, declaration is carried out based on the data bit width in the annotation statement, and the accuracy of the data bit width during signal declaration is ensured. The to-be-declared signals of each design module in the design engineering are automatically declared, so that the workload of developers is reduced. And when the related design inthe design module is changed, the declaration of each signal can be completed only by running the automatic declaration script again, so that the method is very convenient.

Owner:JINAN INSPUR HIGH TECH TECH DEV CO LTD

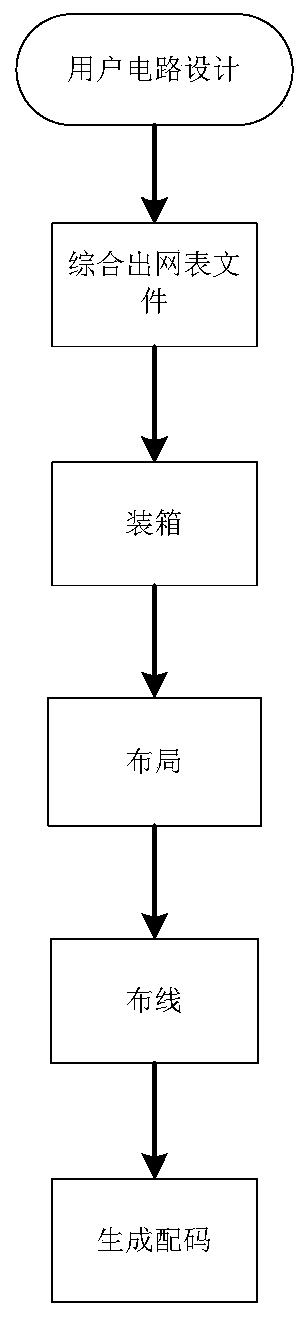

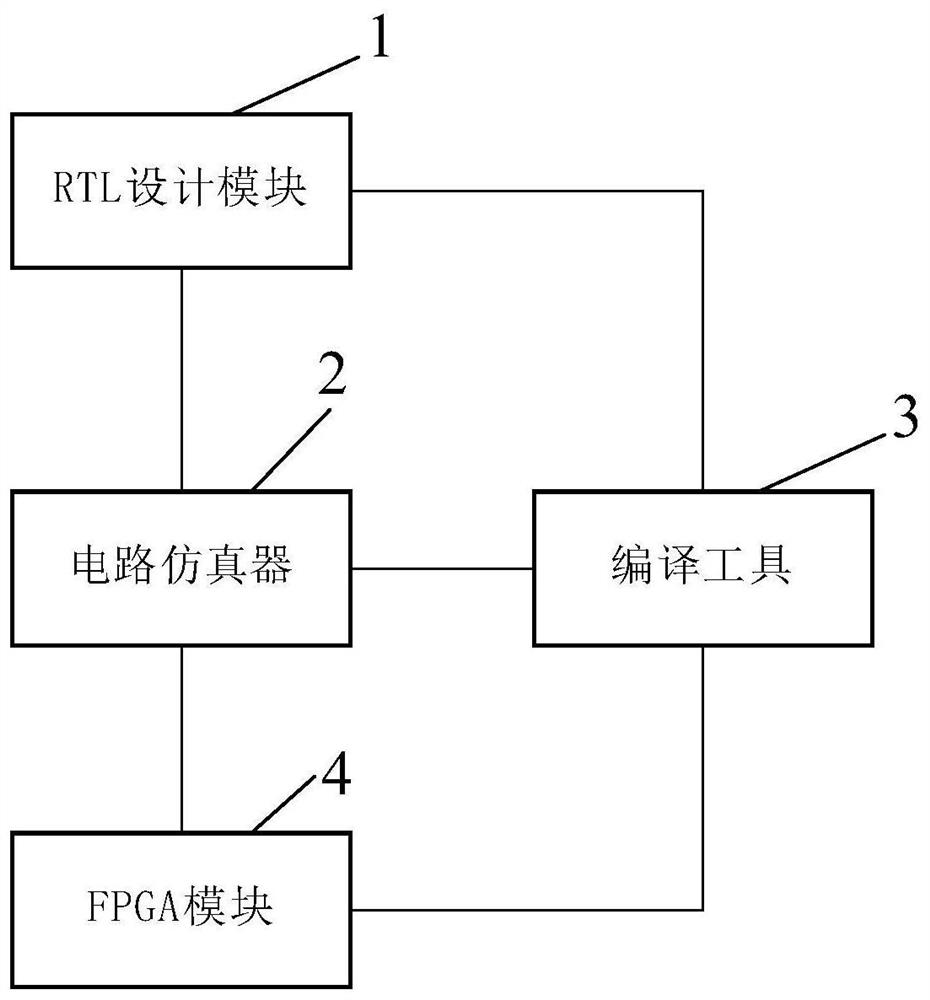

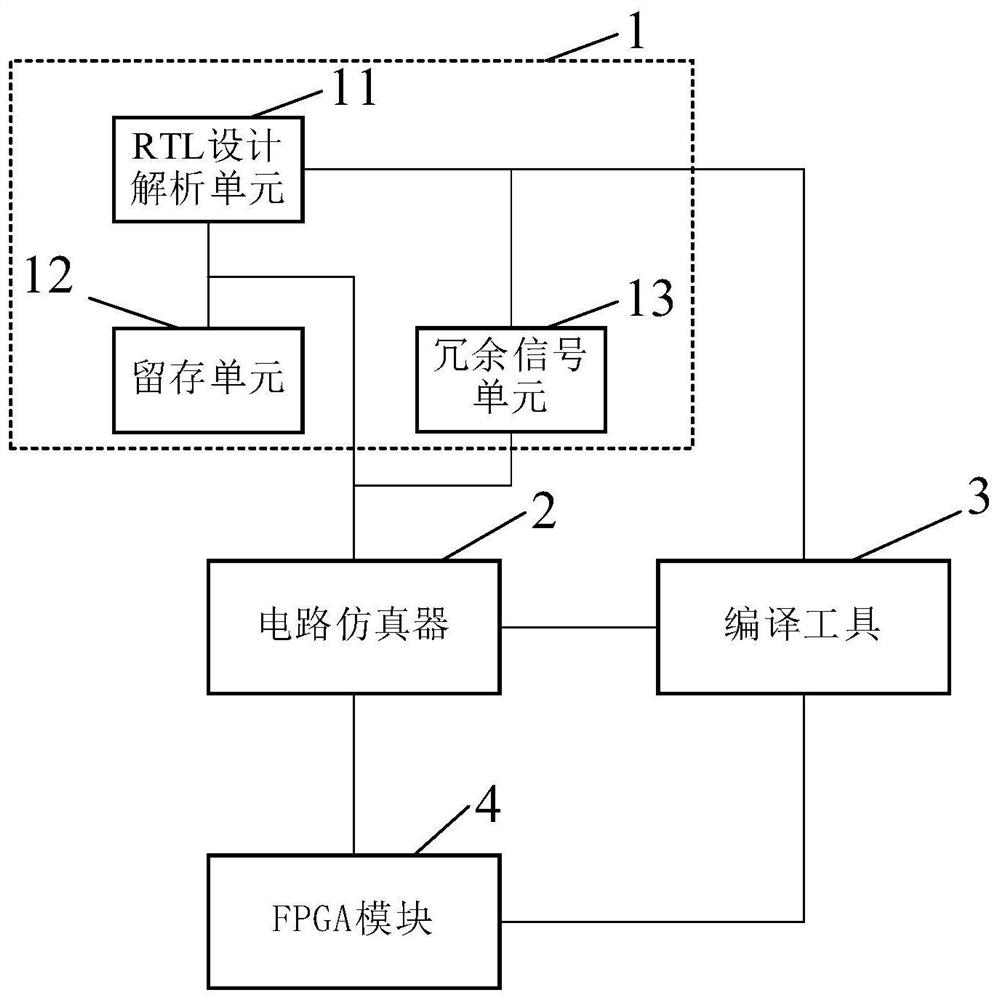

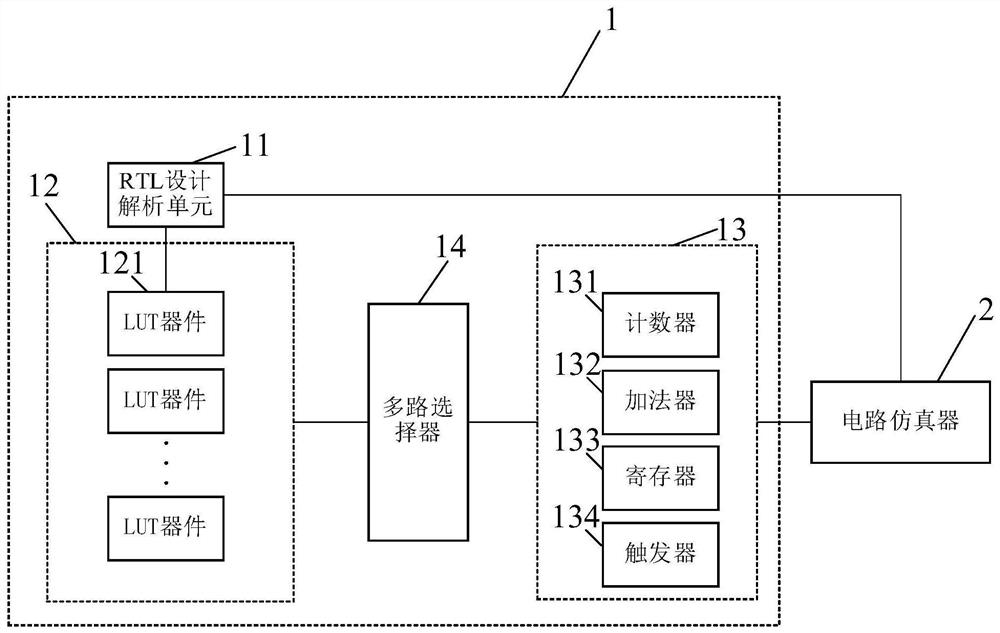

FPGA-based prototype verification method and encoding device

ActiveCN113343615AIncrease flexibilityShorten the error troubleshooting cycleCAD circuit designEnergy efficient computingError checkingComputer architecture

The embodiment of the invention provides a FPGA-based prototype verification device and method, and relates to the technical field of prototype verification. The prototype verification device based on the FPGA comprises an RTL design module, a circuit simulator, a compiling tool and an FPGA module which are connected with one another, and the RTL design module is used for obtaining a plurality of key signals in an RTL design file, storing hierarchical paths of the key signals and generating a constraint list based on the hierarchical paths of the key signals at all levels; the RTL design module is further used for obtaining a plurality of redundant signals in the RTL design file according to the key signals at all levels; the circuit simulator is used for generating a configuration file of the compiling tool based on each level of key signals and the plurality of redundant signals; the compiling tool is further used for obtaining a test file for prototype verification according to the RTL design file, the constraint list and the configuration file; and the FPGA module is used for performing prototype verification by using the test file. According to the invention, the error checking period of prototype verification is shortened, and the debugging period of prototype verification is accelerated.

Owner:中天恒星(上海)科技有限公司

Method and apparatus for moving data

ActiveCN103221939ATransformation of program codeProgram control using stored programsProcessor registerSignal on

A method for moving data from a first register file (4358-1 to 4358-8, 7902) in a computational unit (4308-1 to 4308-M, 7607-1 to 7607-P) to a second register file (5206) in a processor (4322, 7614) is provided. The state of a signal on a data movement lead (risc_is_mtwr) is changed to indicate the data movement instruction from a first register file (4358-1 to 4358-8, 7902) in a computational unit (4308-1 to 4308-M, 7607-1 to 7607-P) to a second register file (5206) in a processor (4322, 7614). A lane address from the processor (4322, 7614) to the computational unit (4308-1 to 4308-M, 7607-1 to 7607-P) is provided over a first address lead (risc_is_ra).; A read address from the processor (4322, 7614) to the computational unit (4308-1 to 4308-M, 7607-1 to 7607-P) is provided over a second address lead (risc_is_ra), and data is transferred from the first register file (4358-1 to 4358-8, 7902) in the computational unit (4308-1 to 4308-M, 7607-1 to 7607-P) to the second register file (5206) in the processor (4322, 7614) over a data interface lead (node_regf_rd).

Owner:TEXAS INSTR INC

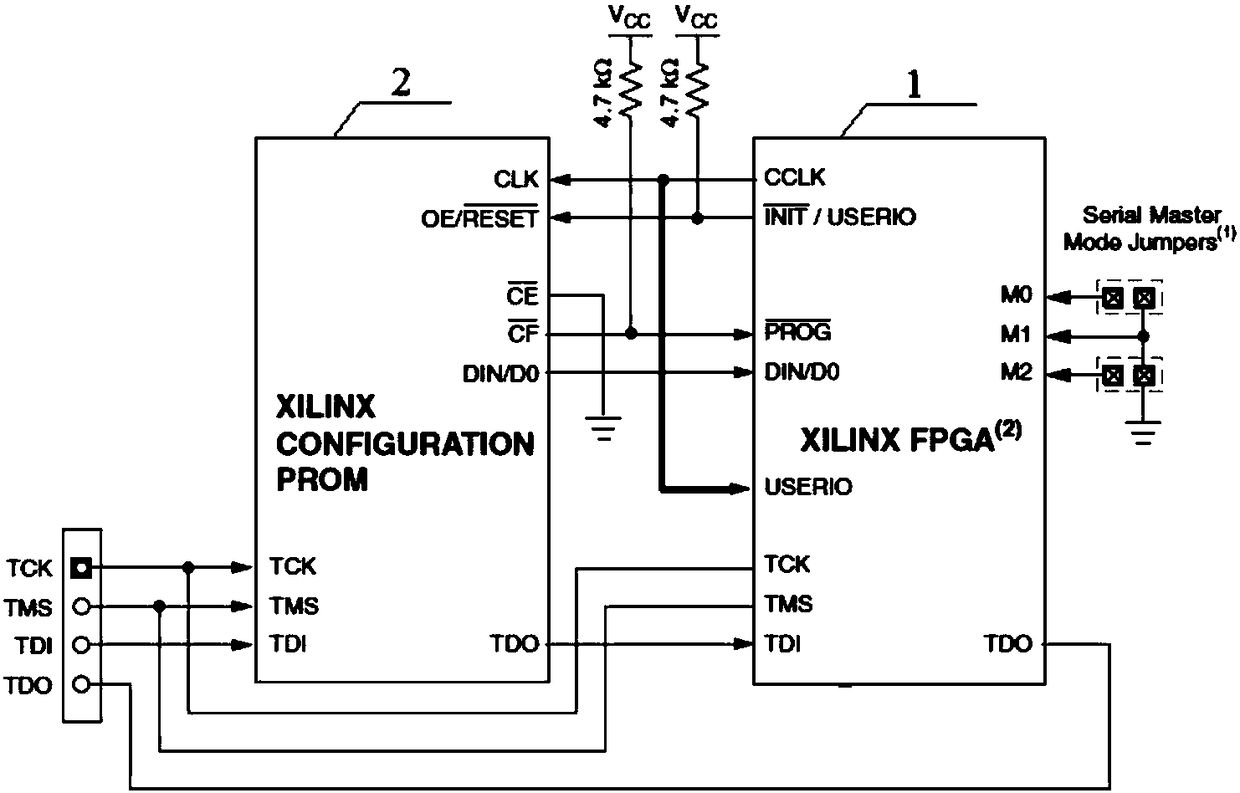

Parameter configuration method and device based on FPGA circuit, and storage space

ActiveCN109308031AShorten the timeGuaranteed confidentialityProgramme controlComputer controlComputer hardwareData segment

The invention provides a parameter configuration method based on an FPGA circuit. The parameter configuration method comprises the following steps that (A) a first mcs file is imported; (B) a debugging value is assigned to to-be-debugged parameters; (C) the first mcs file is copied to obtain a second mcs file, and parameter data segments are written into the second mcs file; (D) the second mcs file is burned into a PROM configuration chip; (E) data in the PROM configuration chip are loaded into an FPGA circuit, and the to-be-debugged parameters in an FPGA control program are updated; and (F) the FPGA control program is executed, and whether an output signal of an A / D conversion circuit is normal or not is judged. The invention further provides a parameter configuration device based on theFPGA circuit, and a storage space. According to the parameter configuration method, an original FPGA control program code does not need to be modified, the multiple-time repetitive compilation and synthesis processes are omitted, and the parameter configuration method has the characteristics of good human-computer interaction, high automation degree and high debugging efficiency.

Owner:HUNAN AEROSPACE ELECTROMECHANICAL EQUIP & SPECIAL MATERIAL INST

Design method of industrial automation design programming software system

PendingCN111274623ASimple designImprove efficiencyComputer aided designSpecial data processing applicationsSoftware systemSoftware engineering

The invention discloses a design method of an industrial automation design programming software system. The design method comprises the following steps: (1) mechanical design: establishing a library file similar to Solidworks or Altium designer software; (2) program design: according to the parameter definition of the library file, limiting the working principle and the activity range of various accessories, and providing a programming basis after software arranges all accessories used in the currently designed non-standard automatic equipment in a list manner; and (3) circuit design: softwareknows related control principles of accessories and related accessories selected by a user, software knows power supplies required by sensors and related sensors selected by the user, types of outputsignals and equipment operation processes designed by the user known by the software, and the software generates a circuit schematic diagram while generating a program. According to the invention, the functions of mechanical design, multifunctional calculation, software program generation, circuit generation, accessory purchasing lists, related manufacturer recommendation, expense settlement, taxcalculation and the like are integrated, convenience is brought to design, and the efficiency is effectively improved.

Owner:罗寄芳

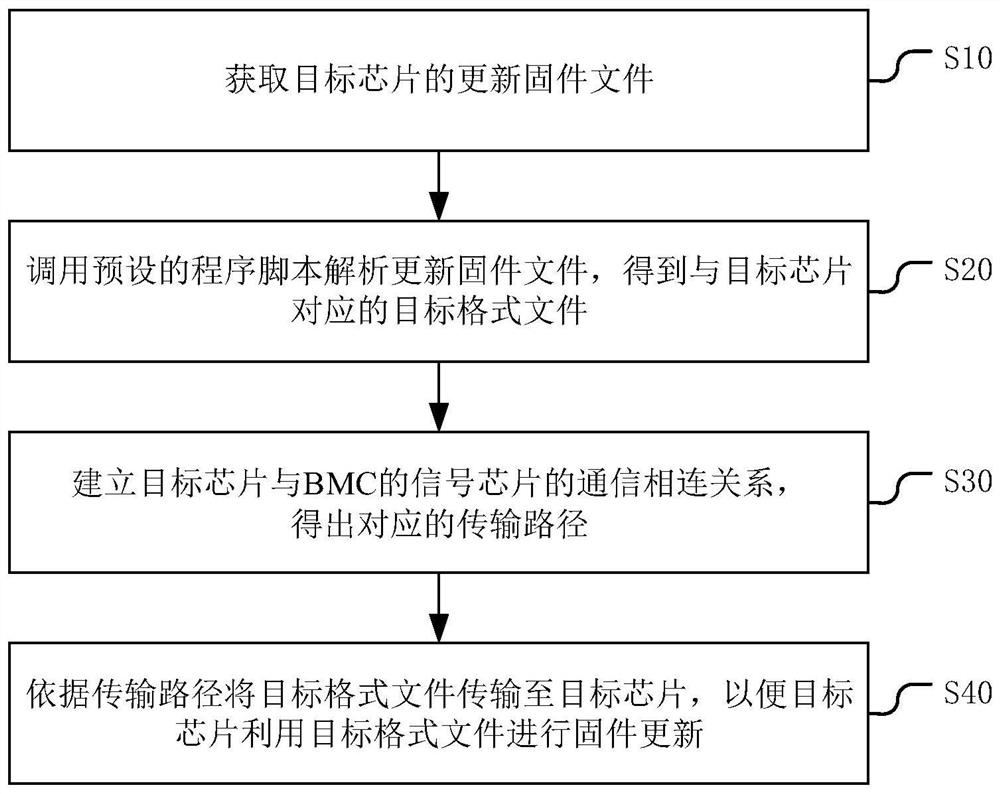

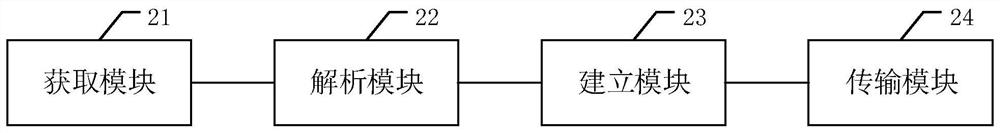

Firmware updating method and device of chip, equipment and storage medium

PendingCN112947964AImprove convenienceImprove upgrade efficiencySoftware deploymentPathPingEngineering

The invention discloses a firmware updating method for a chip, which is applied to a BMC. The method comprises the following steps: acquiring an updated firmware file of a target chip; calling a preset program script to analyze and update the firmware file to obtain a target format file corresponding to the target chip; establishing a communication connection relationship between the target chip and a signal chip of the BMC to obtain a corresponding transmission path; and transmitting the target format file to the target chip according to the transmission path, so that the target chip performs firmware updating by using the target format file. It can be seen that the method can improve the convenience of firmware updating of the chip, prevent the firmware updating process from being affected by other devices, relatively guarantee the stability and reliability of service operation of the server, reduce the consumption of human resources and improve the firmware updating efficiency. The invention furthermore discloses a chip firmware updating device, equipment and a computer readable storage medium, which have the above beneficial effects.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

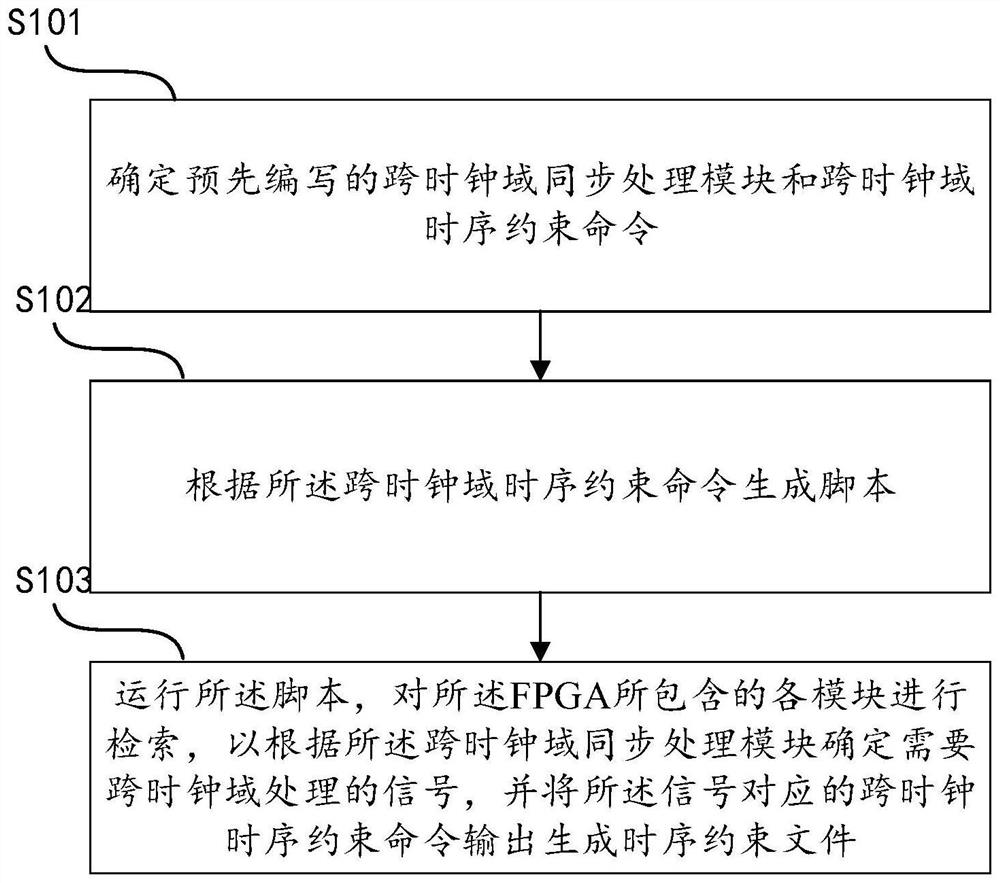

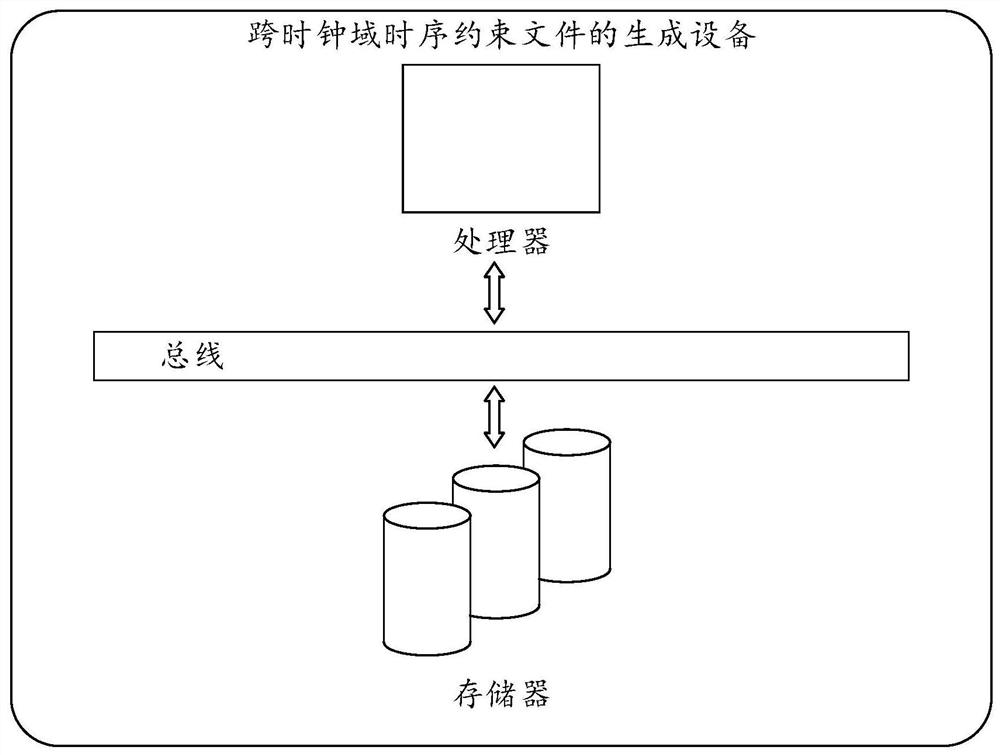

Cross-clock-domain time sequence constraint file generation method and device and medium

PendingCN111651950AImprove R&D efficiencyShorten the timeCAD circuit designSpecial data processing applicationsScripting languageClock time

The invention discloses a cross-clock-domain time sequence constraint file generation method and device and a medium, which are applied to a field programmable gate array (FPGA). The method comprises:determining a pre-written cross-clock-domain synchronous processing module and a cross-clock-domain time sequence constraint command; generating a script according to the clock domain crossing time sequence constraint command; and running the script, retrieving each module contained in the FPGA, determining a signal needing to be subjected to cross-clock domain processing according to the cross-clock domain synchronous processing module, and outputting a cross-clock time sequence constraint command corresponding to the signal to generate a time sequence constraint file. Aiming at a method formanually writing a cross-clock-domain time sequence signal time sequence constraint file in an existing FPGA design process, the method for highly automatically generating the cross-clock-domain timesequence constraint file is completed through a scripting language. The method is convenient to implement, simple in process, efficient and stable, the time for manually constraining the files according to the time sequence can be greatly shortened, and the FPGA research and development efficiency is improved.

Owner:JINAN INSPUR HIGH TECH TECH DEV CO LTD

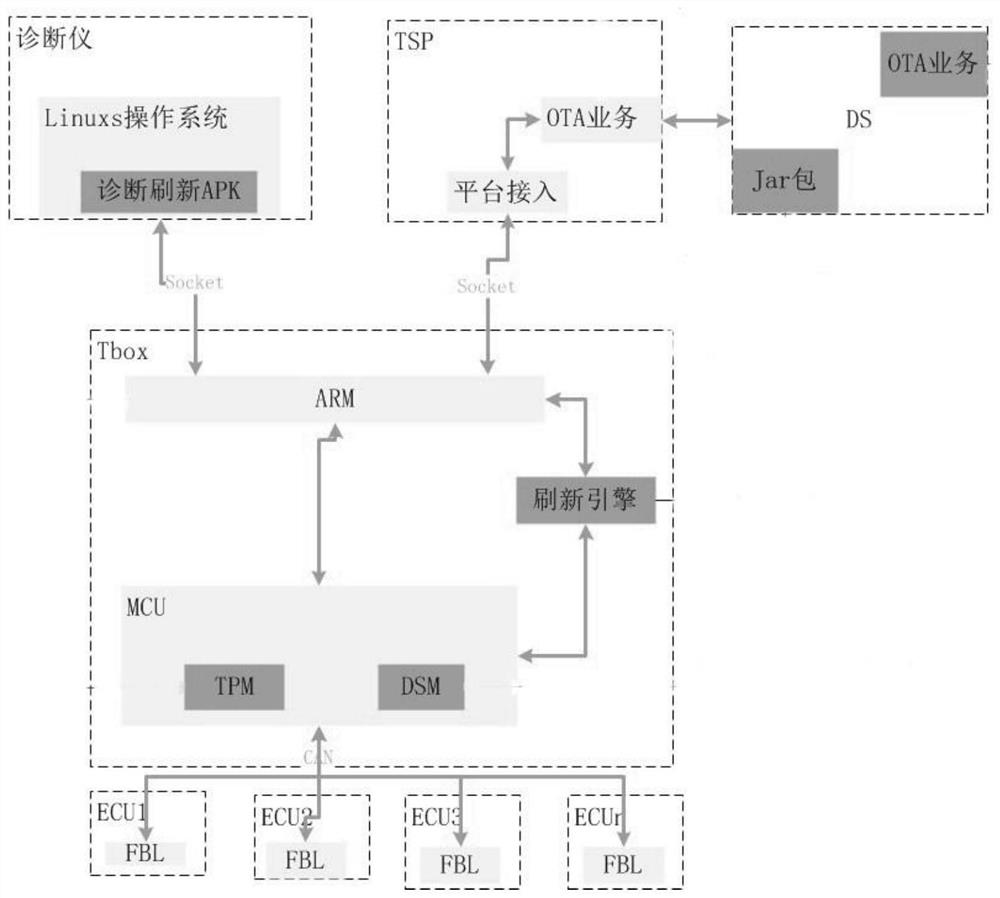

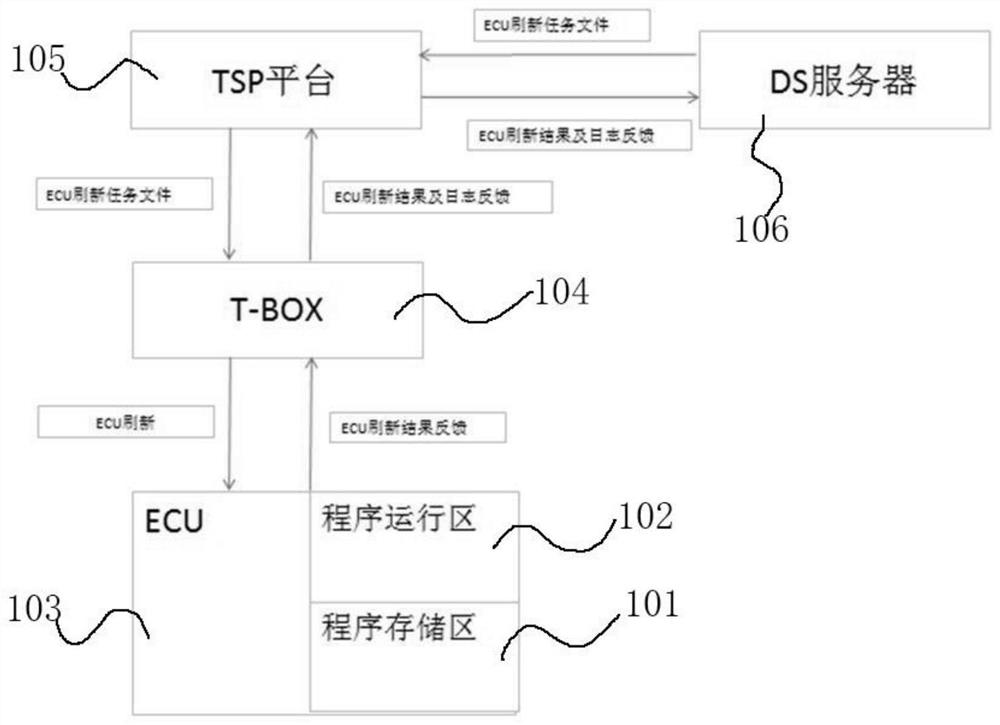

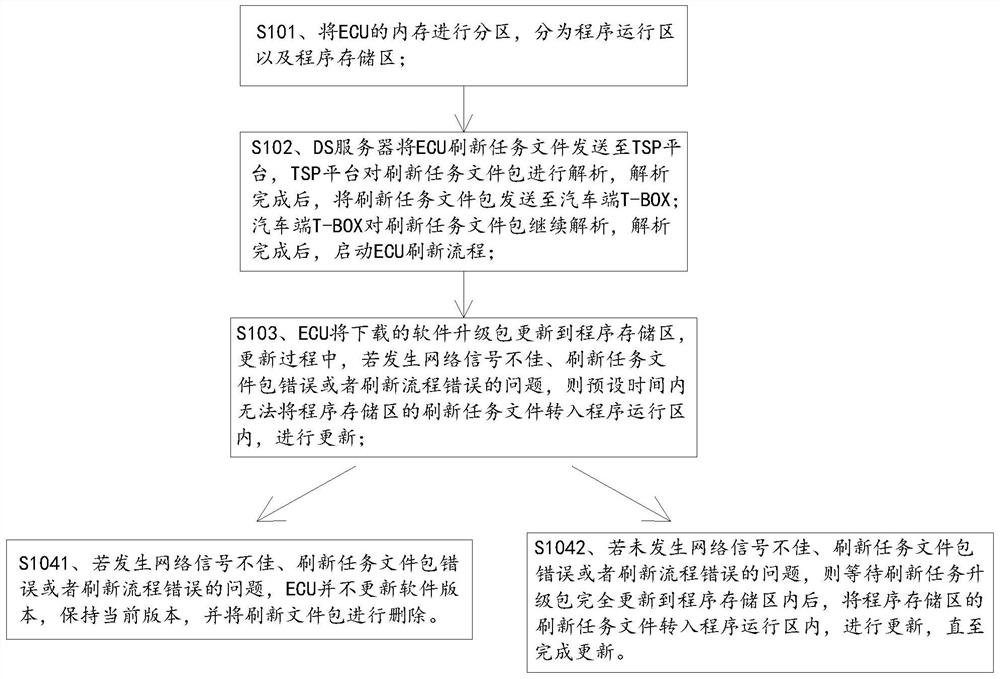

Method and system for solving problem that FOTA cannot be re-refreshed after FOTA upgrade failure

PendingCN112764964AEasy to useVersion controlRedundant operation error correctionSoftware engineeringTerm memory

The invention relates to a method and system for solving the problem that FOTA cannot be re-refreshed after FOTA upgrade failure. The method comprises the steps: partitioning a memory of an ECU (Electronic Control Unit) into a program running region and a program storage region; the DS server sends the ECU refreshing task file to a TSP platform, the TSP platform analyzes a refreshing task file package, and after analysis is completed, the refreshing task file package is sent to an automobile end T-BOX; the vehicle end T-BOX continues to analyze the refreshing task file package, and after analysis is completed, an ECU refreshing process is started; the ECU updates the downloaded software upgrade package to the program storage area, and in the updating process, if the problems of poor network signals, wrong refreshing task file package or wrong refreshing process occur, the refreshing task file in the program storage area cannot be transferred into the program running area for updating within the preset time, so that the situation that the refreshing task file in the program storage area cannot be transferred into the program running area for updating after the FOTA refreshing of the ECU fails can be effectively prevented. And under the condition that the ECU cannot be refreshed again in a short time, the ECU software can keep the current software version and recover the functions of the ECU software, so that the normal use of the vehicle is ensured.

Owner:FJ MOTOR GRP YUDO NEW ENERGY AUTOMOBILE CO LTD

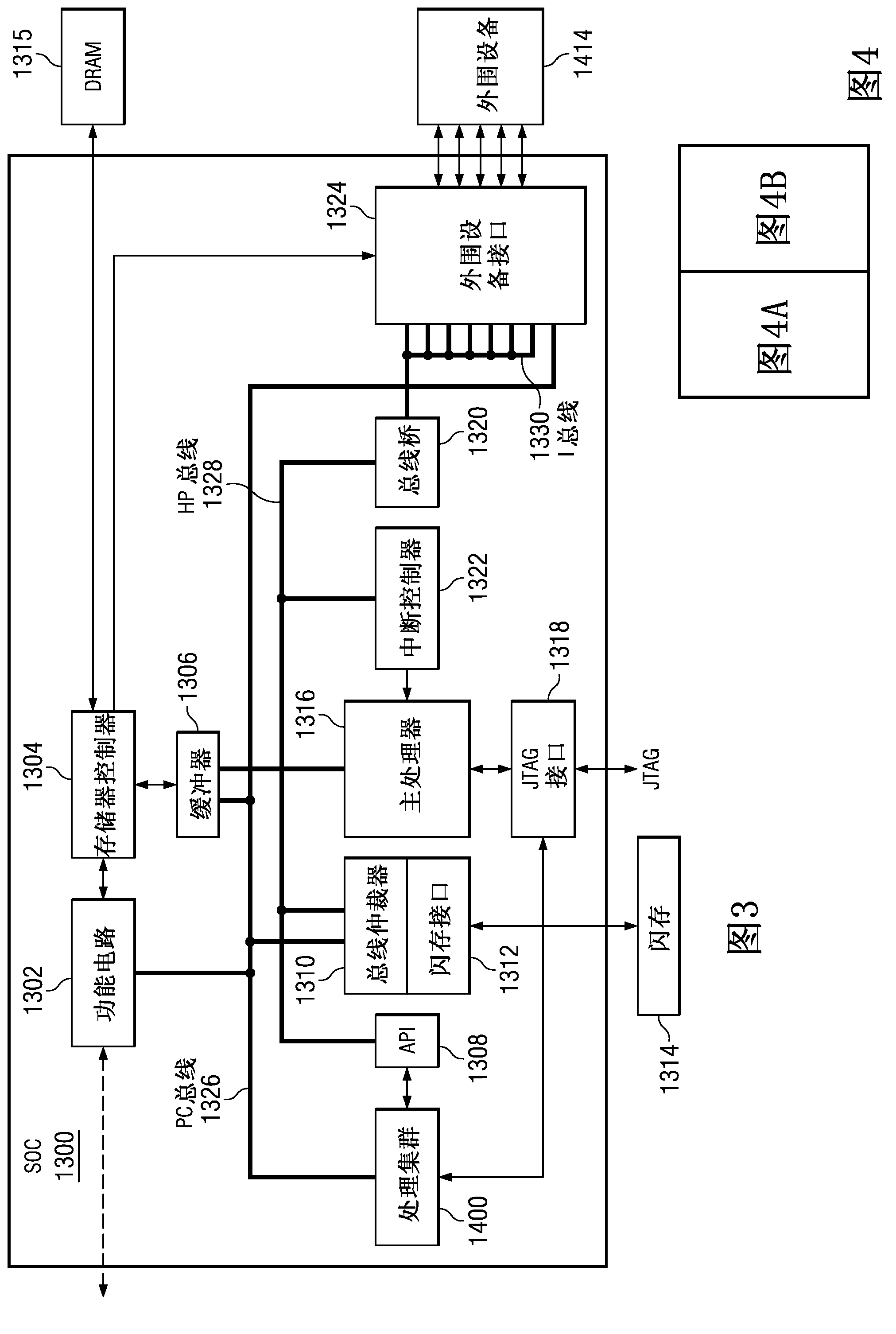

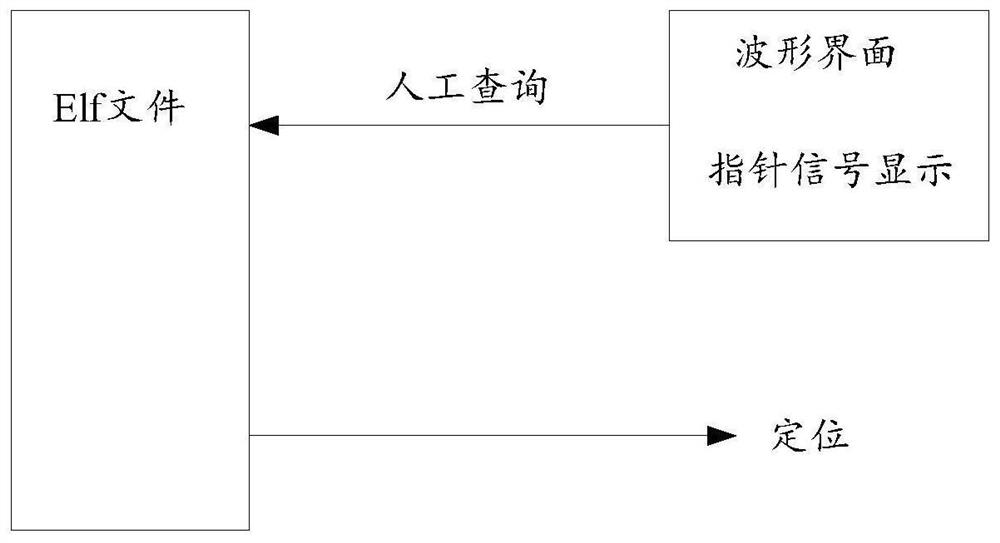

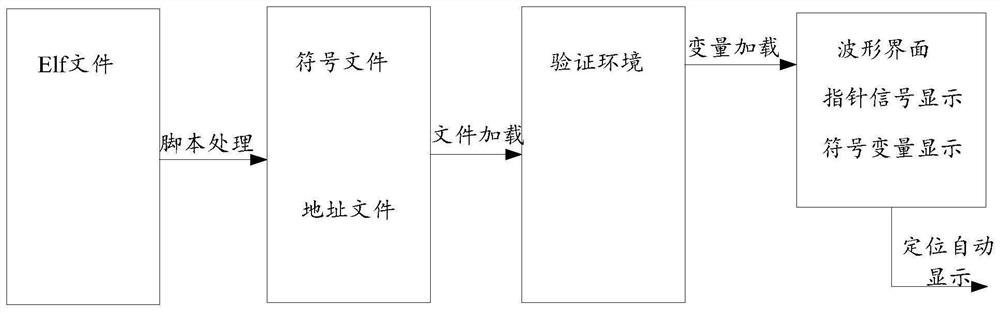

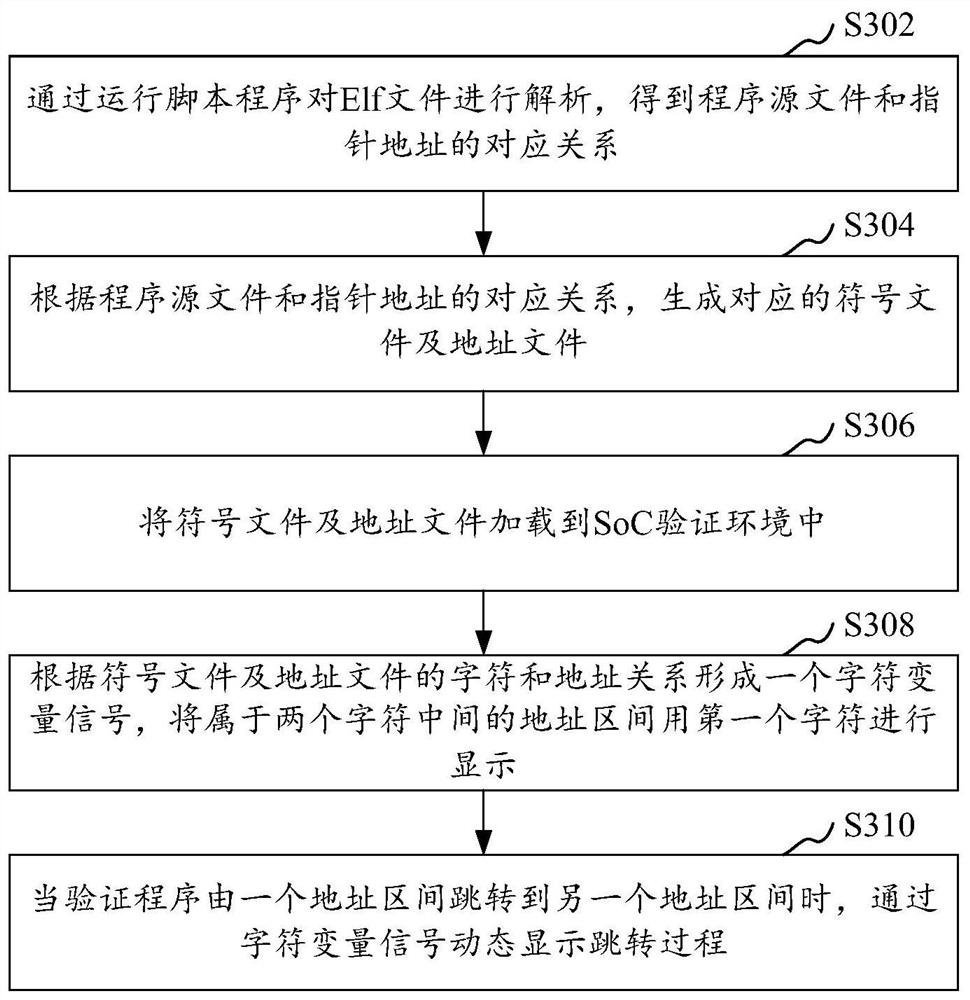

SoC program execution display positioning method and device, computer equipment and storage medium

PendingCN112463164AGood dynamic displayExecution for user interfacesCode compilationComputer hardwareOperating system

The invention relates to a SoC program execution display positioning method and device, computer equipment and a storage medium, and the method comprises the steps: carrying out the analysis of an Elffile through operating a script program, and obtaining a corresponding relation between a program source file and a pointer address; generating a corresponding symbol file and an address file according to the corresponding relationship between the program source file and the pointer address; loading the symbol file and the address file into an SoC verification environment; forming a character variable signal according to the character and address relationship of the symbol file and the address file, and displaying an address interval between the two characters by using a first character; whenthe verification program skips from one address interval to another address interval, dynamically displaying a skipping process through the character variable signal. According to the invention, therelationship between the pointer and the source file can be automatically matched and displayed on an interface such as a waveform in a manner such as a signal variable.

Owner:RAMAXEL TECH SHENZHEN

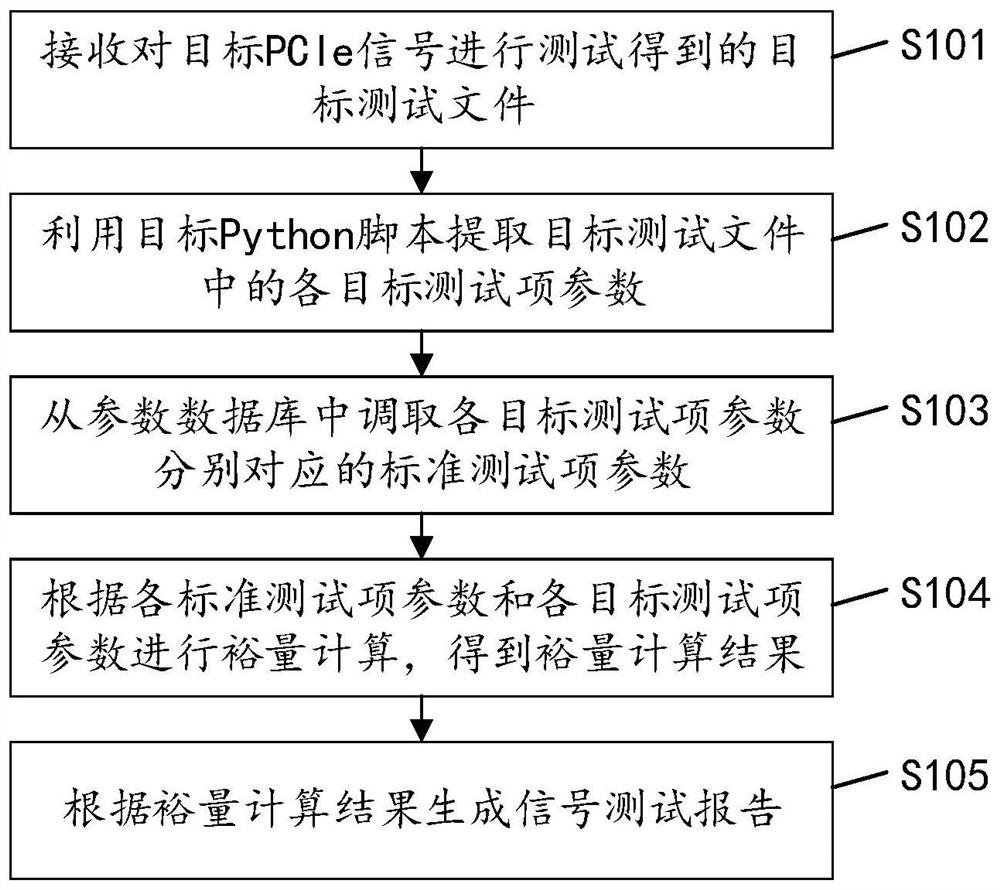

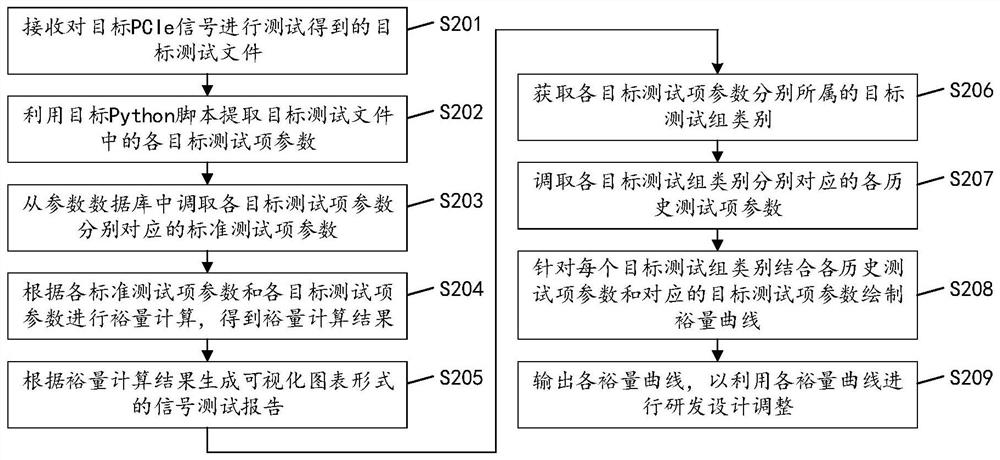

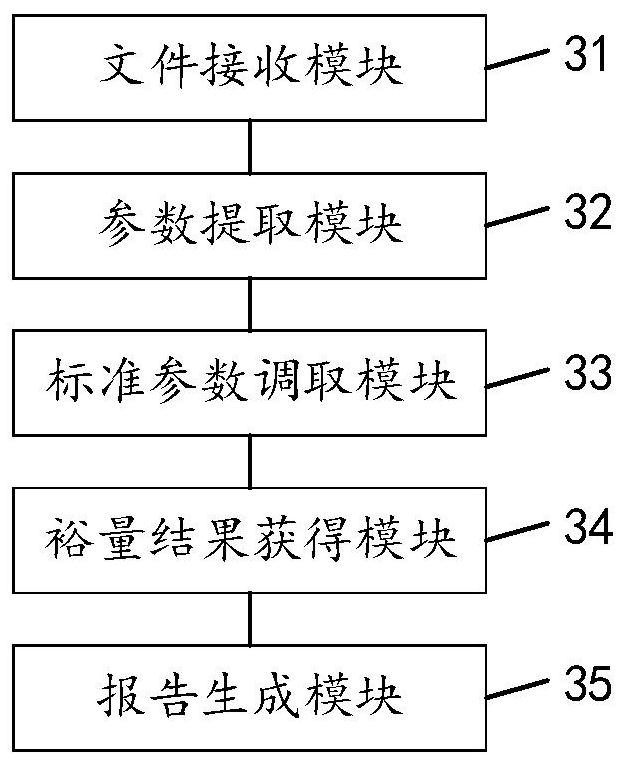

Test report generation method, device and equipment and computer readable storage medium

ActiveCN112256503AImprove signal test efficiencyReduce R&D costsDetecting faulty computer hardwareTest efficiencyTarget signal

The invention discloses a test report generation method. The method comprises the following steps: receiving a target test file obtained by testing a target PCIe signal; extracting each target test item parameter in the target test file by utilizing the target Python script; calling standard test item parameters corresponding to the target test item parameters from a parameter database; carrying out margin calculation according to each standard test item parameter and each target test item parameter to obtain a margin calculation result; and generating a signal test report according to the margin calculation result. By applying the test report generation method provided by the invention, the signal test efficiency is greatly improved, and the research and development cost is saved. The invention further discloses a test report generation device and equipment and a storage medium, which have corresponding technical effects.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

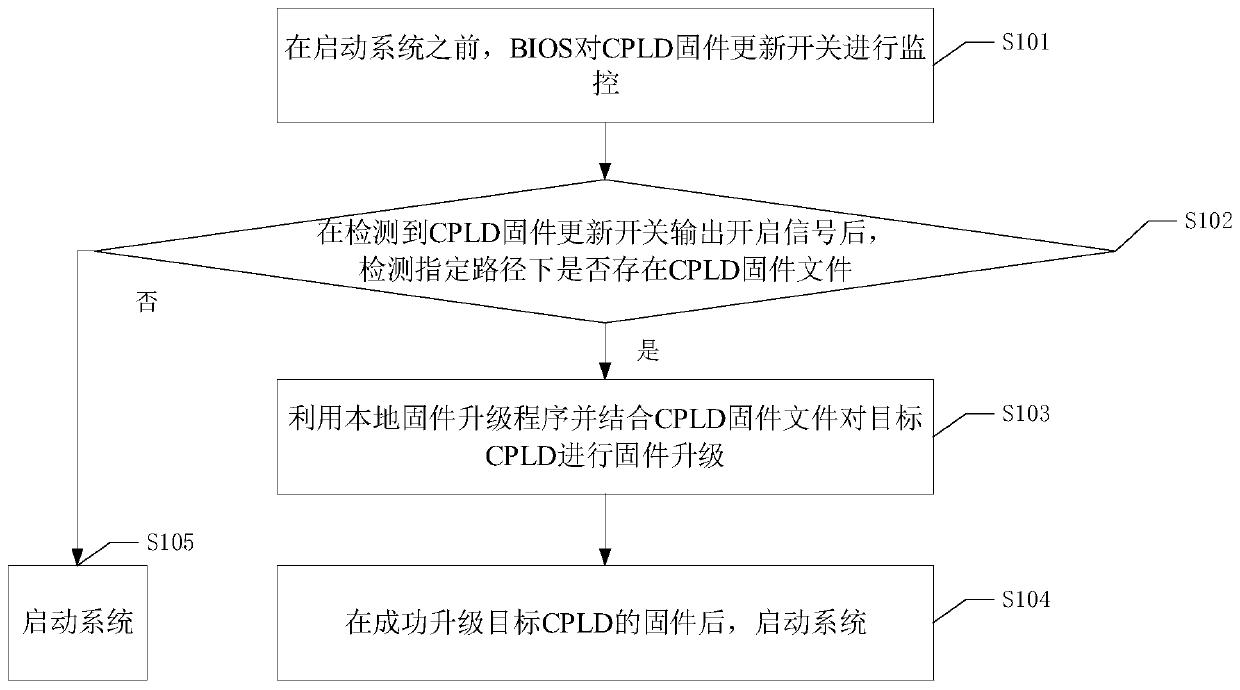

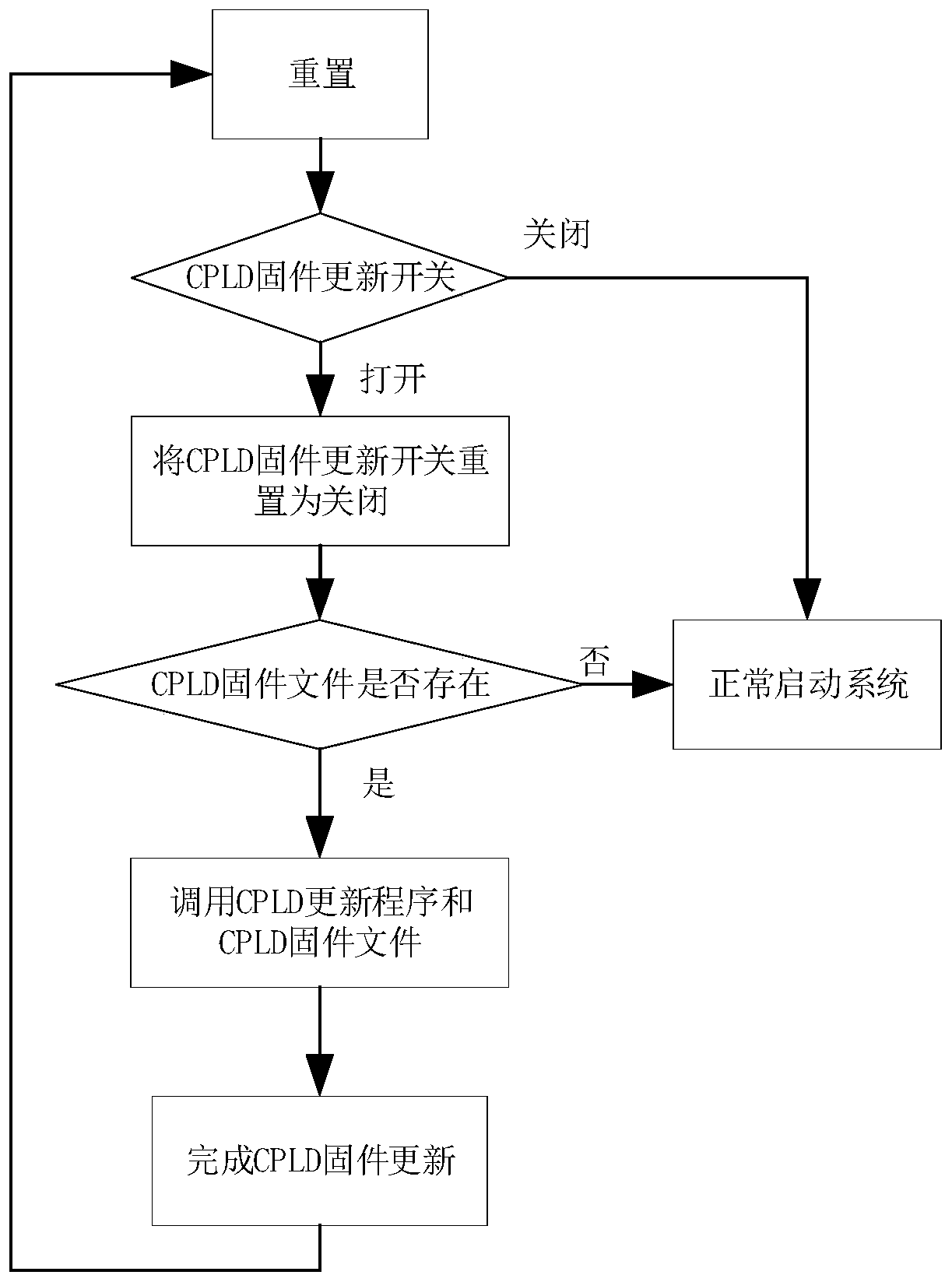

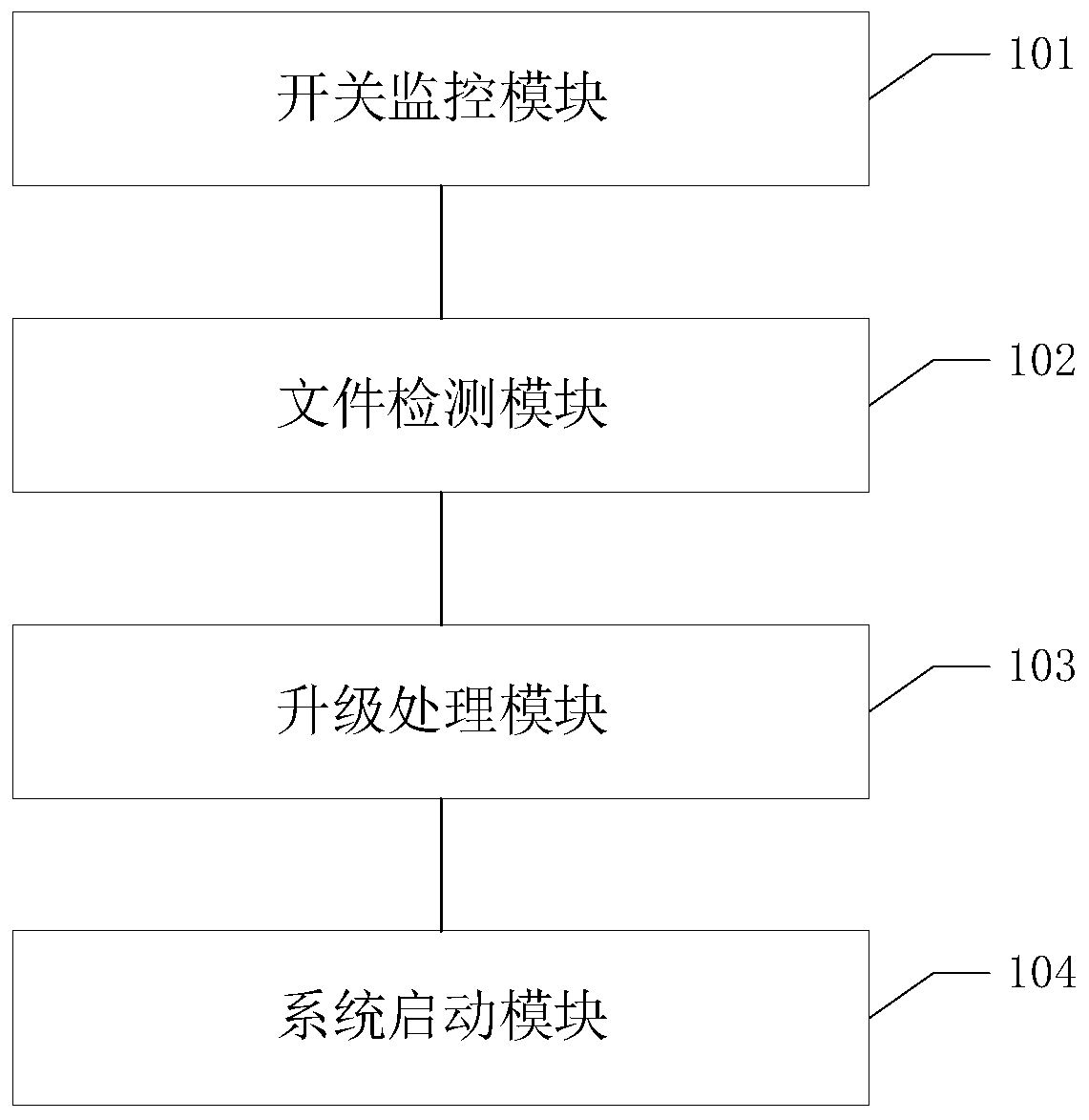

CPLD firmware upgrading method, device and equipment and readable storage medium

The invention discloses a CPLD firmware upgrading method, device and equipment and a readable storage medium, and the method comprises the following steps that a BIOS monitors a CPLD firmware updatingswitch before a system is started; after detecting that the CPLD firmware update switch outputs an opening signal, detecting whether a CPLD firmware file exists in a specified path or not; if yes, firmware upgrading is conducted on the target CPLD through a local firmware upgrading program in combination with the CPLD firmware file; and after the firmware of the target CPLD is successfully upgraded, starting the system. Visibly, in the method, the CPLD firmware can be updated without a third-party burning tool, burning software and professionals, the CPLD firmware can be directly updated by alocal machine, and the firmware updating efficiency of the CPLD is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

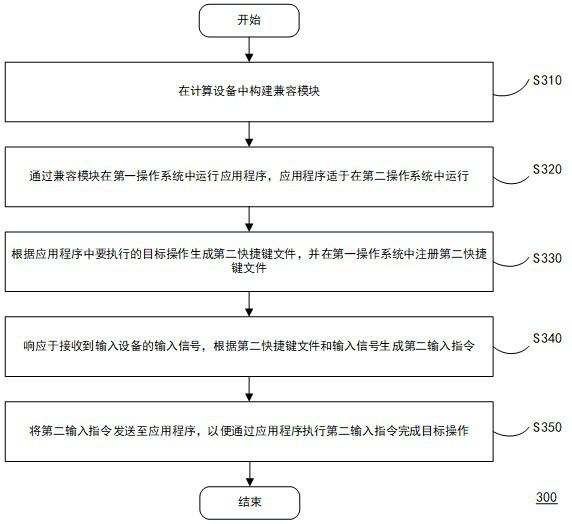

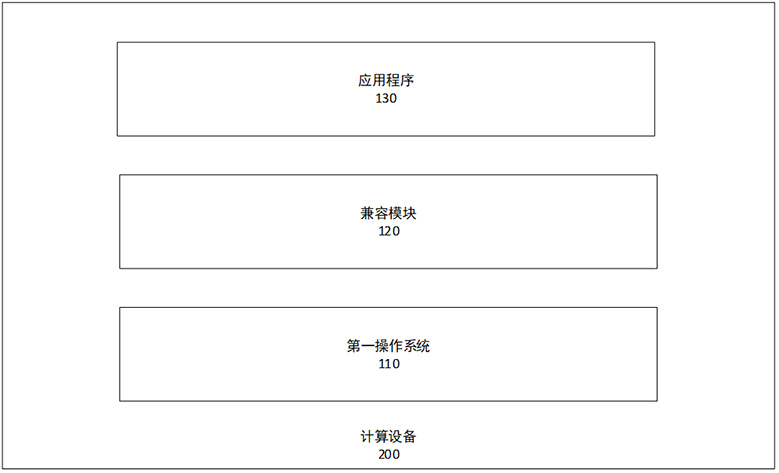

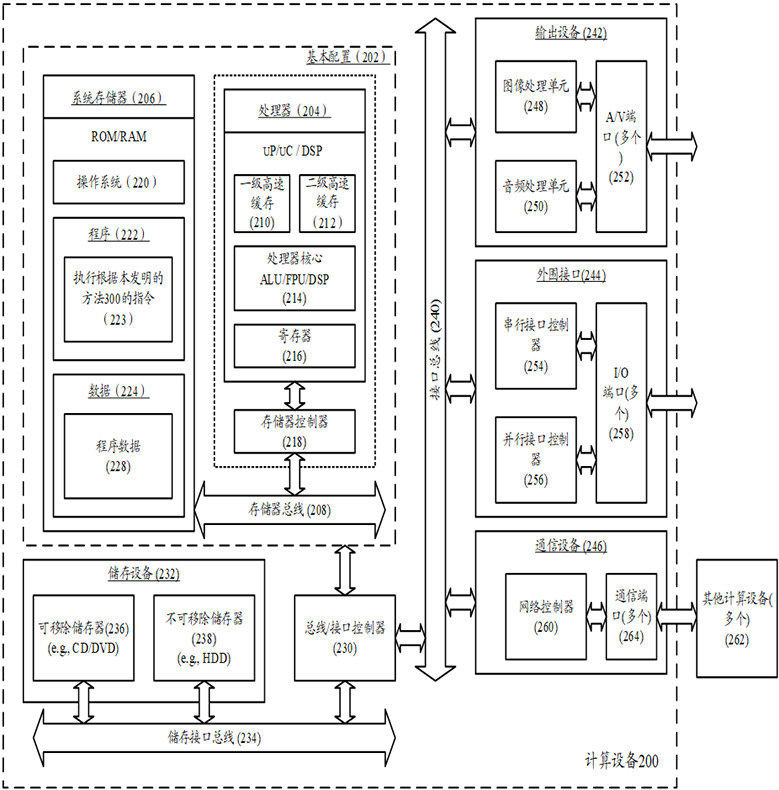

Shortcut key implementation method, computing device and storage medium

ActiveCN113961086AImprove adaptabilityImprove user experienceInput/output processes for data processingOperational systemKeyboard shortcut

The invention discloses a shortcut key implementation method, computing equipment and a storage medium. The shortcut key implementation method comprises the following steps: constructing a compatible module in the computing equipment; running an application program in the first operating system through the compatible module, wherein the application program is suitable for running in the second operating system; generating a second shortcut key file according to a target operation to be executed in the application program, and registering the second shortcut key file in the first operating system; in response to a received input signal of the input device, generating a second input instruction according to the second shortcut key file and the input signal; and sending the second input instruction to the application program so as to execute the second input instruction through the application program to complete the target operation. According to the method and the device, the second shortcut key file is registered in the operating system, so that when the application program is executed in the unmatched operating system, the shortcut key can still be normally used to complete the target operation, and the use experience of a user when the operating system is used to run the application program which is not completely matched is improved.

Owner:UNIONTECH SOFTWARE TECH CO LTD

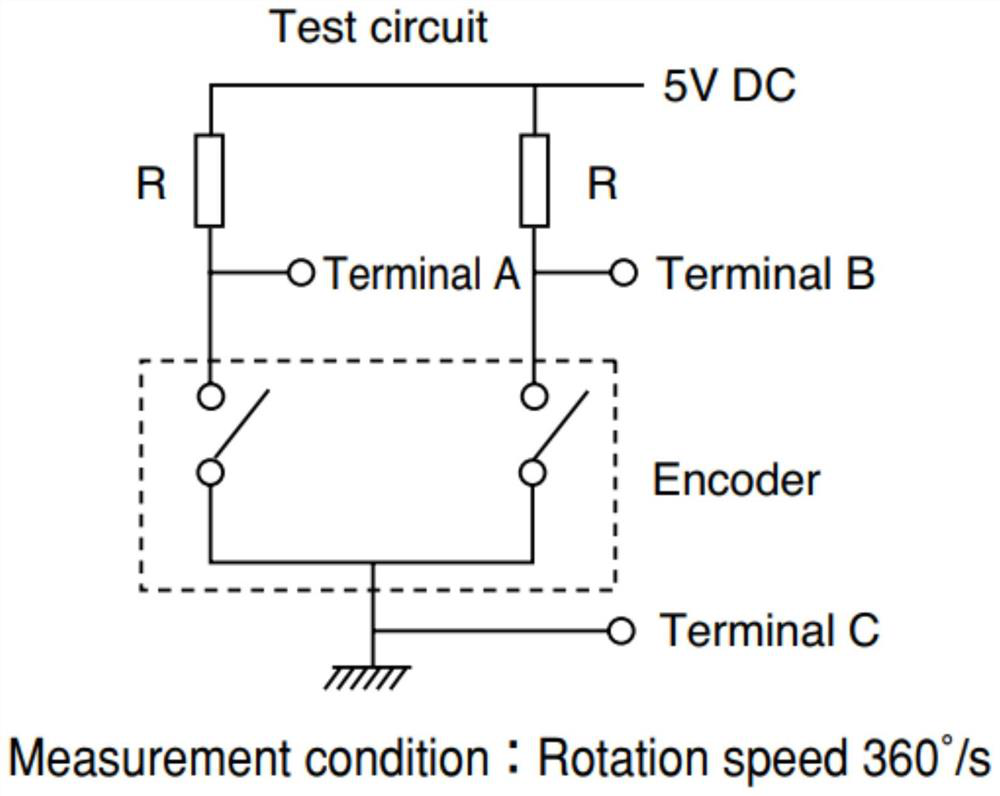

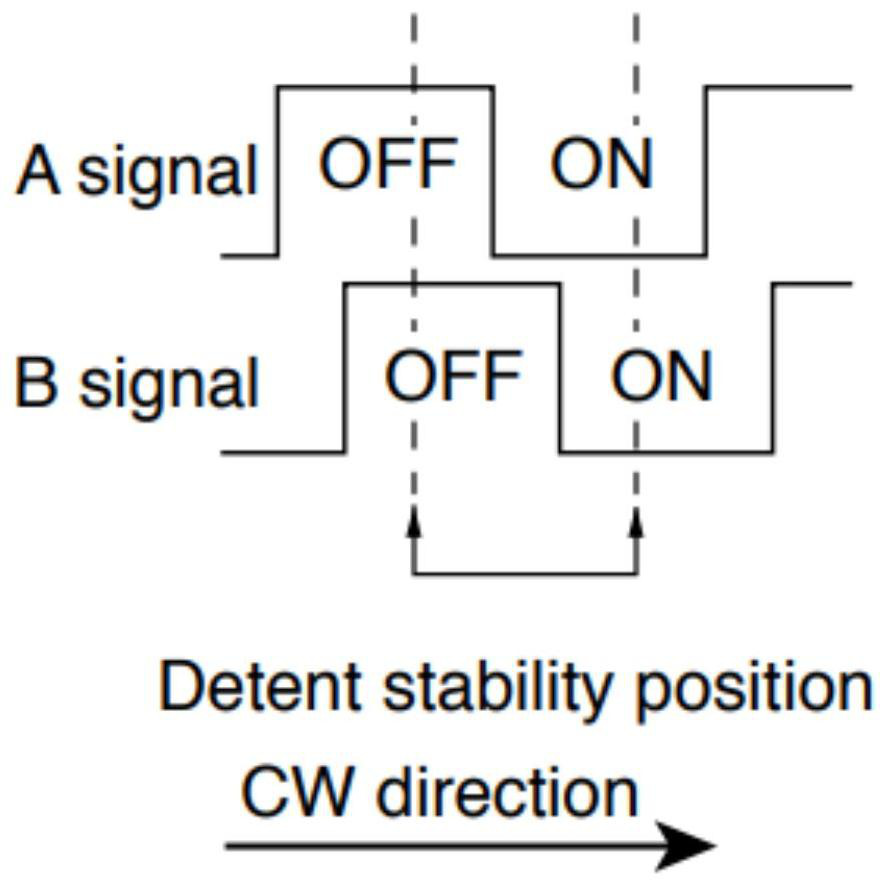

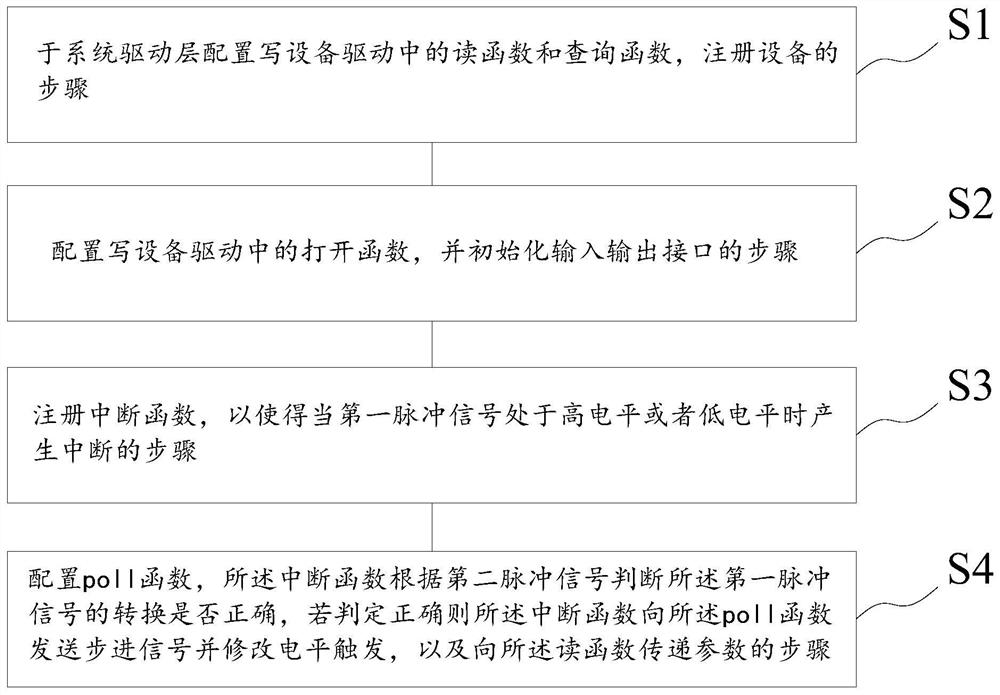

Digital encoder interrupt filtering method based on linux platform

PendingCN112815967ALow costReduce complexityConverting sensor output electrically/magneticallyComputer hardwareInit

The invention provides a digital encoder interrupt filtering method based on a linux platform. The method comprises the following steps of S1, configuring a read function and a query function in a write device driver on a system driver layer, and registering a device, S2, configuring an opening function in the write device driver, and initializing an input / output interface, S3, registering an interrupt function so as to generate interrupt when the first pulse signal is at a rising edge or a falling edge, and S4, configuring a poll function, enabling the interrupt function to judge whether conversion of the first pulse signal is correct or not according to a second pulse signal, if the conversion of the first pulse signal is correct, enabling the interrupt function to send a stepping signal to the poll function and modify level triggering, and transmitting parameters to the read function. Aiming at the problem of interference processing of a digital encoder in the prior art, low hardware cost and low complexity are achieved, and the bit error rate can be effectively improved.

Owner:SUZHOU CHANGFENG AVIATION ELECTRONICS

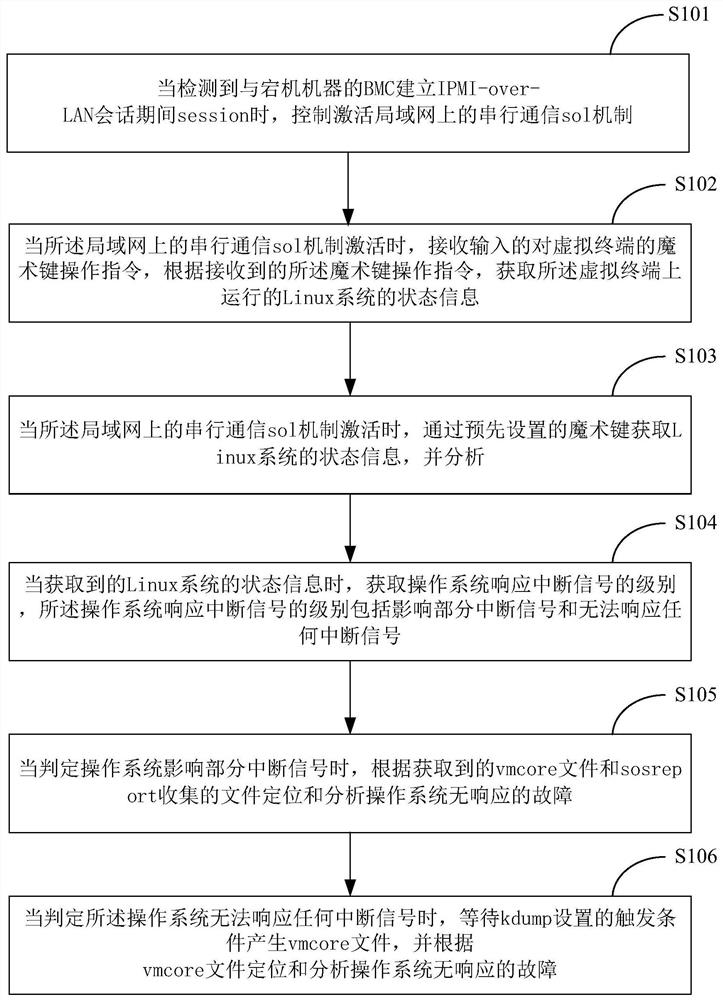

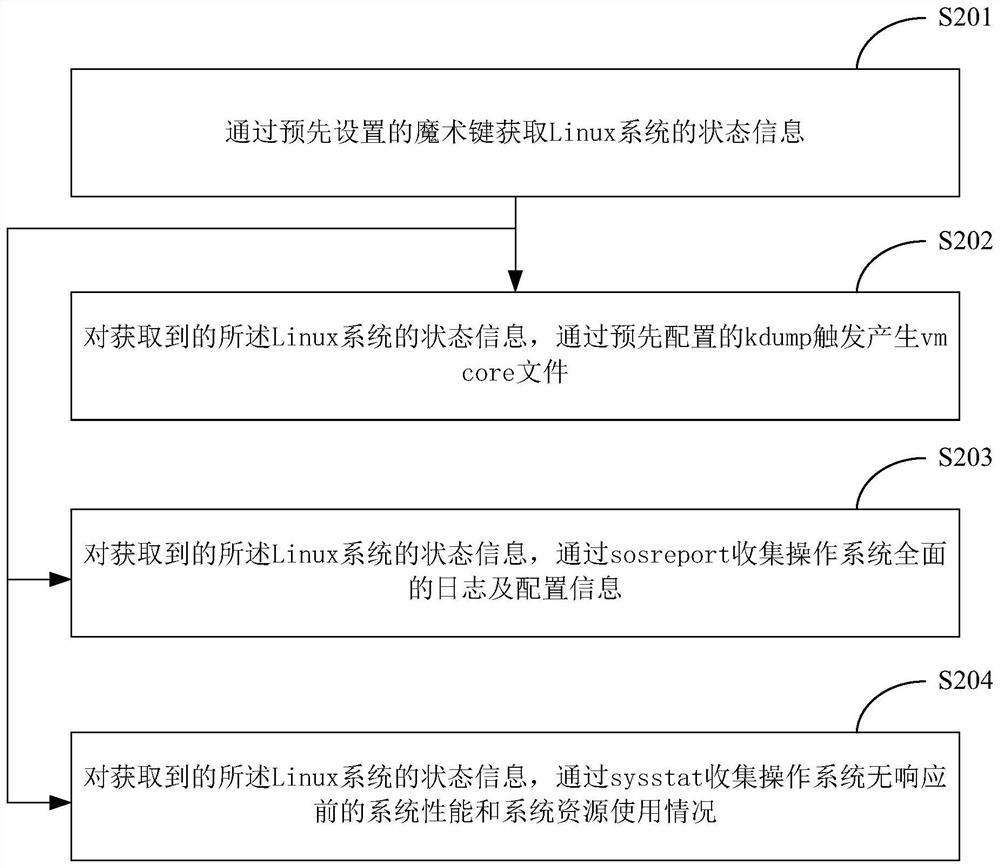

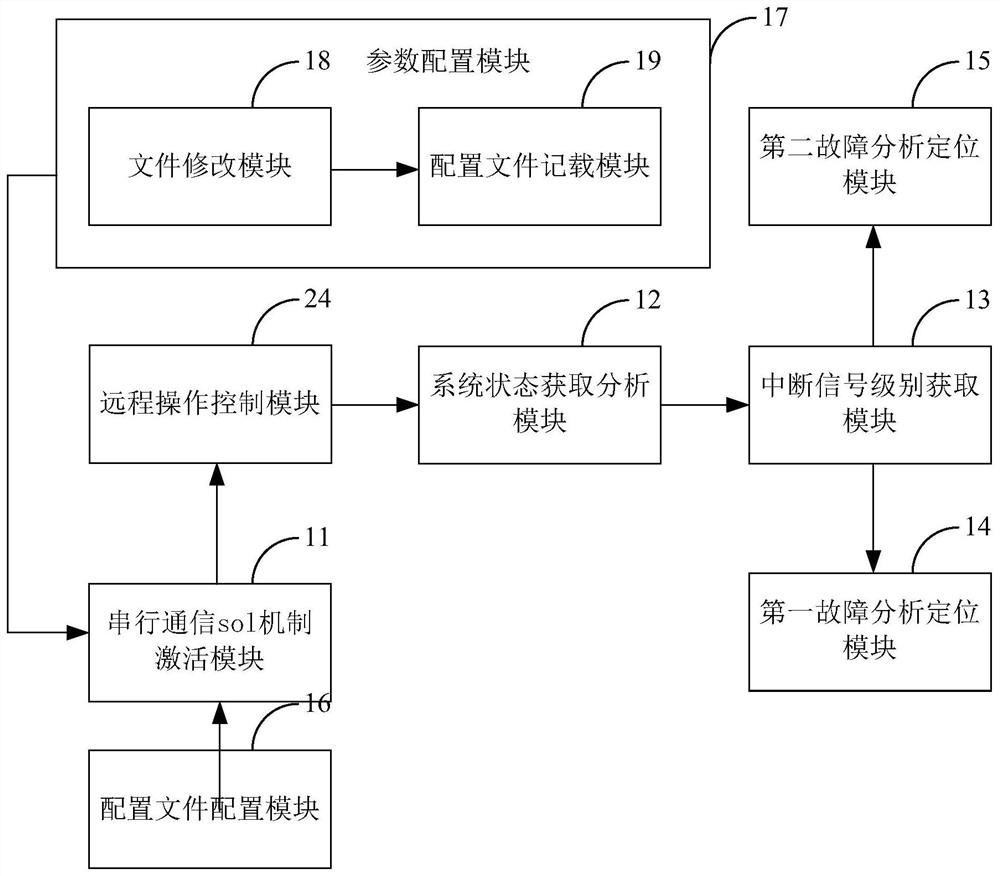

Method and system for remotely collecting downtime information of Linux system

The invention relates to the technical field of servers, and provides a method and system for remotely collecting downtime information of a Linux system, and the method comprises the steps: controlling to activate a serial communication sol mechanism on a local area network; when a serial communication sol mechanism on the local area network is activated, obtaining and analyzing state informationof the Linux system; acquiring the level of the operating system responding to the interrupt signal; when it is judged that the operating system influences a part of interrupt signals, locating and analyzing a fault that the operating system does not respond according to the obtained vmcore file and the file collected by the sosreport; when it is judged that the operating system cannot respond toany interrupt signal, waiting for a trigger condition set by the kdump to generate a vmcore file, and positioning and analyzing a non-response fault of the operating system according to the vmcore file, thereby accurately positioning the non-response problem of the operating system by using the function of a magic key in the session establishment period between the remote console and the server.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

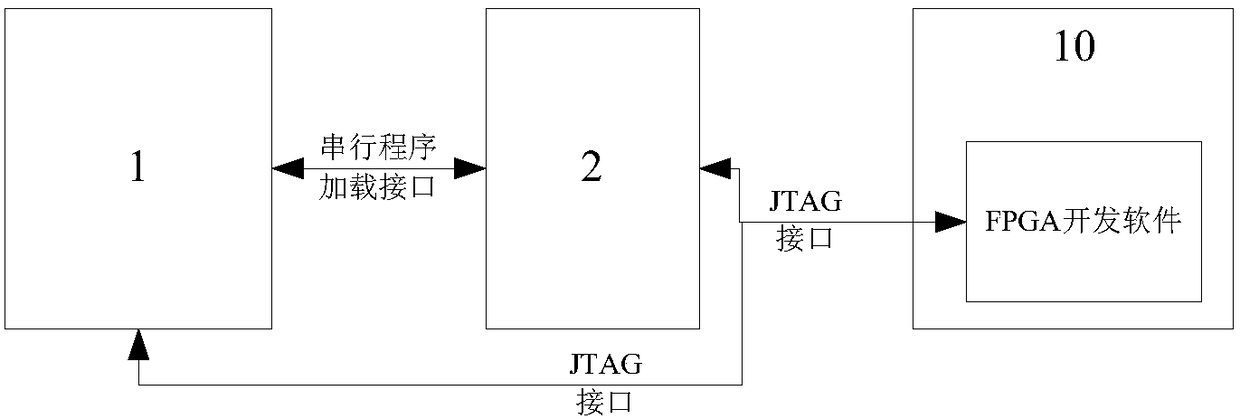

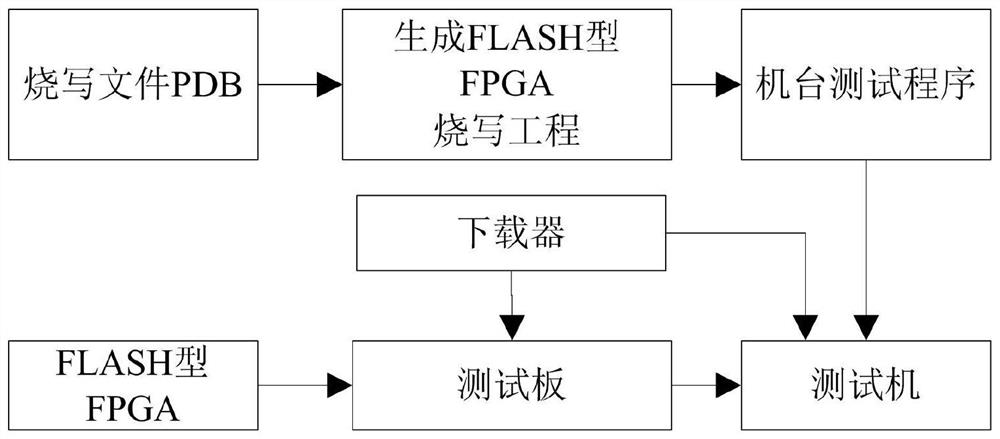

Online programming test method for FPGA

PendingCN111983438ASolve the problem of multiple programmingSolve offline programmingElectronic circuit testingSingle chipTest vector

The invention discloses an online programming test method for an FPGA, and belongs to the technical field of FPGA testing. The downloader establishes a programming project; the test machine calls a programming project to program the programming file PDB into the FLASH type FPGA; the testing machine inputs a corresponding signal to the pin; and the test machine calls the test vector to carry out fault judgment on the FLASH type FPGA. Aiming at analysis and decoding of FLASH type FPGA code streams, the invention provides an online programming test method of an FPGA, a conventional programming and testing separation method of a single-chip microcomputer is classified into an online programming test method, and the problem of repeated programming of a traditional test method is solved. Off-line programming is achieved, manual operation in the testing process is reduced, production efficiency is improved, and cost is reduced.

Owner:58TH RES INST OF CETC

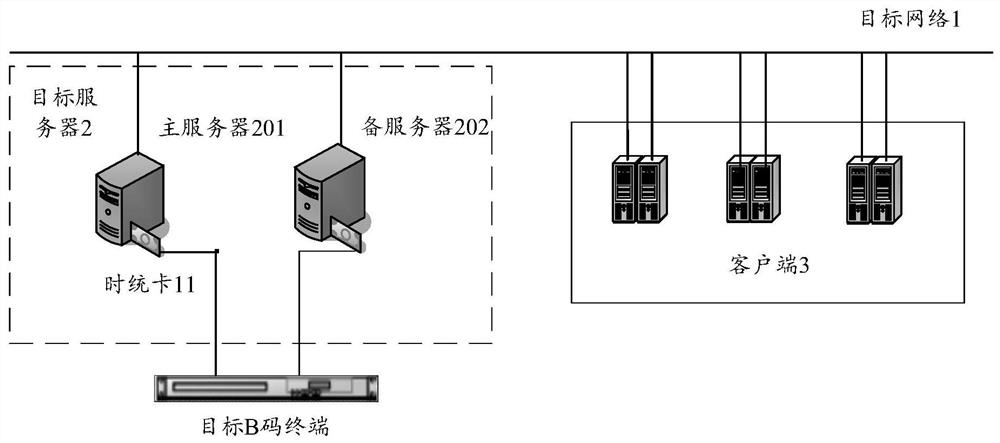

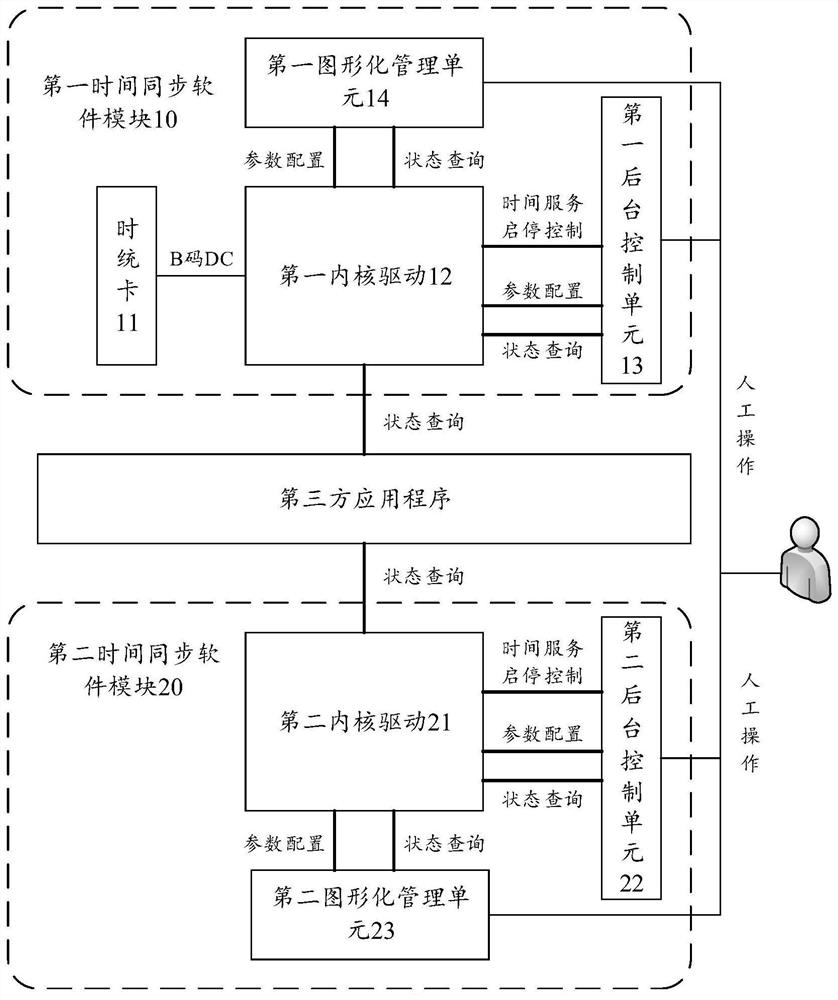

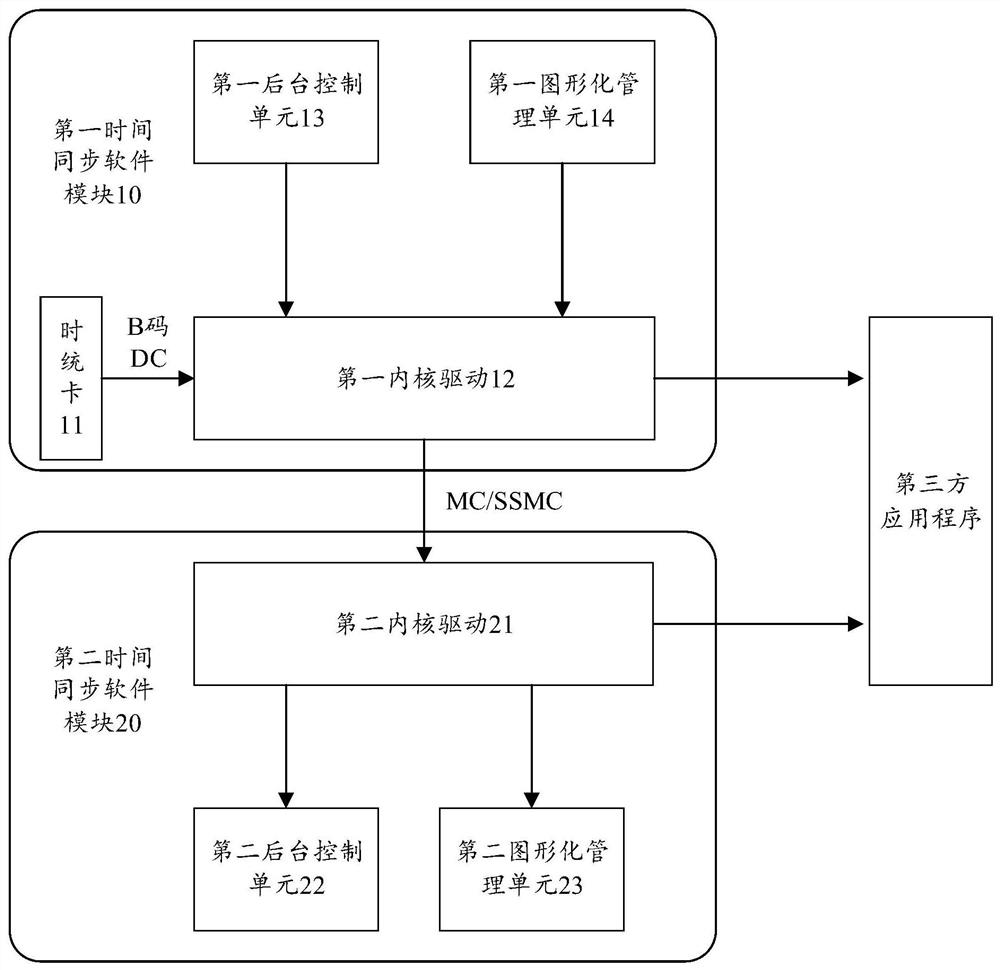

Time synchronization device and method

The invention provides a time synchronization device and method, and relates to the technical field of communication, and the device comprises a target server and a client. A first time synchronization software module based on a domestic Linux system is installed on the target server, the first time synchronization software module comprises a timing unification card and a first kernel driver, a second time synchronization software module based on the domestic Linux system is installed on the client, and the second time synchronization software module comprises a second kernel driver; the timing unification card is used for acquiring a time reference signal from a target B code terminal and sending the time reference signal to the first kernel driver; the first kernel driver is used for carrying out time calibration on the target server based on the time reference signal; and the second kernel driver is used for carrying out network timing on the client based on the time information after timing. According to the time synchronization device set based on the domestic Linux system, the time of the target server and the time of the client can be kept synchronous, and the information security is ensured.

Owner:中国人民解放军32039部队

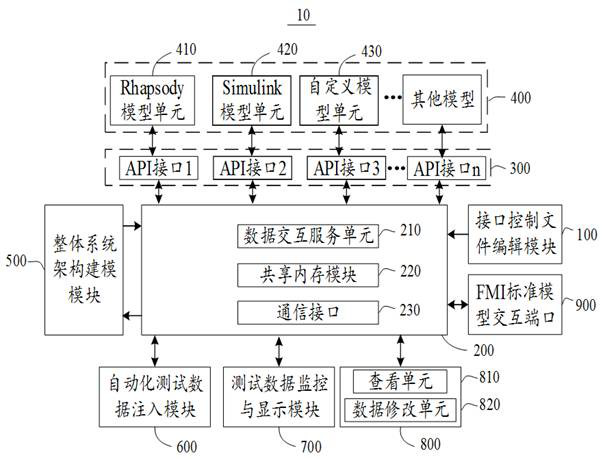

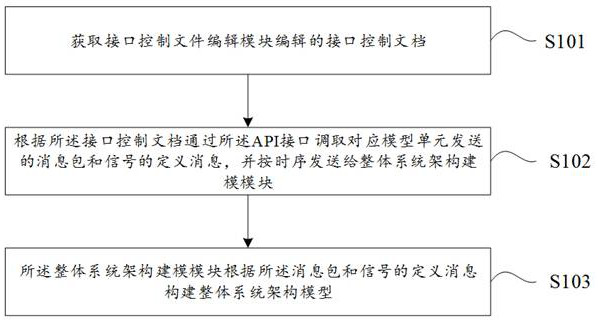

Computer-aided design model integration system and method based on interface control file

ActiveCN112800124BImprove convenienceEasy constructionDatabase management systemsInterprogram communicationComputer Aided DesignInterface control document

The invention provides a computer-aided design model integration system and method based on interface control files, including an interface control file editing module; a data sharing service bus module communicating with the interface control file editing module; and a data sharing service bus module communicating with the data sharing service bus module A plurality of API interfaces; a model unit module communicated with the API interface; and an overall system architecture modeling module connected with the data sharing service bus module; the data sharing service bus module includes data interaction service units; the interface control file editing module is used for editing Interface control document; the data interaction service unit is used to obtain the message package and signal definition message of the Rhapsody model unit, Simulink model unit and custom model unit through the API interface according to the interface control document; the overall system architecture modeling module is used to obtain the message package according to the message package and signal definition messages to build the overall system architecture model.

Owner:成都赢瑞科技有限公司

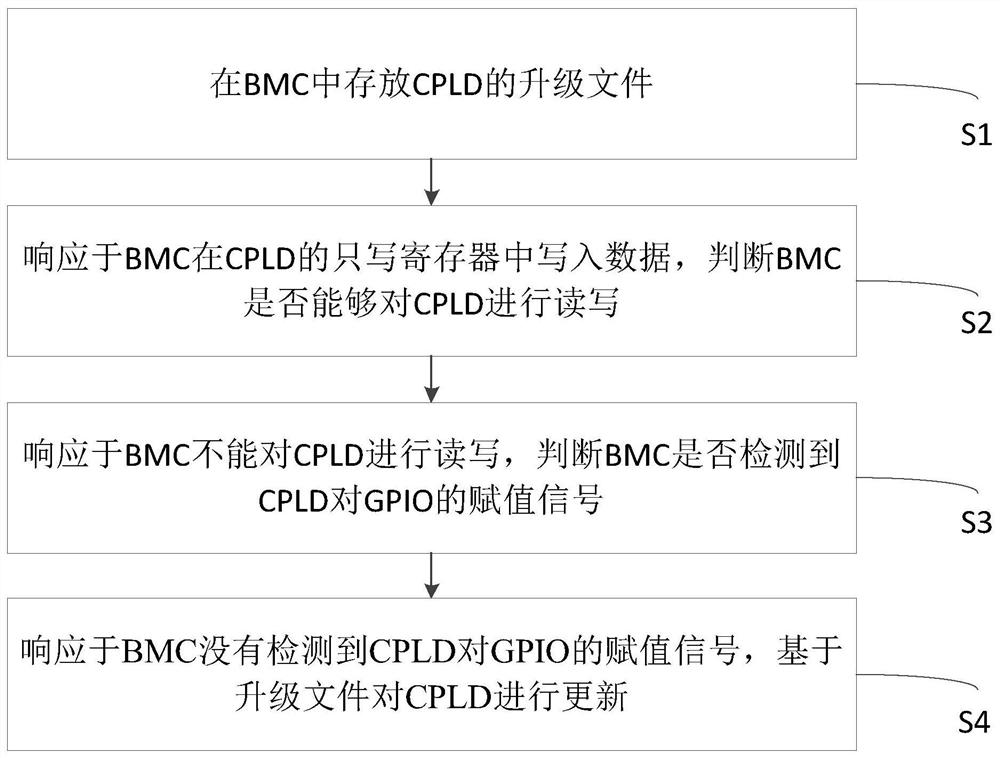

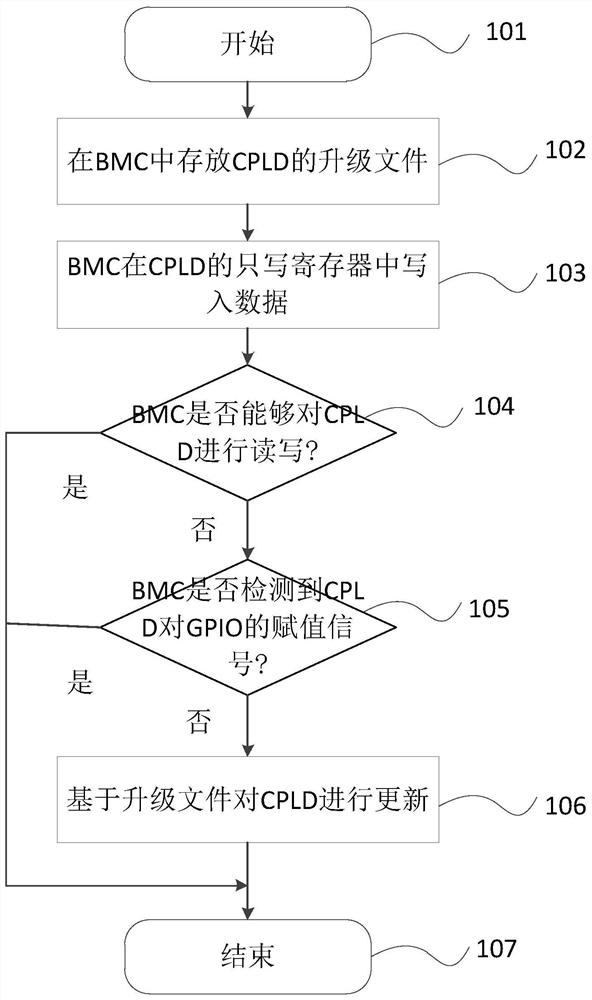

A method, device and medium for recovering faulty cpld

ActiveCN111090545BAvoid machine failureThere will be no misjudgment scenariosRedundant operation error correctionSoftware deploymentComputer hardwareDependability

The invention discloses a method for recovering a faulty CPLD, comprising the following steps: storing an upgrade file of the CPLD in a BMC; in response to the BMC writing data in a write-only register of the CPLD, judging whether the BMC can read and write the CPLD; Since the BMC cannot read and write the CPLD, it is judged whether the BMC detects the assignment signal of the CPLD to the GPIO; and in response to the BMC not detecting the assignment signal of the CPLD to the GPIO, the CPLD is updated based on the upgrade file. The invention also discloses a computer device and a readable storage medium. The method, device and medium for recovering a faulty CPLD proposed by the present invention ensure no misjudgment of the fault of the CPLD through a double judgment mechanism, improve the reliability of the overall system, and store the upgrade file of the CPLD in the BMC, thereby ensuring the recovery of the CPLD to the correct version.

Owner:INSPUR SUZHOU INTELLIGENT TECH CO LTD

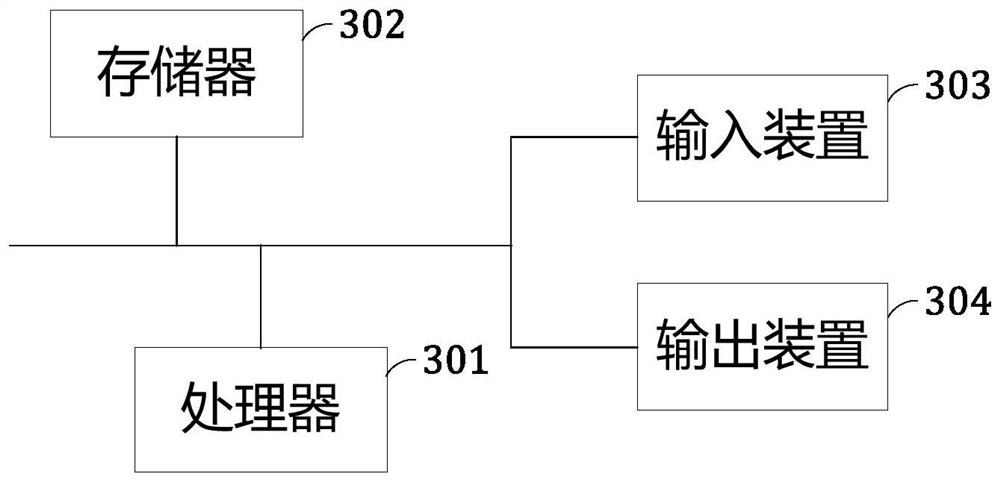

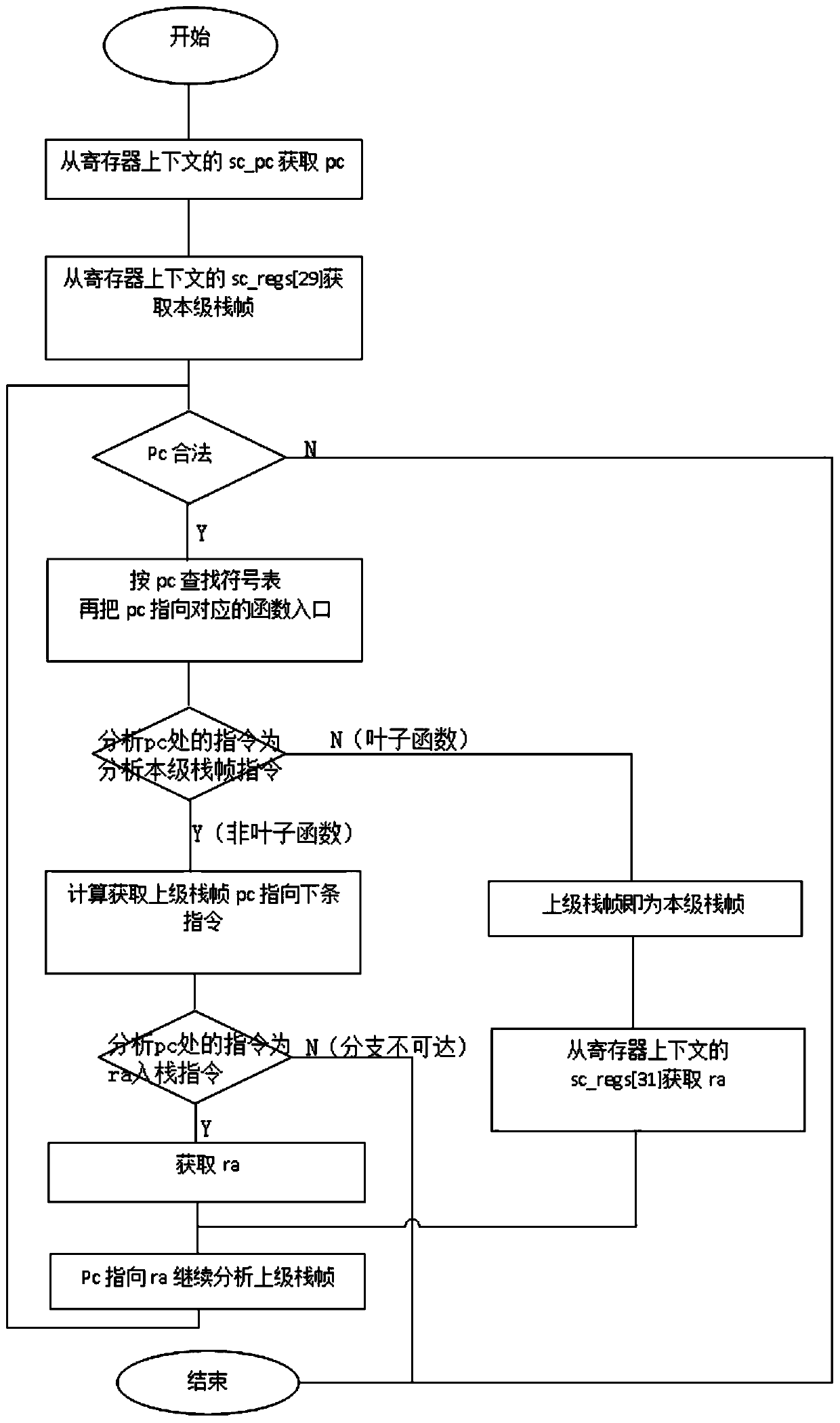

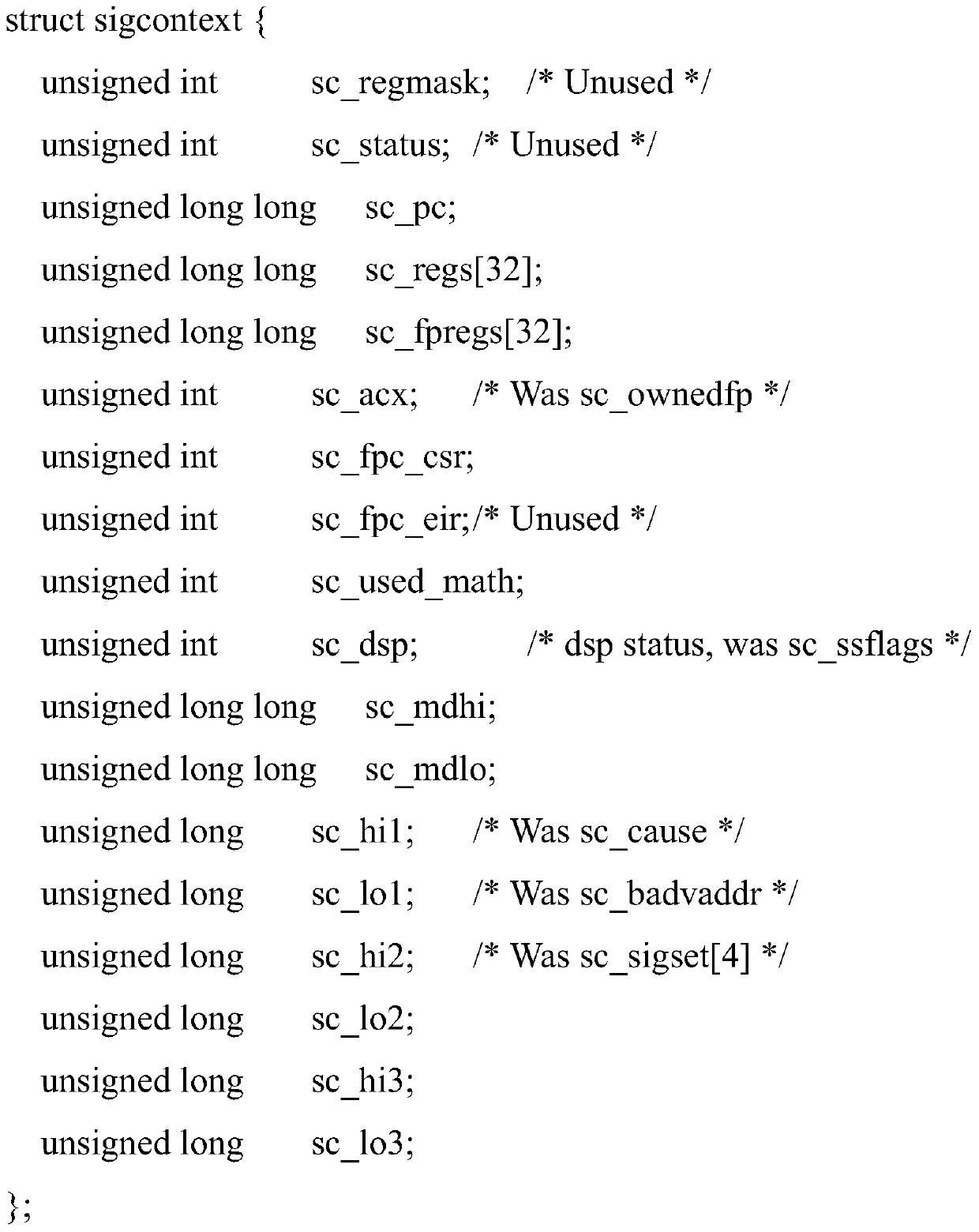

A Method for Analyzing Abnormal User Mode Processes in Linux System

ActiveCN105824749BReduce the difficulty of debuggingImprove solution efficiencySoftware testing/debuggingSoftware bugSoftware engineering

The invention discloses a method for analyzing abnormality of a user state process under a linux system. The method realizes abnormal analysis by taking over a specific signal of the process itself to obtain the abnormal task context and analyzing the task stack according to the system structure. This solution can assist software developers to quickly and accurately locate and solve software bugs.

Owner:SHANGHAI BAUD DATA COMM