Preparation method of vertical gate semiconductor device

A semiconductor and vertical gate technology, applied in the field of vertical gate semiconductor device preparation, can solve the problems of easy leakage current, ineffective diffusion of doped ions, and decreased photosensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0029] figure 2 A flow chart of a method for manufacturing a vertical gate semiconductor device provided in this embodiment, as shown in figure 2 As shown, this embodiment provides a method for fabricating a vertical gate semiconductor device, including:

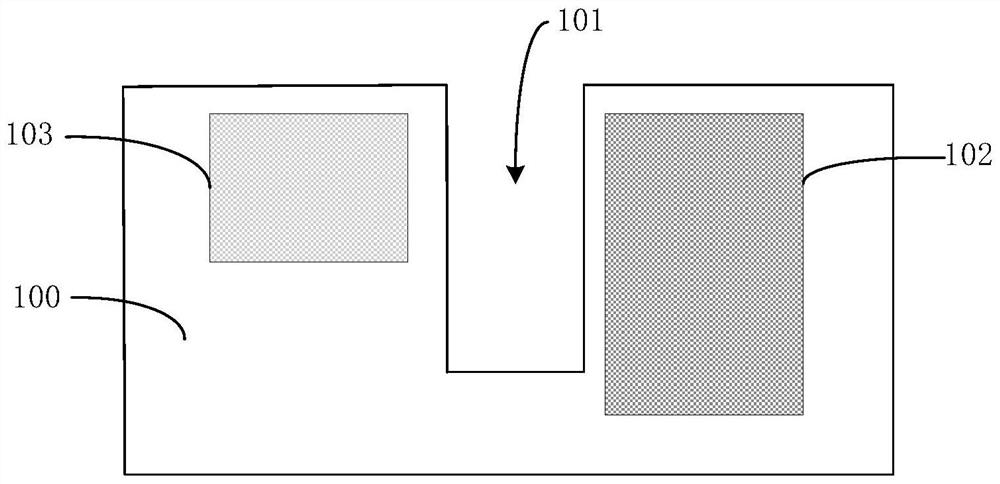

[0030] Step S1: providing a substrate, a trench is formed in the substrate, and photodiode regions and floating diffusion regions respectively located on both sides of the trench;

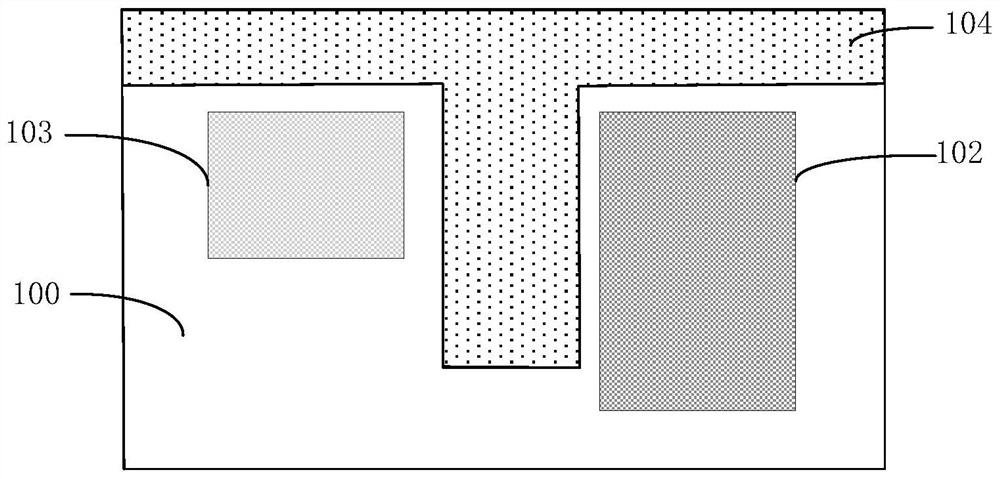

[0031] Step S2: forming an amorphous silicon layer on the substrate, the amorphous silicon layer filling the trench, and injecting a doping gas to perform in-situ doping while forming the amorphous silicon layer;

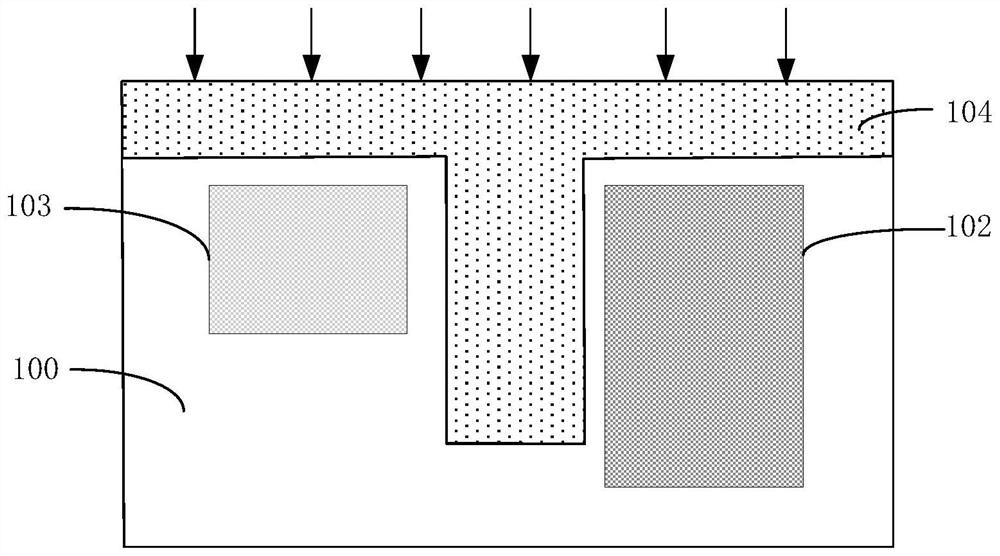

[0032] Step S3: performing thermal annealing treatment on the amorphous silicon layer, so as to transform the amorphous silicon layer into a polysilicon layer.

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com