Transposition convolution and convolution accelerator chip design method based on systolic array

A pulsating array and accelerator technology, which is applied in the calculation using the number system, using non-contact manufacturing equipment for calculation, instruments, etc., to accelerate the training process, improve the acceleration performance, and improve the image processing performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Below in conjunction with the accompanying drawings, the present invention is further described through examples, but the scope of the present invention is not limited in any way.

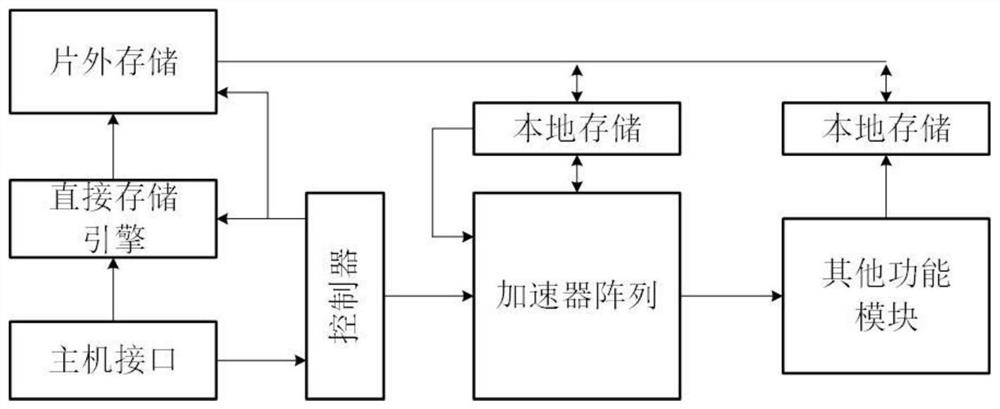

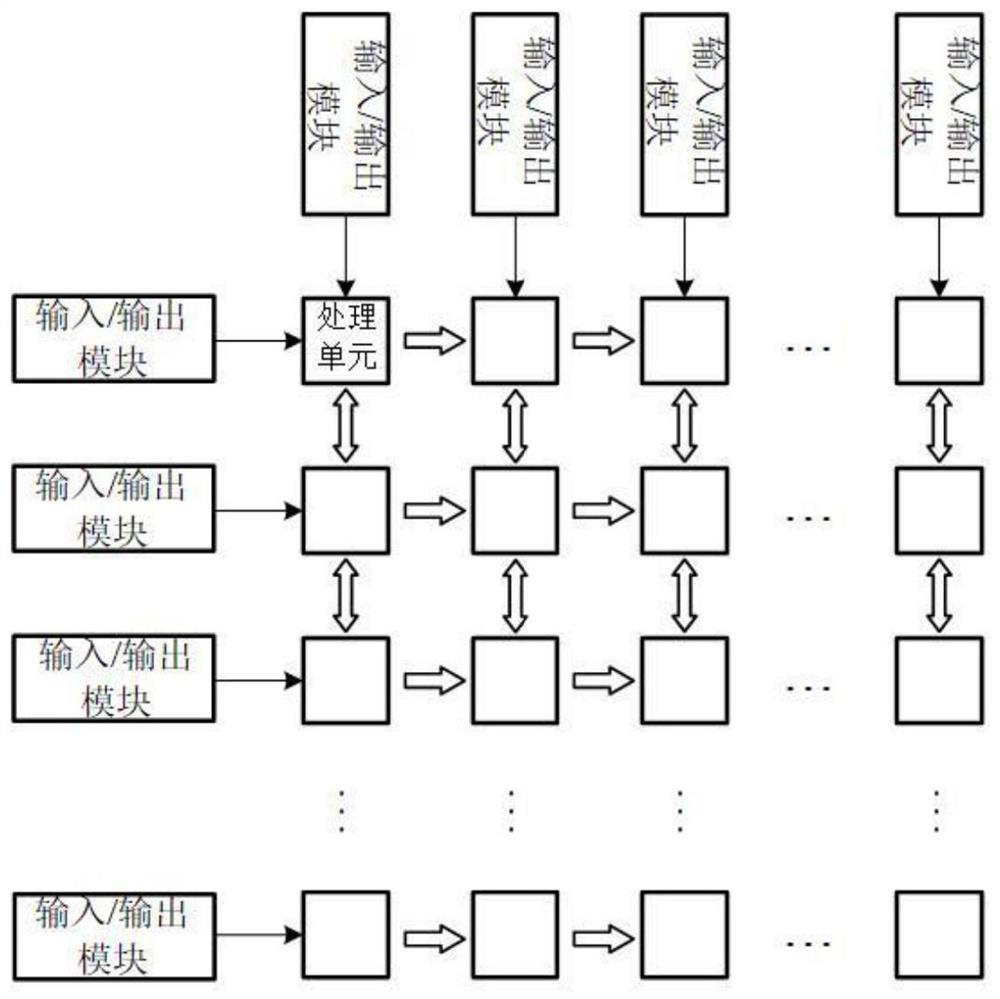

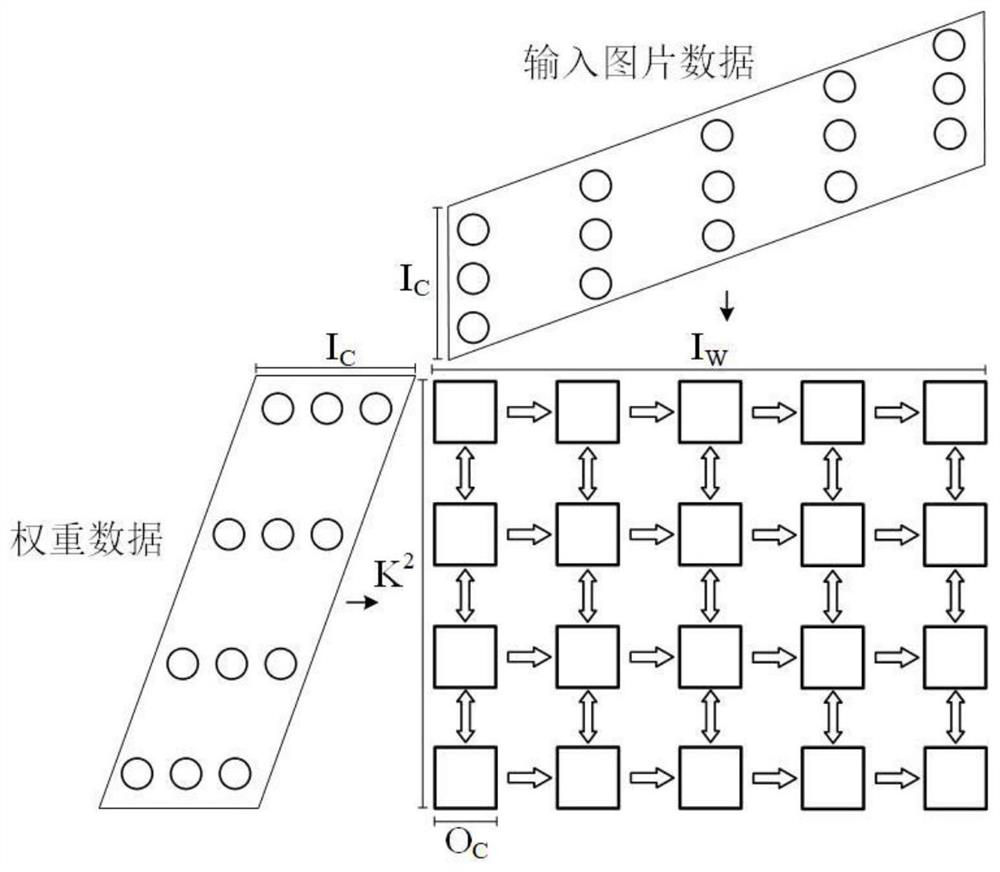

[0030] The present invention provides a systolic array-based chip accelerator architecture that can be used to accelerate transposed convolution / convolution, and a corresponding data flow scheme for mapping transposed convolution / convolution onto the accelerator array. The accelerator array is a two-dimensional array that includes multiple processing units, interconnection networks, storage structures, and input / output modules.

[0031] with (K tc ,S tc ,I tc H ,I t W ,I tc C ,O tc C ) represents a transposed convolutional layer with parameter K tc ,S tc ,I tc H ,I t W ,I tc C ,O tcC Represents the weight kernel size value, step value, input image height, input image width, input channel value and output channel value of the transposed convolution layer, respectively. with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com