Nested general-purpose computing parallel processing architecture

A general-purpose computing and parallel processing technology, applied to general-purpose stored program computers, architectures with multiple processing units, computing, etc., can solve the in-depth discussion of unfavorable architecture development, without considering communication and synchronization, and without detailed expression component logic Relational execution model and other issues to achieve the effect of flexible scalability and portability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0028] The specific implementation of the present invention will be described in detail below in conjunction with specific embodiments.

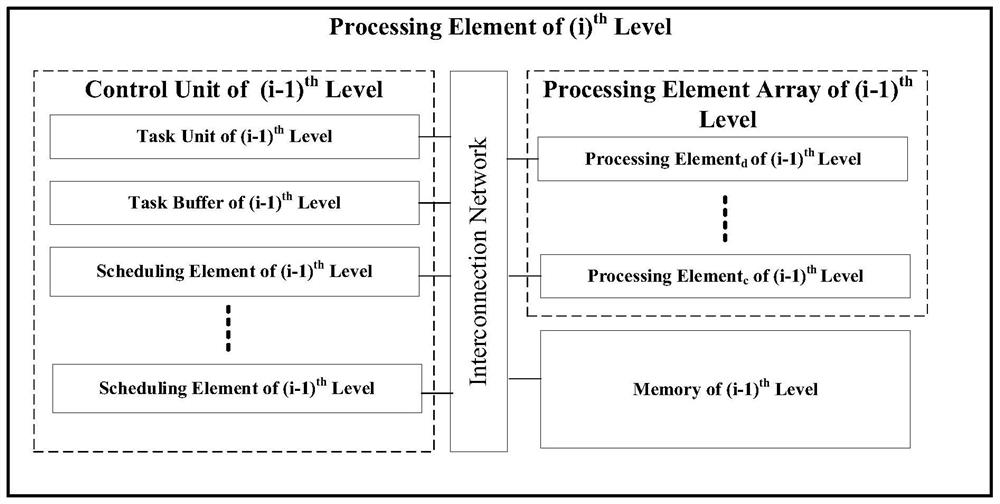

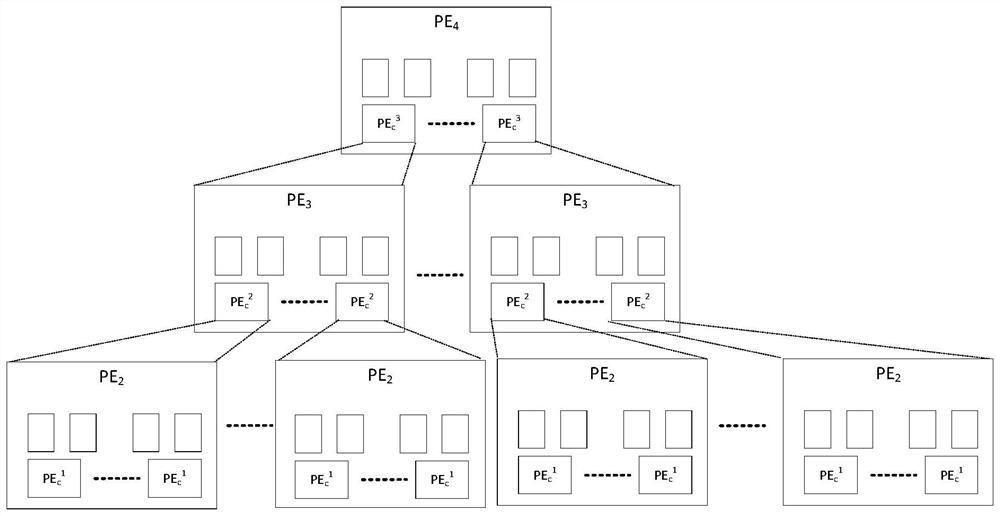

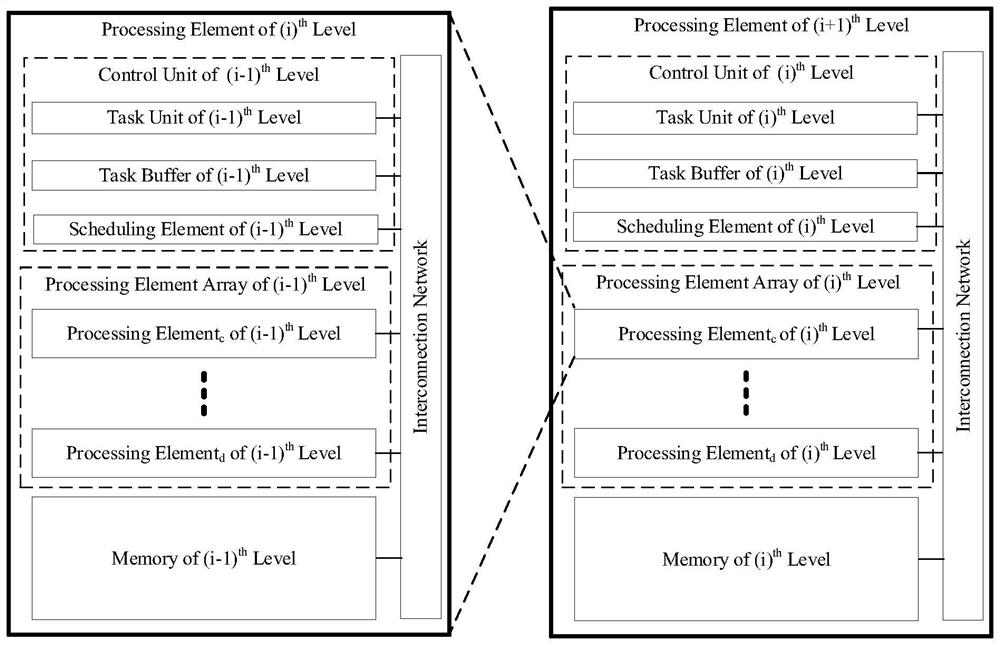

[0029] like figure 1 As shown, a nested general-purpose computing parallel processing architecture provided by an embodiment of the present invention includes a general-purpose computing task execution component, and the general-purpose computing task execution component includes multiple levels through nesting, and each level is equivalent to A number of general-purpose computing task execution components, the general-purpose computing task execution components...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap