Chip decoupling capacitor position determination method, device and system

A technology for decoupling capacitors and determining methods, applied in electrical digital data processing, CAD circuit design, special data processing applications, etc., can solve the problem of low efficiency of decoupling capacitor position confirmation, achieve position optimization, and enhance EMC performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present application, and are not intended to limit the present application.

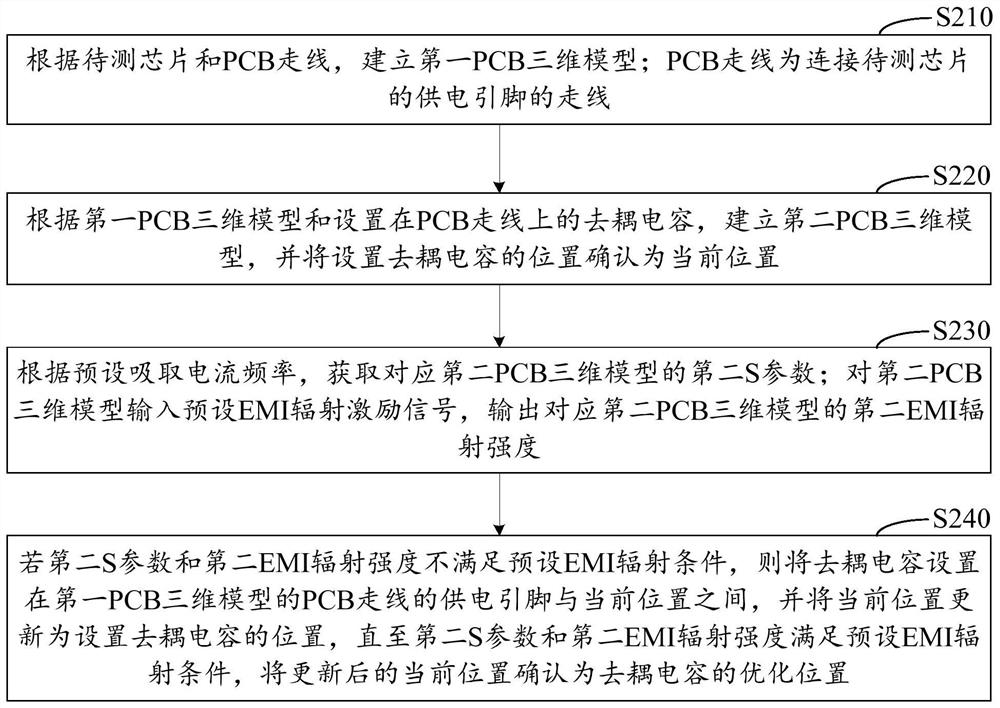

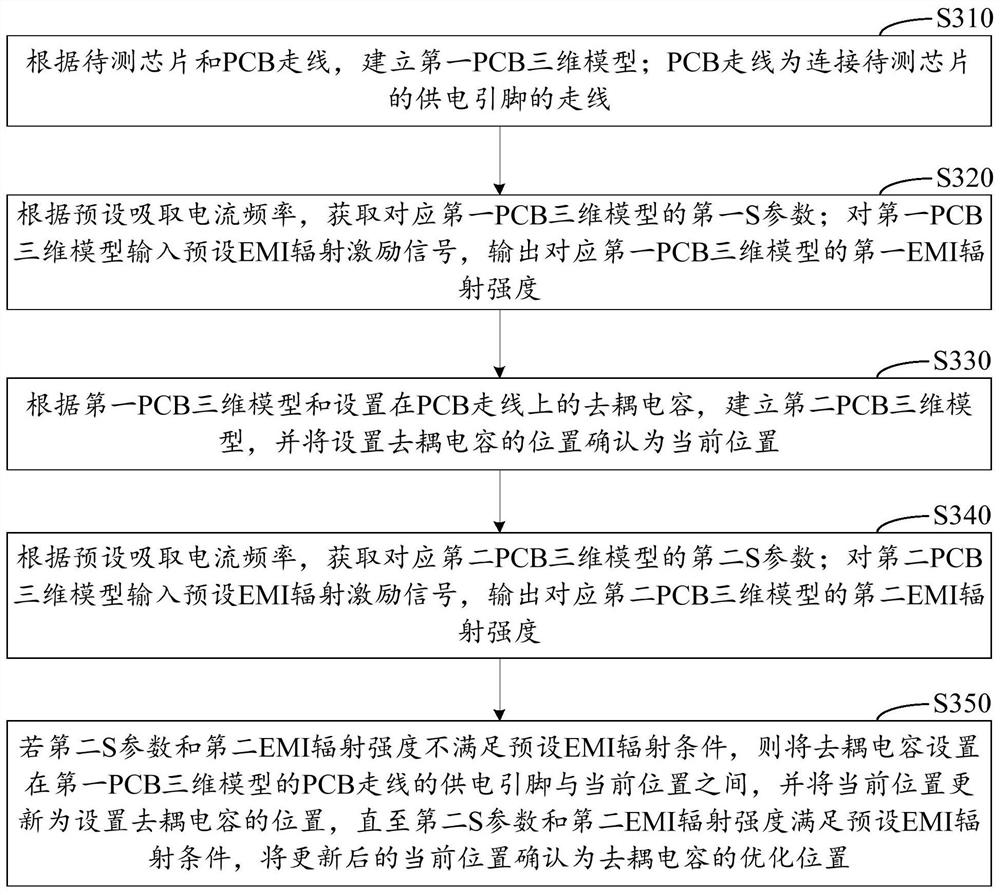

[0044]The method for determining the position of the chip decoupling capacitor provided by this application can be applied to such as figure 1 shown in the application environment. Wherein, the processing device 10 includes a processor 102 and a memory 104, and the processor 102 can be used to establish a first PCB three-dimensional model according to the chip to be tested and the PCB trace; the PCB trace is a trace connecting the power supply pin of the chip to be tested; According to the first PCB three-dimensional model and the decoupling capacitor set on the PCB trace...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More