Device and method for supporting processor silicon post debugging

A technology for processors and debugging hosts, which is applied in the detection of faulty computer hardware, functional testing, etc., to achieve the effect of reducing the complexity of debugging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the purpose, technical solution and advantages of the present invention clearer, the device and method for supporting post-silicon debugging of processors of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention rather than limit the present invention.

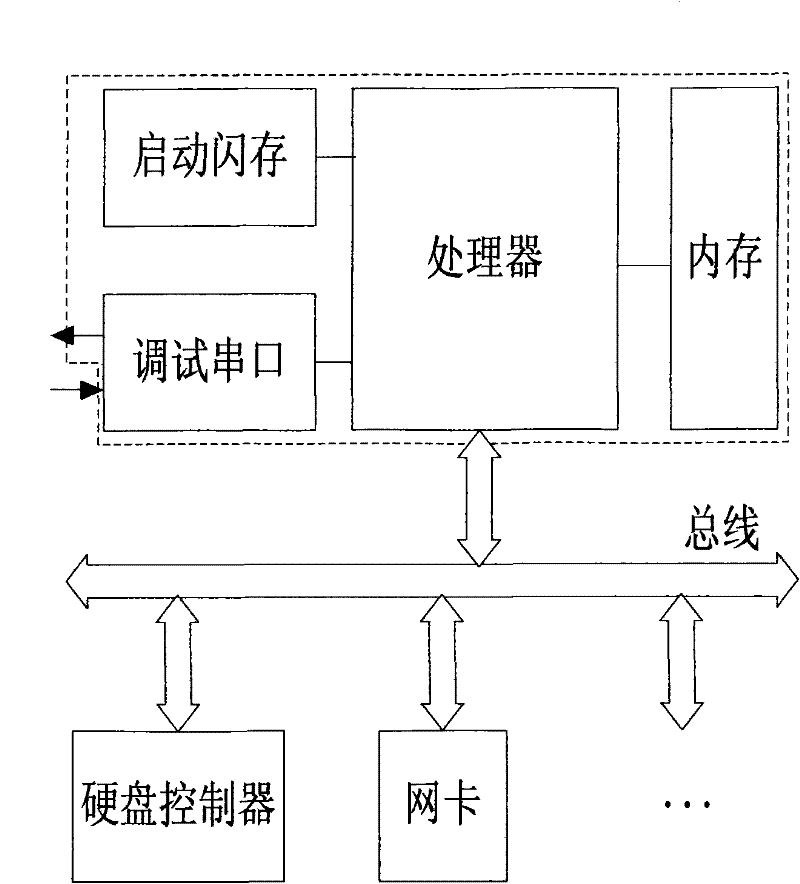

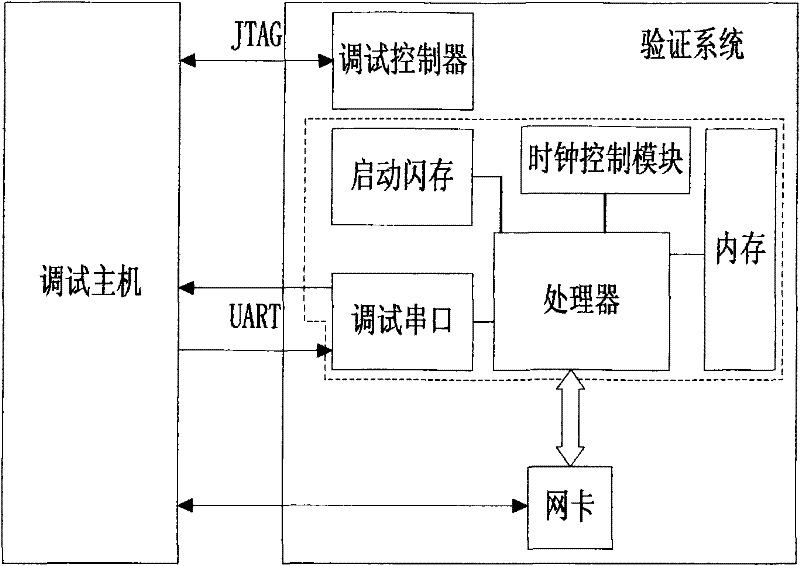

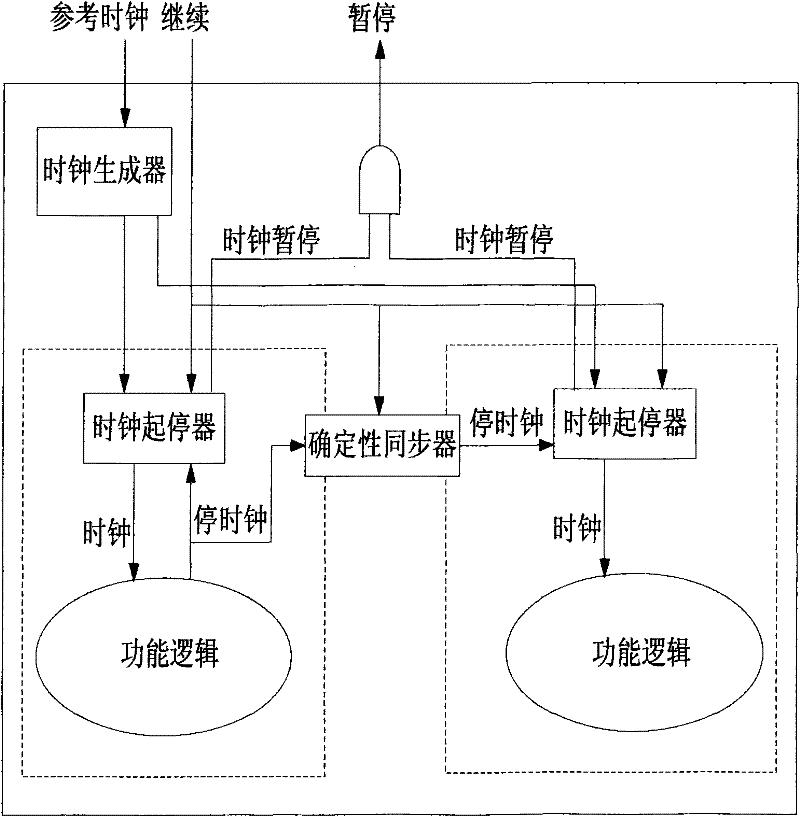

[0031] The present invention is based on figure 1 Based on the common processor system shown, the definition implements a basic system such as figure 1 As shown in the dotted line box, it is only composed of the necessary components to verify the processor, including processor core, memory, boot flash memory, serial port output and clock control module. When the verification software is limited to run within the basic system, there is no external input signal. Therefore, on the premise that the basic system is dete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More