Low-power-consumption high-precision protocol integrated circuit module packaging process

An integrated circuit and packaging process technology, which is applied in the field of low power consumption and high precision protocol integrated circuit module packaging process, can solve the problems of expanding the production defect rate of product packaging, the flying lead is susceptible to flow shock, and the flying lead is broken, etc. The probability of product fracture under force, the effect of improving production stability and ensuring stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

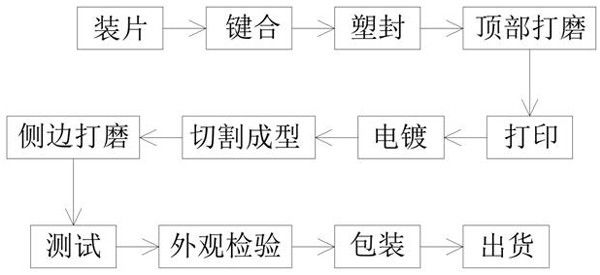

[0057] see Figure 1-Figure 10 , a low-power-consumption high-precision protocol integrated circuit module packaging process, comprising the following steps:

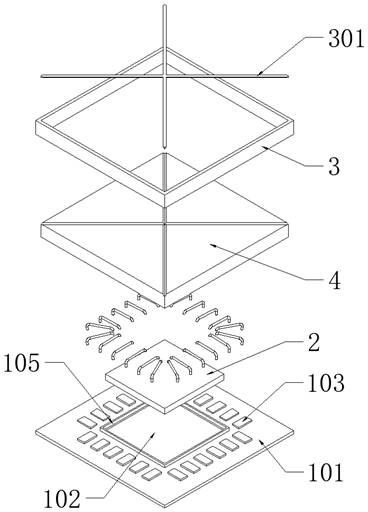

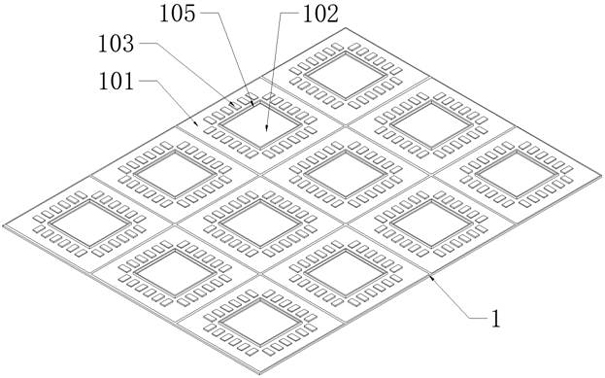

[0058] S1. Chip loading: The interior of the main board 1 is evenly divided into a plurality of circuit substrates 101, and each circuit substrate 101 is provided with a mounting position 102 in the middle of the top, and a plurality of inlaid circuit boards are arranged around the mounting position 102. The first contact 103 on the top of the substrate 101, and the second contact 104 corresponding to the plurality of first contacts 103 are evenly inlaid on the bottom of the circuit substrate 101, and the chip 2 is sequentially placed on the installation position set on the top of the circuit substrate 101 by the grasping robot arm 102 on;

[0059] S2. Bonding: use the welding manipulator to connect the connection point on the chip 2 and the contact point 103 with flying wires. After the flying wire operation is comple...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More