Module FPGA verification method and system for chip video decoding IP

A technology of video decoding and verification method, which is applied in the module FPGA verification method and system field of chip video decoding IP, which can solve problems such as increased chip tape-out cycle, reduced management efficiency, and parallel decoding errors, so as to shorten the verification cycle and improve verification speed effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

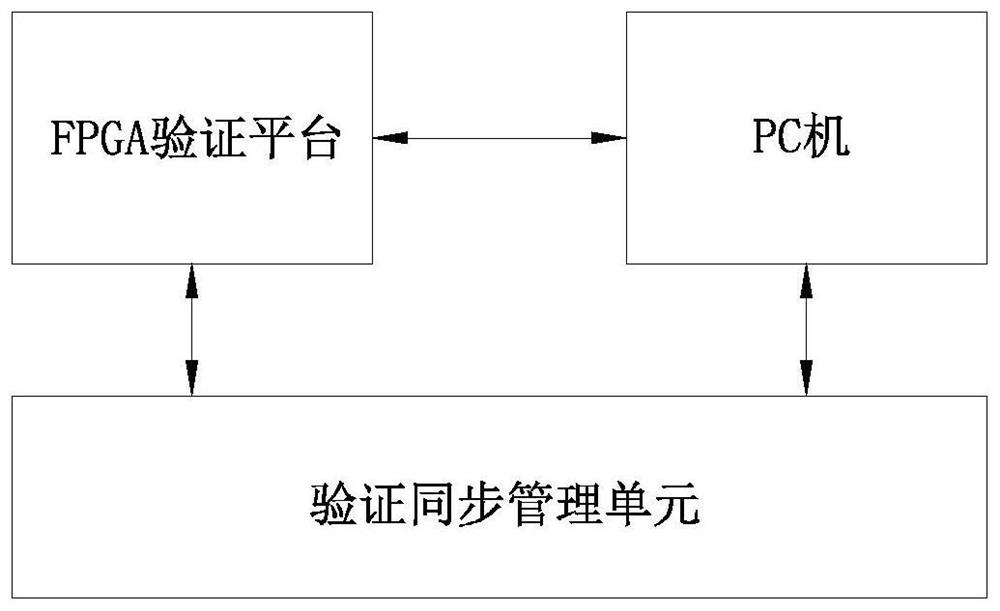

[0052] The invention proposes a chip video decoding IP module FPGA verification system, which can realize multi-channel multi-standard parallel FPGA verification of decoding IP cores without an operating system.

[0053] Described module FPGA verification system comprises FPGA verification platform, PC and the verification synchronous management unit that corresponding FPGA verification platform and PC are set, see figure 1 shown. The video decoding firmware of the decoding IP core is arranged on the FPGA verification platform. The video decoding firmware is used to initialize decoding related parameters and configure the initial state of decoding hardware. The PC is provided with a result comparison unit, and the result comparison unit can perform multiple communication with the aforementioned video decoding firmware.

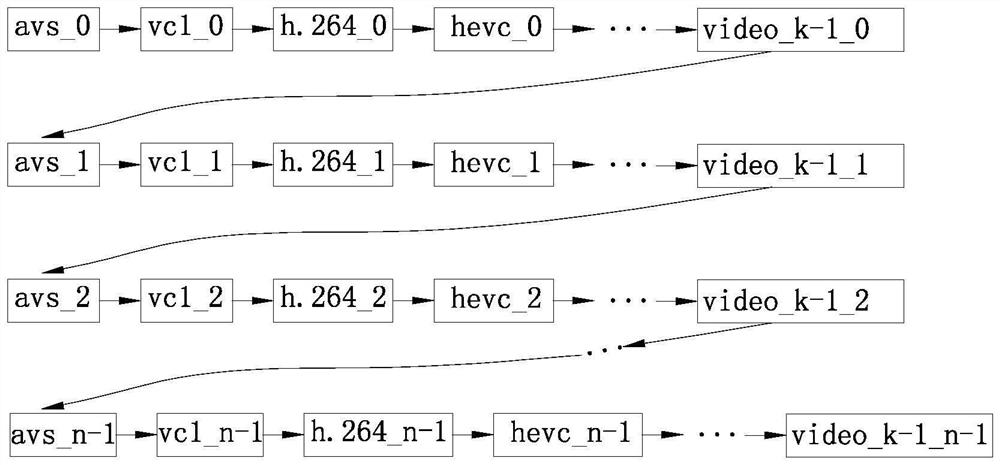

[0054] Utilize above-mentioned system to carry out the method for multi-channel multi-standard parallel verification of decoding IP core and comprise the st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More