Design method of contact type card verification system based on FPGA (field programmable gate array)

A verification system and card design technology, applied in computing, instruments, electrical digital data processing, etc., can solve the problems of high cost of chip tape-out, insufficient verification reliability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

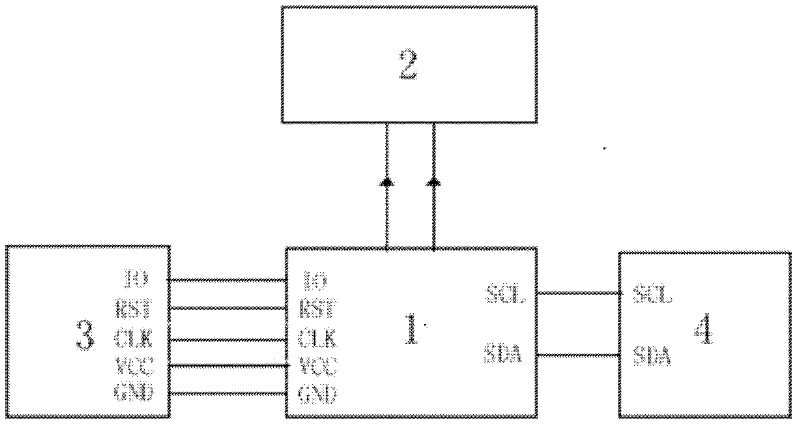

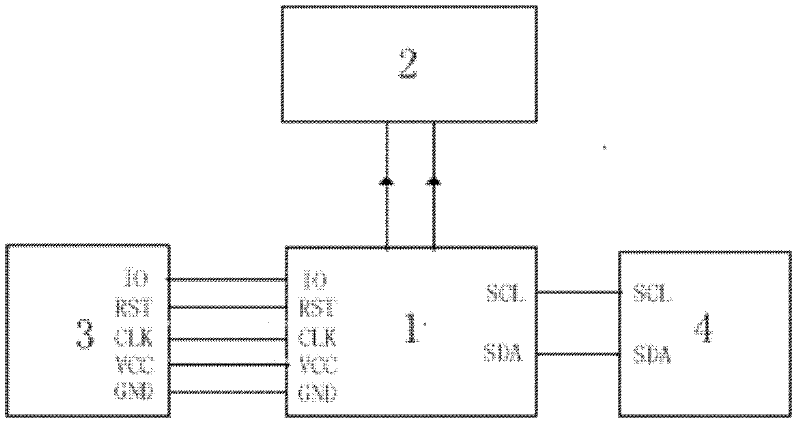

[0034] A design method of a FPGA-based contact card verification system, such as figure 1 , figure 2 As shown, the steps are as follows:

[0035] 1) Select FPGA as the design platform for the verification system;

[0036] 2) Transplant the contact card design on the FPGA platform, mainly including IO processing and IP replacement:

[0037] IO processing: According to the contact card design specification, modify the IO port of the contact card design in the FPGA platform, so that the IO port conforms to the interface specification in the ISO-7816 protocol;

[0038] IP replacement: replace the IP core based on the integrated circuit design process in the contact card design with the IP core suitable for the FPGA platform according to the functions realized by the IP core;

[0039] 3) Build the verification system environment:

[0040] The verification system environment includes a card reader conforming to the ISO-7816 protocol, EEPROM data storage chip, FPGA platform for ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More