Multi-chip normally-mounted reset wafer level packaging structure and method

A multi-chip, level packaging technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems that the chip surface cannot be protected, the chip process is difficult, and the packaging volume is large, so as to reduce the difficulty of cutting , Improving packaging efficiency and simplifying the packaging process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the drawings in the embodiments of the present invention.

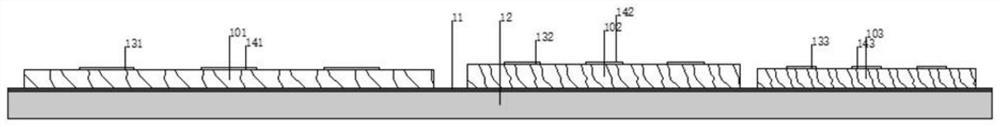

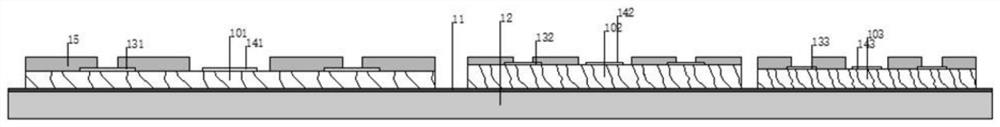

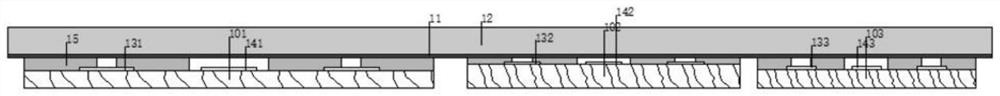

[0038] 1. Multi-chip reset layout, using patch technology to place different types of chips (the number of chips can be flexibly matched, here is an example of 3 chips (101, 102, 103) placed on the substrate 12 with a temporary bonding film 11 , the front of the chip faces up, and the back is attached to the temporary bonding film on the substrate; the front of the chip contains electrodes (each chip includes electrodes 131, 132, 133), key functional areas (such as the IDT area of the surface acoustic filter, the bulk The resonator area of the acoustic wave filter includes key functional areas (141, 142, 143) and other areas in different chips. Taking a group of 3 chips as an example, multiple groups are regularly arranged on the substrate 12 to fill the substrate. shall p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More