Logic gate based on neuromorphic device

A neuromorphic and logic gate technology, applied in the field of logic gates, can solve the problems of poor applicability, low neural network integration, and high power consumption, and achieve the effects of good applicability, reduced power consumption, and good integration.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

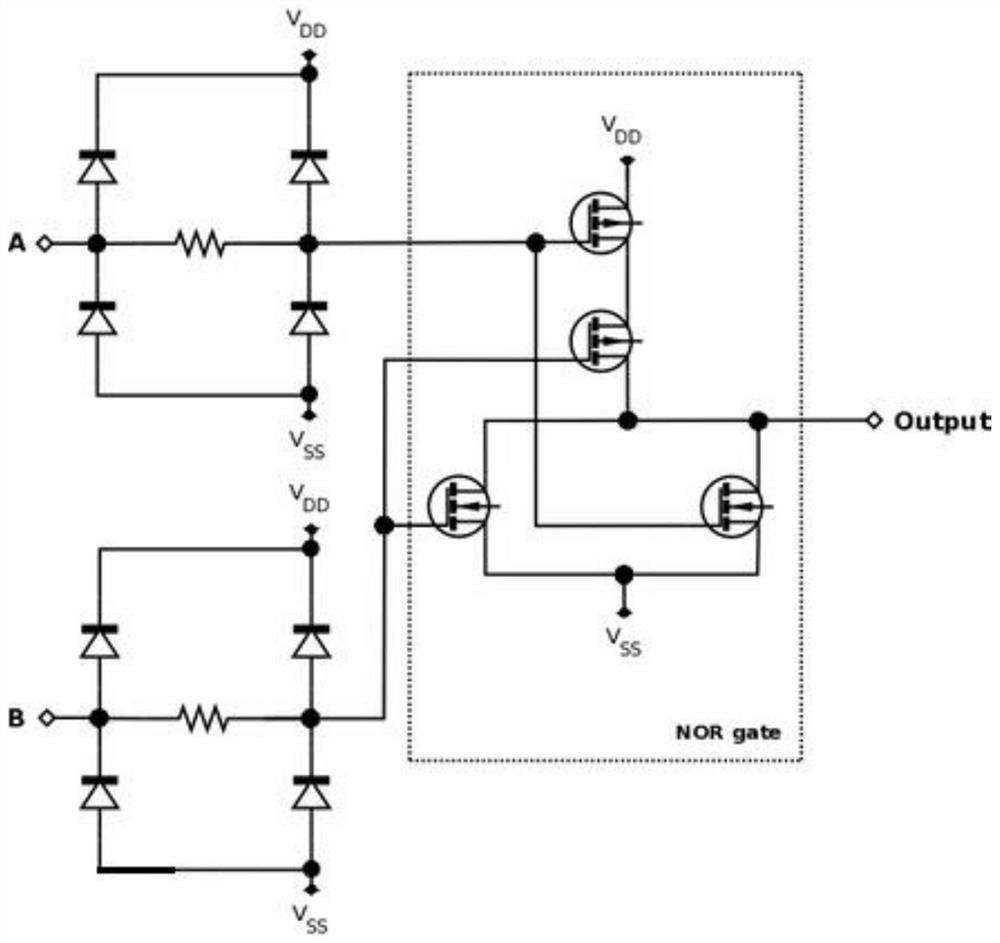

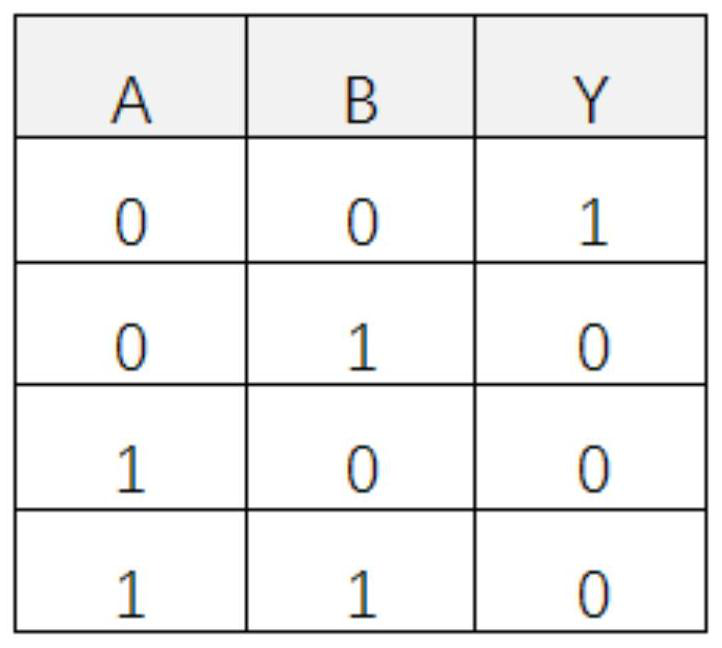

[0046] In this embodiment, both the first neuron A and the second neuron B are inhibitory neurons, which suppress the activation of the connected neurons by issuing inhibitory signals when outputting a high level, the third neuron C and the fourth neuron Element D has a fundamental signal of constant 1.

[0047] The NOR gate logic is implemented based on the logic gates of neuromorphic devices, and the following operations are performed:

[0048] When both the first neuron A and the second neuron B output a high level, the third neuron C and the fourth neuron D are inhibited, the membrane potential is lower than the second firing threshold, the output is low, and the fifth neuron Y When the membrane potential is less than the third release threshold, the output is low level;

[0049] When the first neuron A outputs a high level and the second neuron B outputs a low level, the third neuron C is inhibited, the membrane potential is lower than the second firing threshold, the ou...

Embodiment 2

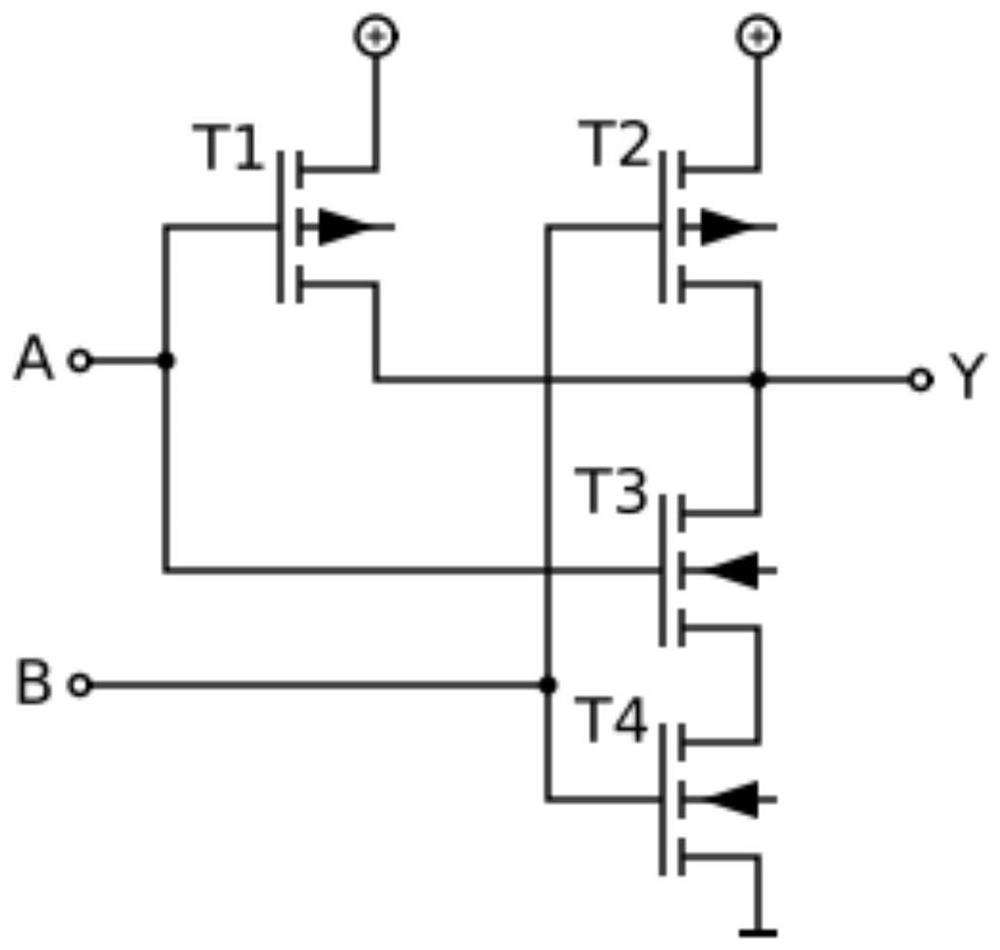

[0063] In this embodiment, both the first neuron A and the second neuron B are inhibitory neurons, which suppress the activation of the connected neurons by issuing inhibitory signals when outputting a high level, the third neuron C and the fourth neuron Element D has a fundamental signal of constant 1.

[0064] The NAND gate logic is implemented based on the logic gate of the neuromorphic device, and the following operations are performed:

[0065] When both the first neuron A and the second neuron B output a high level, the third neuron C and the fourth neuron D are inhibited, the membrane potential is lower than the second firing threshold, the output is low, and the fifth neuron Y When the membrane potential is less than the third release threshold, the output is low level;

[0066] When the first neuron A outputs a high level and the second neuron B outputs a low level, the third neuron C is inhibited, the membrane potential is lower than the second firing threshold, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More