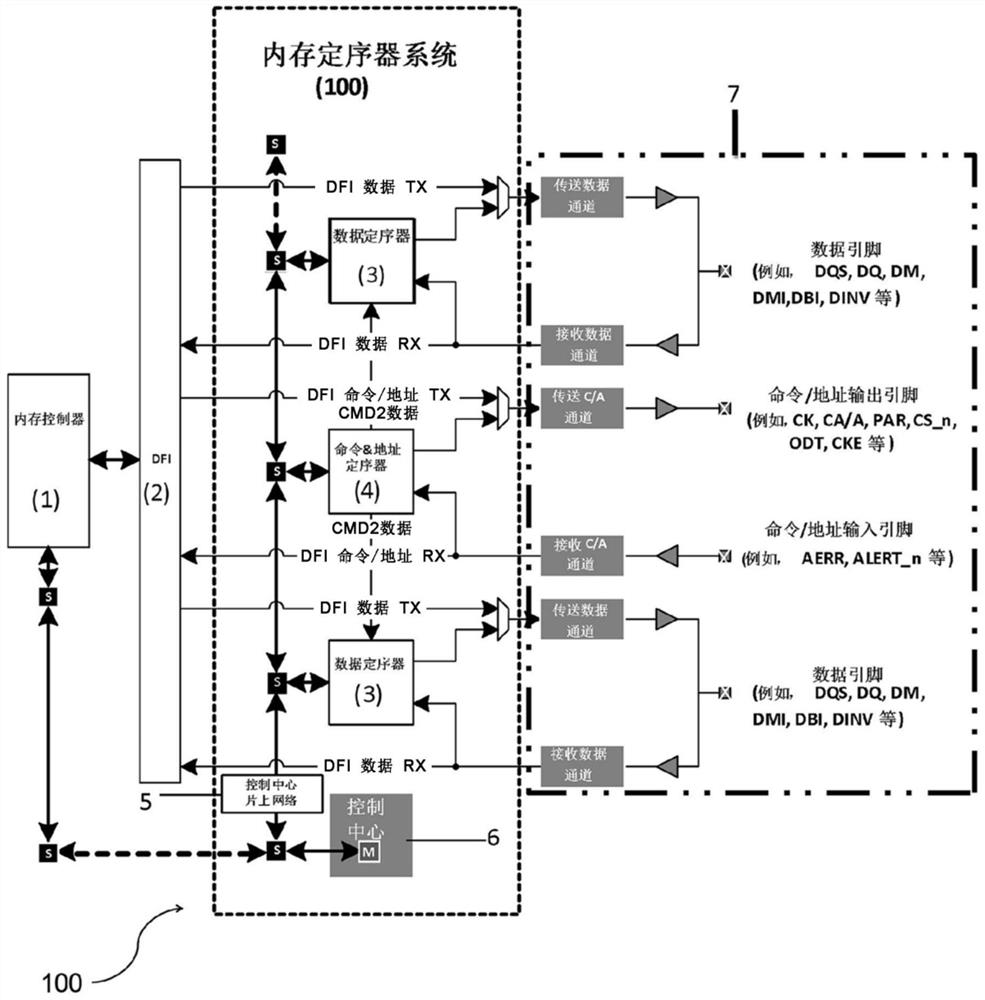

Memory sequencer system and memory sequencing method applying same

A sequencer, memory technology, applied in the field of memory management

- Summary

- Abstract

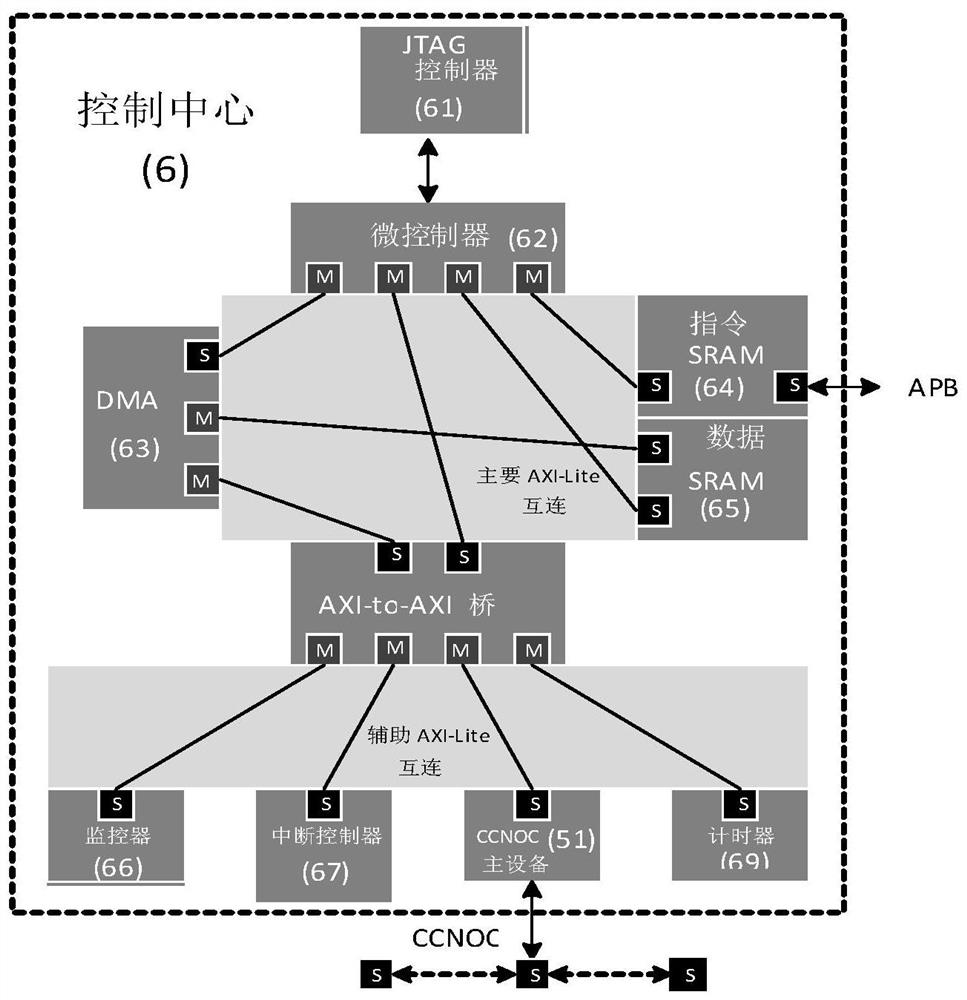

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example

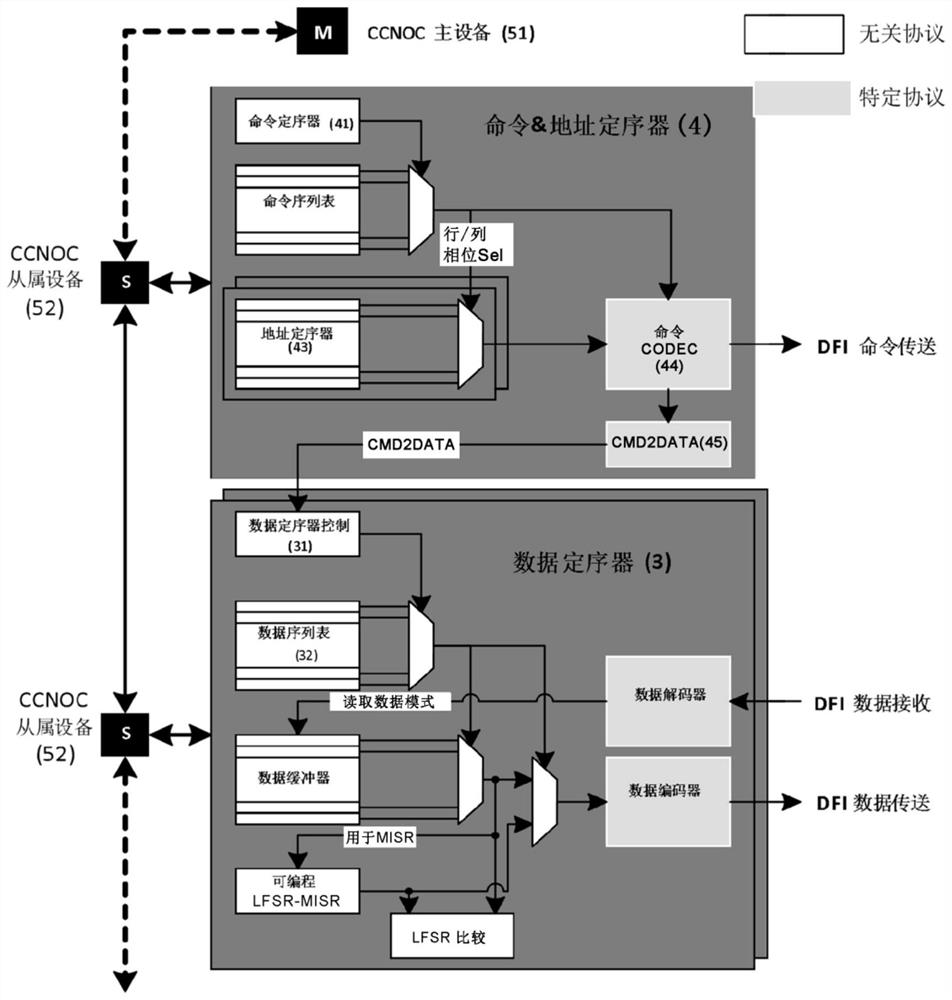

[0065] Generate command, address and data sequences

[0066] Table 1:

[0067] name symbol #byte describe delay count delay 8 Number of DFI delay cycles to apply before / after the command cycle pre / post delay post_delay 1 If 1, the delay will be applied after the command cycle line command phase 0 row_sel_p0 3 Select the address sequencer corresponding to phase P0 command line phase 1 row_sel_p1 3 Select the address sequencer corresponding to phase P1 column command phase 0 col_sel_p0 3 Select the address sequencer corresponding to phase P0 Column Command Phase 1 col_sel_p1 3 Select the address sequencer corresponding to phase P1 Loop Counter Selection loop_select 2 Select 1 of 4 loop counters branch equal to zero pointer bez 3 If the selected loop counter is 0, the next table entry index branch not equal to zero pointer bnz 3 next table entry index if selected loop counter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More