MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device integrated with PiN structure temperature sensor and preparation method of MOSFET device

A temperature sensor and device technology, applied in the field of microelectronics, can solve the problems affecting the application reliability of the device, the characteristics are deteriorated, and the thermal characteristics of the device cannot be accurately obtained, and the effect of improving the thermal reliability is achieved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

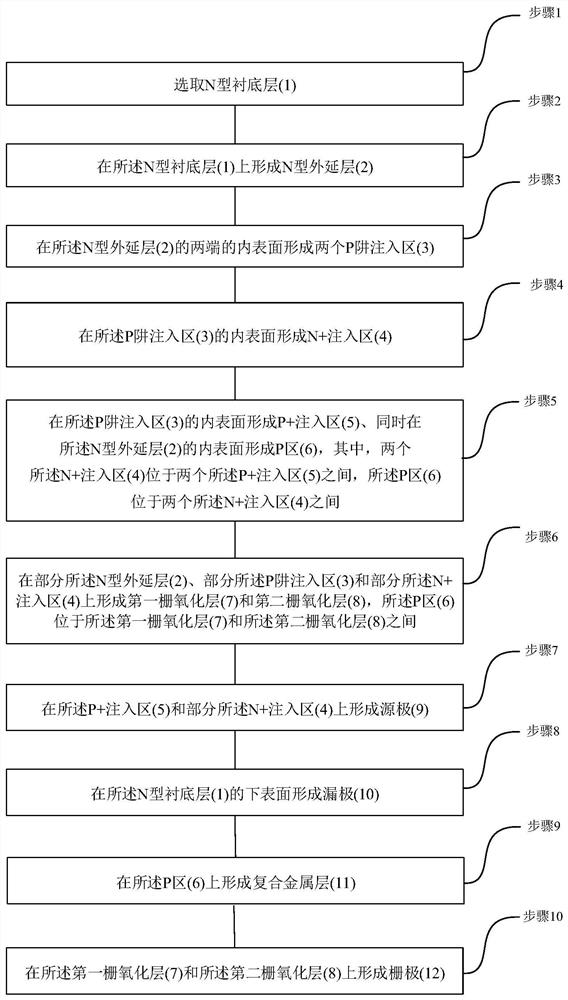

[0051] See figure 1 , Figures 2a-2j , figure 1 A flow chart of a method for manufacturing a MOSFET device with an integrated PiN structure temperature sensor provided by an embodiment of the present invention, Figures 2a-2j A process schematic diagram of a MOSFET device integrating a PiN structure temperature sensor provided by an embodiment of the present invention. The invention provides a method for preparing a MOSFET device with an integrated PiN structure temperature sensor, the preparation method comprising the following steps:

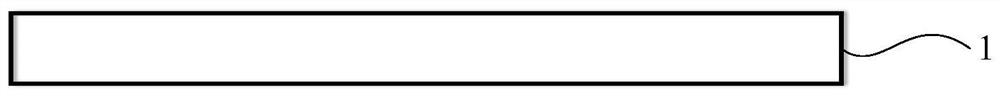

[0052] Step 1, see Figure 2a , select the N-type substrate layer 1 .

[0053] Specifically, the N-type substrate layer 1 is selected, and the N-type substrate layer 1 is cleaned using an RCA cleaning standard.

[0054] Further, the N-type substrate layer 1 is an N-type 4H-SiC substrate layer.

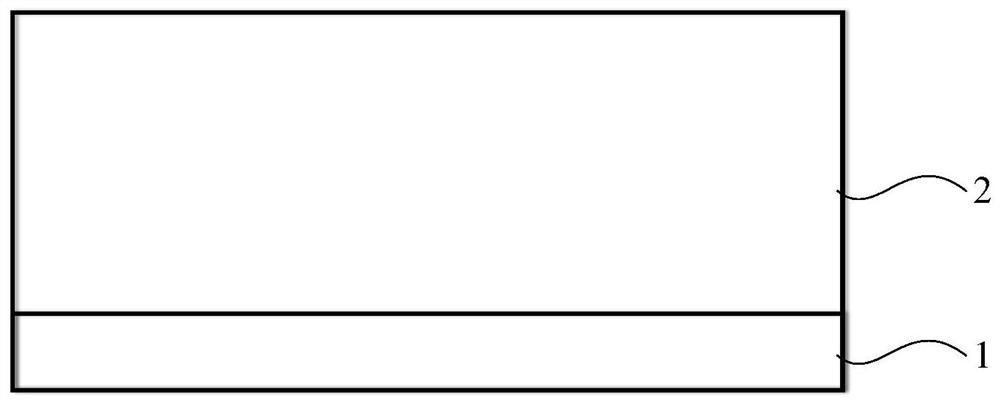

[0055] Step 2, see Figure 2b , forming an N-type epitaxial layer 2 on the N-type substrate layer 1 .

[0056] Specifically, an N-type epitaxi...

Embodiment 2

[0098] See image 3 , image 3 A schematic structural diagram of a MOSFET device integrating a PiN structure temperature sensor provided by an embodiment of the present invention. The present invention proposes a MOSFET device integrating a PiN structure temperature sensor. The MOSFET device is prepared by the preparation method described in Embodiment 1. The MOSFET device includes:

[0099] N-type substrate layer 1;

[0100] The N-type epitaxial layer 2 is located on the N-type substrate layer 1;

[0101] Two P-well injection regions 3 are respectively located at both ends of the N-type epitaxial layer 2;

[0102] Two N+ implantation regions 4 are respectively located in the two P well implantation regions 3;

[0103] Two P+ implant regions 5 are respectively located in the two P well implant regions 3, and the two N+ implant regions 4 are located between the two P+ implant regions 5;

[0104] The P region 6 is located in the N-type epitaxial layer 2, and the P region 6 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More