Semiconductor packaging structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as limited application fields, decreased accuracy, environmental pollution, etc., to increase electrical performance, The effect of reducing package height and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

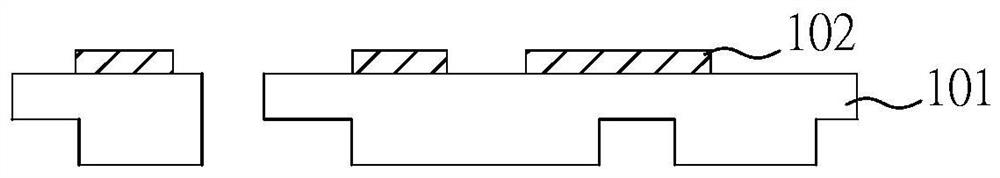

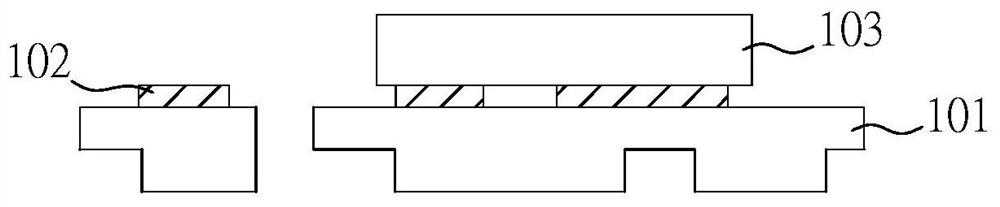

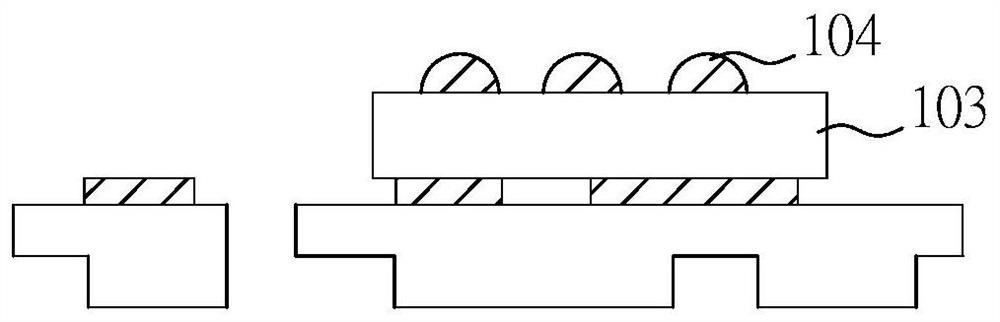

[0053] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. In the following description, many specific details are set forth to facilitate a full understanding of the present invention, but the present invention can also be implemented in other ways different from those described herein, and those skilled in the art can do so without departing from the connotation of the present invention. Similar promotion, therefore, the present invention is not limited by the specific embodiments disclosed below.

[0054] Please refer to figure 2 As shown, the first state embodiment of the semiconductor package structure 2 of the preferred embodiment of the present invention includes a first stack structure 20 and a second stack structure 30 . The second stack structure 30 is stacked on the first stack structure 20 . The first stacked str...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More