Back-end compiler implementation method and device based on array analysis primitive structure

An implementation method and compiler technology, applied in the direction of compiler construction, parser generation, code compilation, etc., to achieve the effect of clear thinking, convenient operation, and good scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

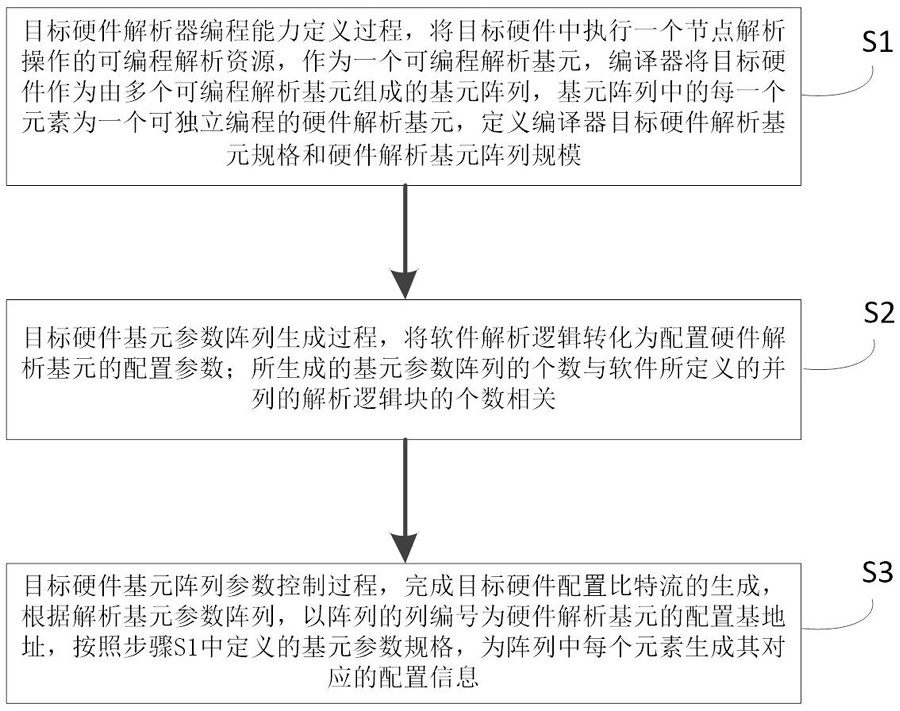

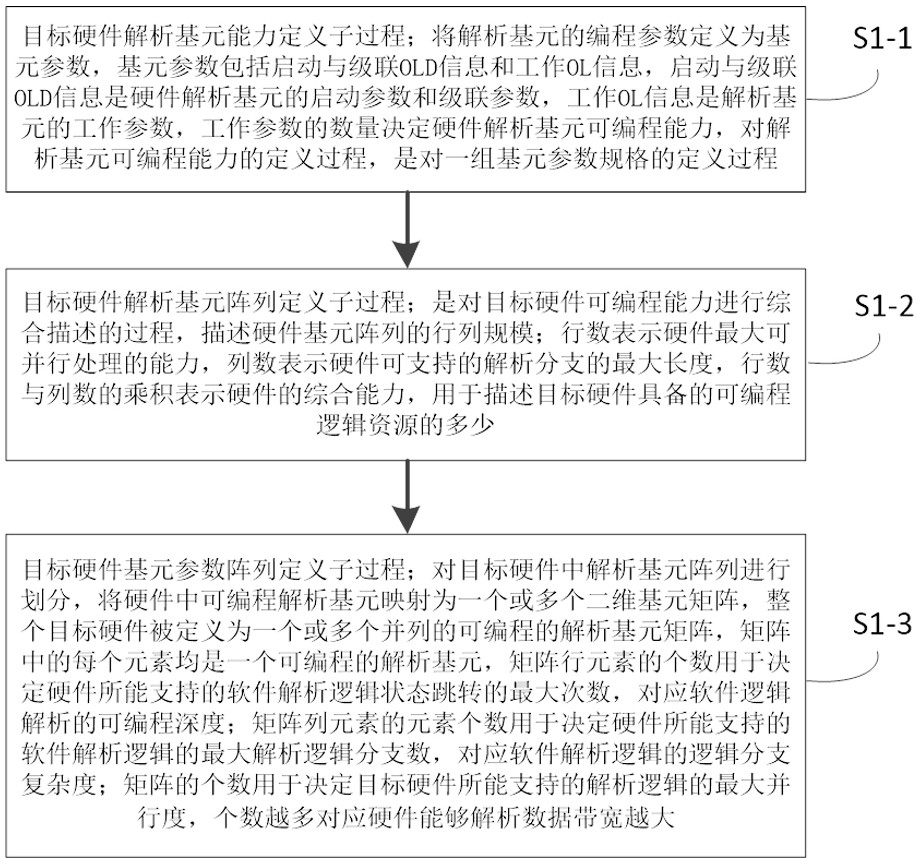

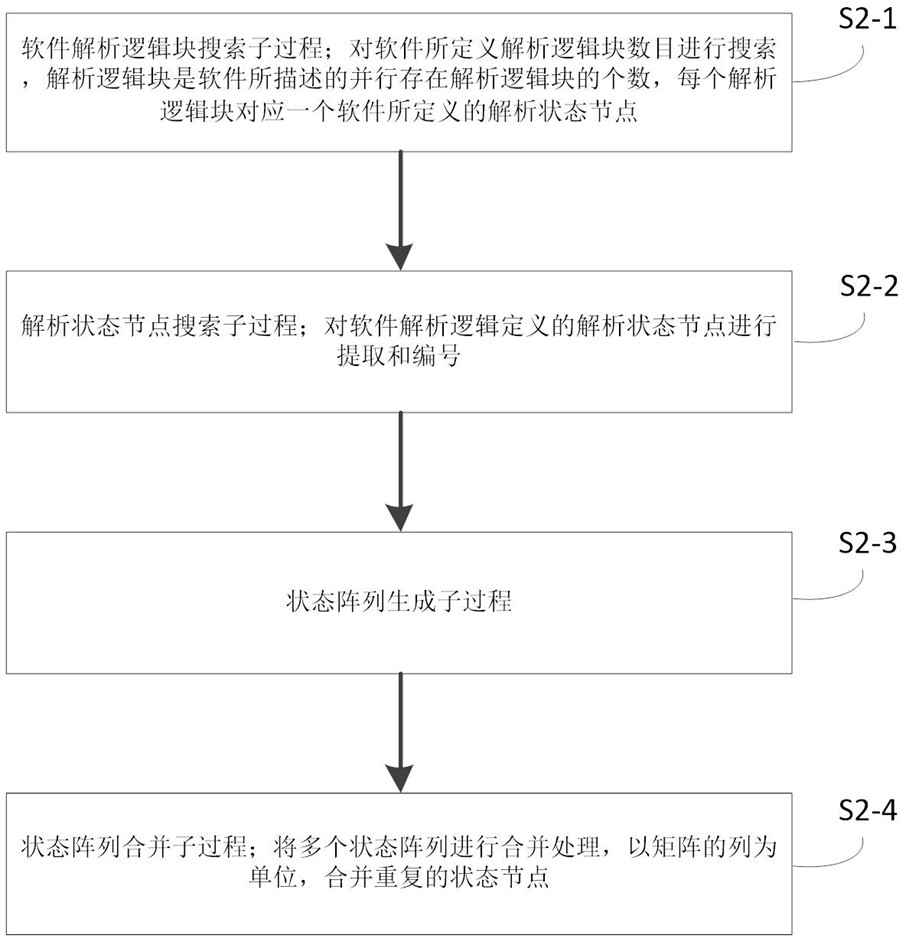

[0038] Step S3: the target hardware primitive array parameter control process, and the generation of the target hardware configuration bit stream is completed. According to the parsing primitive parameter array and parsing parameter list generated in step S2, the column number of the array is used as the configuration base address of the hardware parsing primitive, according to the parameter format of starting and cascading OLD information and working OL information defined in step S1 , to generate its corresponding configuration information for each element in the array. Step S3 is responsible for generating a final parsing primitive parameter array based on the parsing state matrix and parsing parameter list, and merging all parameters in the array into a final parsing primitive parameter format defined by the hardware in units of columns Configure the bit stream, and configure the configuration bit stream into the target hardware to complete the programming operation of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More