Simulation method, system, storage medium and device for gate-level circuit

A gate-level circuit and simulation method technology, applied in CAD circuit design, geometric CAD, special data processing applications, etc., can solve the problems of increasing simulation time and complexity, reducing simulation efficiency, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

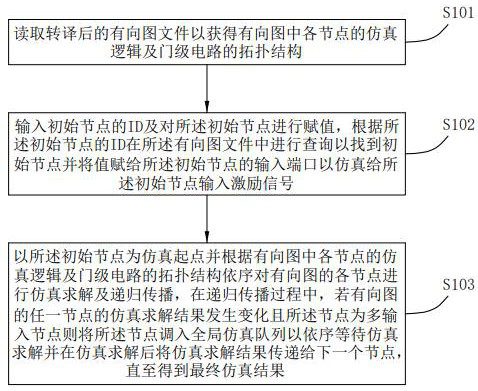

[0047] see figure 1 , the first embodiment of the present invention provides a method for simulating a gate-level circuit, including steps S101 to S103.

[0048] S101, read the translated directed graph file to obtain the simulation logic of each node in the directed graph and the topology structure of the gate-level circuit.

[0049] It should be noted that for the gate-level circuit topology: the translated directed graph file can already represent the circuit as a directed graph, each graph node represents a gate, and each gate has a unique ID attribute to use It is used to find its position in the directed graph, so to obtain the topology of the gate-level circuit, it is only necessary to read the directed graph represented by the translation file.

[0050] Specifically, the step of reading the translated directed graph file to obtain the simulation logic of each node in the directed graph and the topology of the gate-level circuit specifically includes:

[0051] Read th...

Embodiment 2

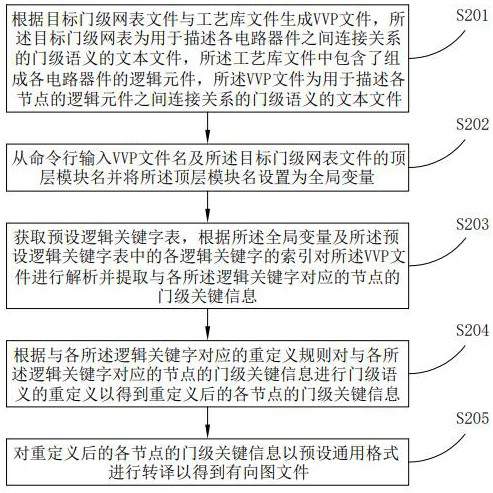

[0094] like figure 2 As shown, this embodiment is a method for translating a gate-level circuit, which is used to translate the gate-level netlist file to obtain the directed graph file in the first embodiment, including steps S201-S205.

[0095] S201, generating a VVP file according to a target gate-level netlist file and a process library file, where the target gate-level netlist is a text file used to describe the gate-level semantics of connection relationships between circuit devices, and the process library file contains The logic elements that compose each circuit device are described, and the VVP file is a text file used to describe the gate-level semantics of the connection relationship between the logic elements of each node.

[0096] It should be noted that the VVP file in the embodiment of the present invention may be generated by the Icarus Verilog simulator, and the Icarus Verilog simulator will generate an intermediate file VVP file when simulating the circuit ...

Embodiment 3

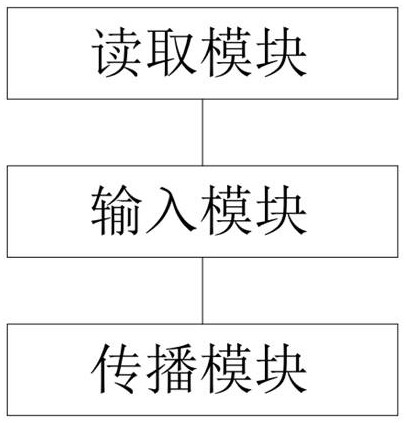

[0159] Please refer to image 3 , this embodiment provides a gate-level circuit simulation system, including:

[0160] Reading module: used to read the translated directed graph file to obtain the simulation logic of each node in the directed graph and the topology of the gate-level circuit.

[0161] The reading module is also used for:

[0162] Reading the translated directed graph file, the directed graph file includes a first directed graph file and a second directed graph file;

[0163] Build a first preset global dictionary, traverse the first directed graph file to extract the simulation logic of the combinational logic udp node and the sequential logic udp node and store it in the first preset global dictionary, where the first preset The global dictionary can be the global dictionary GUDPDefMap;

[0164] A second preset global dictionary is created, and the second directed graph file is traversed to analyze and obtain the topological structure of the gate-level circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More