Power supply monitoring circuit and switching power supply

A technology of power monitoring and power supply voltage, applied in the direction of electrical components, output power conversion devices, etc., can solve the problems of increasing the chip area, not completely solving the problem of low voltage operation, increasing the overall power consumption of the system, and achieving small footprint, The effect of ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0051] In this embodiment, the reset indication signal is valid when it is in a low level state.

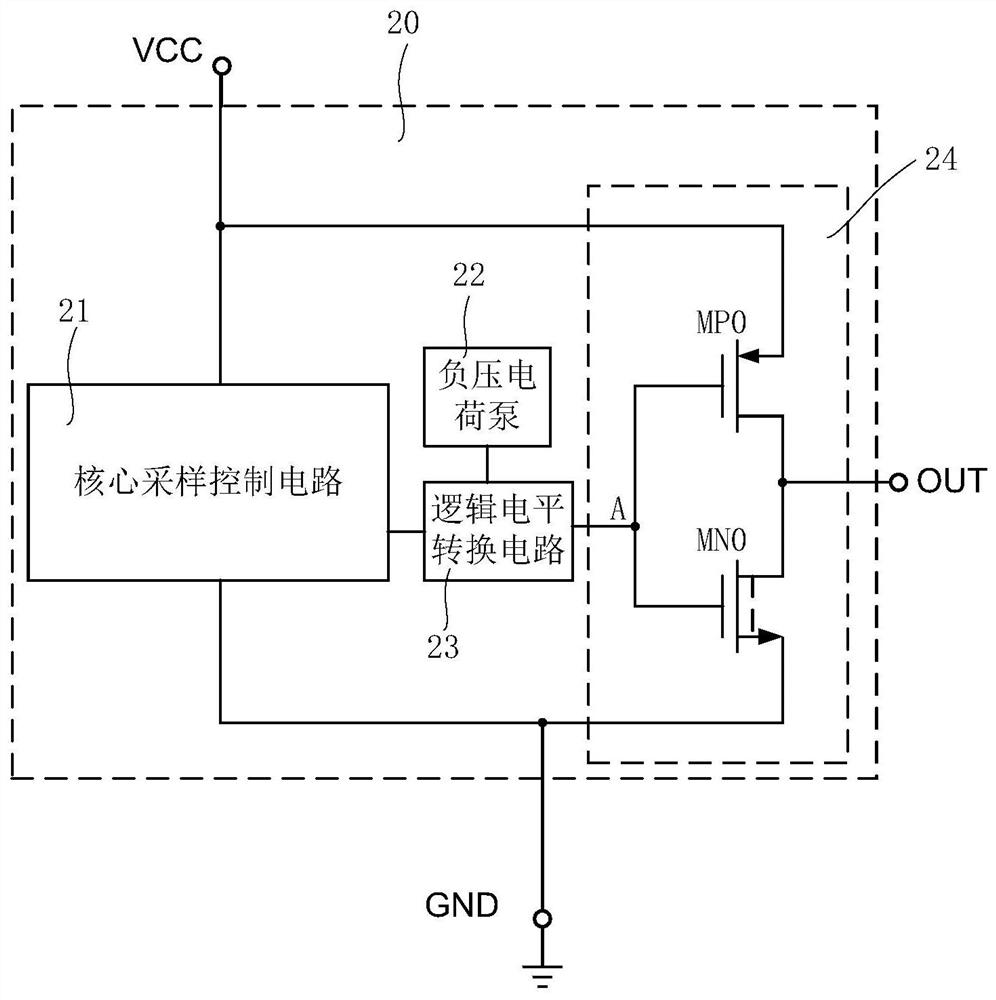

[0052] refer to image 3 , the output module 24 includes: a first switch tube MP0 and a second switch tube MN0. The first switch tube MP0 and the second switch tube MN0 are sequentially connected in series between the power supply voltage VCC input terminal and the reference ground GND, the gate of the first switch tube MP0 receives the first control signal or receives the second control signal A, and the second switch tube The gate of the transistor MN0 receives the second control signal A. Wherein, the first switch tube MP0 is an enhancement mode PMOS transistor, and the second switch tube MN0 is a depletion mode NMOS transistor. And the output module 24 outputs a reset indication signal to the output terminal OUT at the drain of the second switch tube MN0.

[0053] Further, in this embodiment, the charge pump 22 generates a reference voltage with a negative voltage VSS.

...

Embodiment 2

[0062] In this embodiment, the reset indication signal is valid when the signal is at a high level.

[0063] refer to Figure 4 , the output module 24 includes: a fourth switch tube MP1 and a fifth switch tube MN1. The fourth switch MP1 and the fifth switch MN1 are sequentially connected in series between the power supply voltage VCC input terminal and the reference ground GND, the gate of the fourth switch MP1 receives the first control signal or the second control signal A, and the fifth switch The gate of the tube MN1 receives the second control signal A. The fourth switch MP1 is a depletion-mode PMOS transistor, and the fifth switch MN1 is an enhancement-mode NMOS transistor. And the output module 24 outputs the reset indication signal to the output terminal OUT at the drain of the fourth switch tube MP1.

[0064] Further, in this embodiment, the charge pump 22 generates a reference voltage that is greater than the power supply voltage VCC.

[0065] The specific workin...

Embodiment 3

[0074] In this embodiment, the reset indication signal is valid when it is in a low level state.

[0075] refer to Figure 5 , the output module 24 includes: a first resistor R1 and a third switch tube MN2. The first resistor R1 and the third switch tube MN2 are connected in series between the power supply voltage VCC input terminal and the reference ground GND in sequence, and the gate of the third switch tube MN2 receives the second control signal A. The third switch MN2 is a depletion-mode NMOS transistor. And the output module 24 outputs a reset indication signal at the drain of the third switch tube MN2.

[0076] Further, in this embodiment, the charge pump 22 generates a reference voltage with a negative voltage VSS.

[0077] Compared with the power monitoring circuit 20 in the first embodiment, the power monitoring circuit 20 in this embodiment only replaces the PMOS transistor in the output module 24 with a resistor, and its specific working principle is basically t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More