Source-drain limited epitaxy method, device preparation method, device and equipment

A device and epitaxy technology, applied in the field of GAAFET device manufacturing process, can solve the problems of source/drain layer thickness limitation, etc., and achieve the effect of reducing stress relaxation and reducing mismatch dislocation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

other Embodiment approach

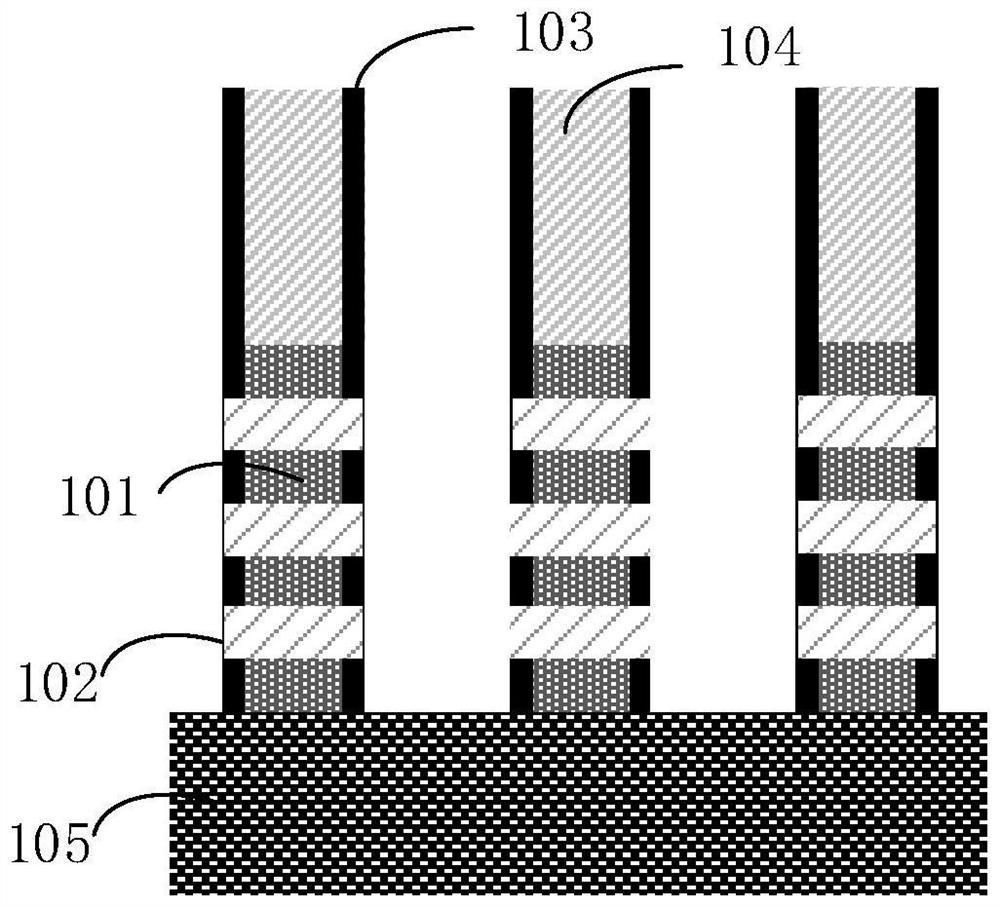

[0091] In other embodiments, the material for forming the first isolation layer may be other isolation materials that can achieve similar isolation effects.

[0092] In an embodiment, the forming the first isolation layer arranged along the first direction between adjacent fin structures specifically includes:

[0093] depositing an isolation layer in the plurality of source / drain cavities;

[0094] CMP processing is performed on the isolation layer; the CMP processing is a polishing process, so that the isolation layers in the plurality of source / drain cavities meet a specified height;

[0095] Photolithography and etching are performed on the isolation layer after the CMP treatment, and only the isolation layer between adjacent fin structures is retained to form the first isolation layer;

[0096] The specific steps of performing photolithography and etching on the isolation layer after the CMP treatment are: covering the surface of the device after the CMP treatment with p...

other Embodiment approach

[0110] In other embodiments, other methods may also be used to selectively etch the sacrificial layer.

[0111] 4) Filling the dummy gate cavity with a metal gate material.

[0112] Before filling the metal gate material in the dummy gate cavity, the method further includes: filling the dummy gate cavity with a high dielectric constant material; the metal gate material covers the high dielectric constant material; the high dielectric constant material Constant material and metal gate (Metalgate, MG) complete the full wrapping of the channel layer;

[0113] In one embodiment, the high dielectric constant material (High-k, HK) is a high-K material; the metal gate material is a widely used material in the prior art.

[0114] CMP processing is performed on the above-mentioned metal gate material and the high dielectric constant material, thereby removing the metal gate material and the high dielectric constant material on the top of the interlayer dielectric layer.

[0115] An e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More