Circuit path level NBTI aging prediction method and device based on key gate

A circuit path and aging prediction technology, which is applied in the circuit field, can solve the problems that the prediction accuracy and speed are difficult to guarantee at the same time, and achieve the effect of reducing training complexity, meeting the prediction accuracy and speed, and reducing the amount of model calculation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

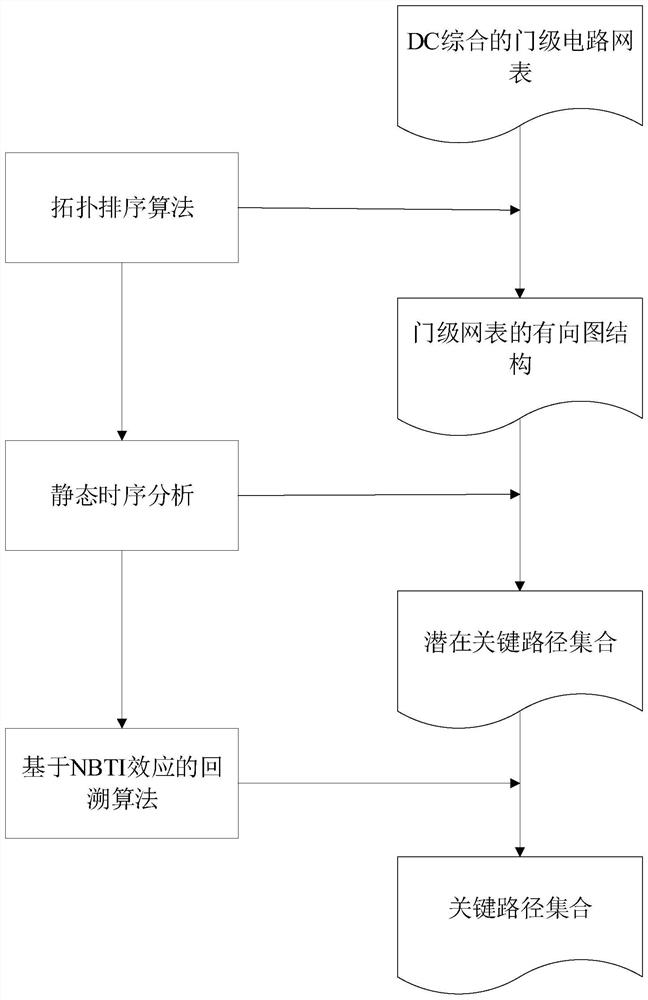

[0058] A circuit-path-level NBTI aging prediction method based on critical gates, the method includes:

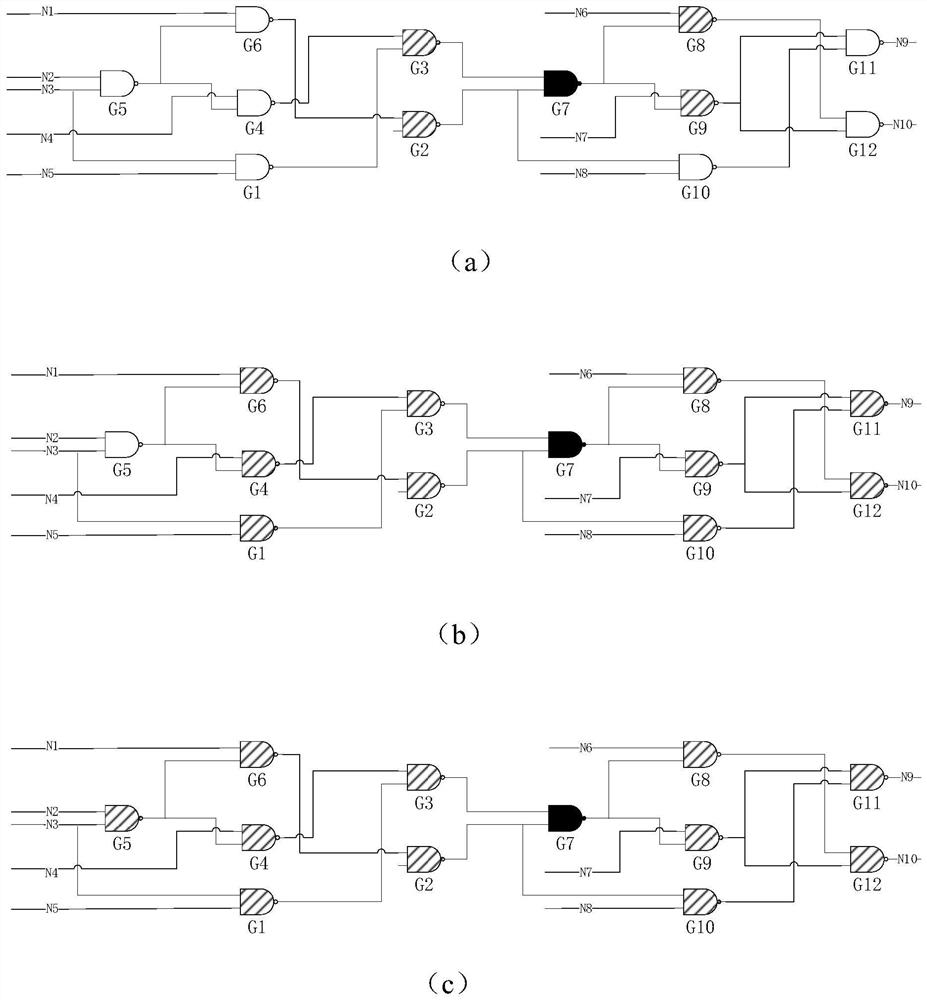

[0059] S1. Obtain key sub-circuits, such as figure 1 As shown, the steps to obtain key subcircuits include:

[0060] A directed graph representation of the circuit is expressed as G=(V, E), V={v i ,1≤i≤n} as a set of nodes, representing the gates in the circuit; E={e j ,1≤j≤m} as a set of edges, representing the connection between gates; first establish the initial set TO i , the v i Join TO i , then the v i The predecessor node and successor node join the set TO i and set TO1 i , TO1 i called v i A layer of topology ring, then TO1 i The predecessor and successor nodes of each node in , and these nodes are not included in TO1 i , adding TO i and TO2 i , TO2 i called v i Layer 2 topology ring, and so on, TO3 i called v i The three-layer topological ring of the final obtained TO i That is, the three-layer ring sub-circuit. Find each node v in the circuit by...

Embodiment 2

[0105] Based on Embodiment 1, Embodiment 2 of the present invention further provides a circuit-path-level NBTI aging prediction apparatus based on critical gates, and the apparatus includes:

[0106] Dataset building blocks for building training and test sets;

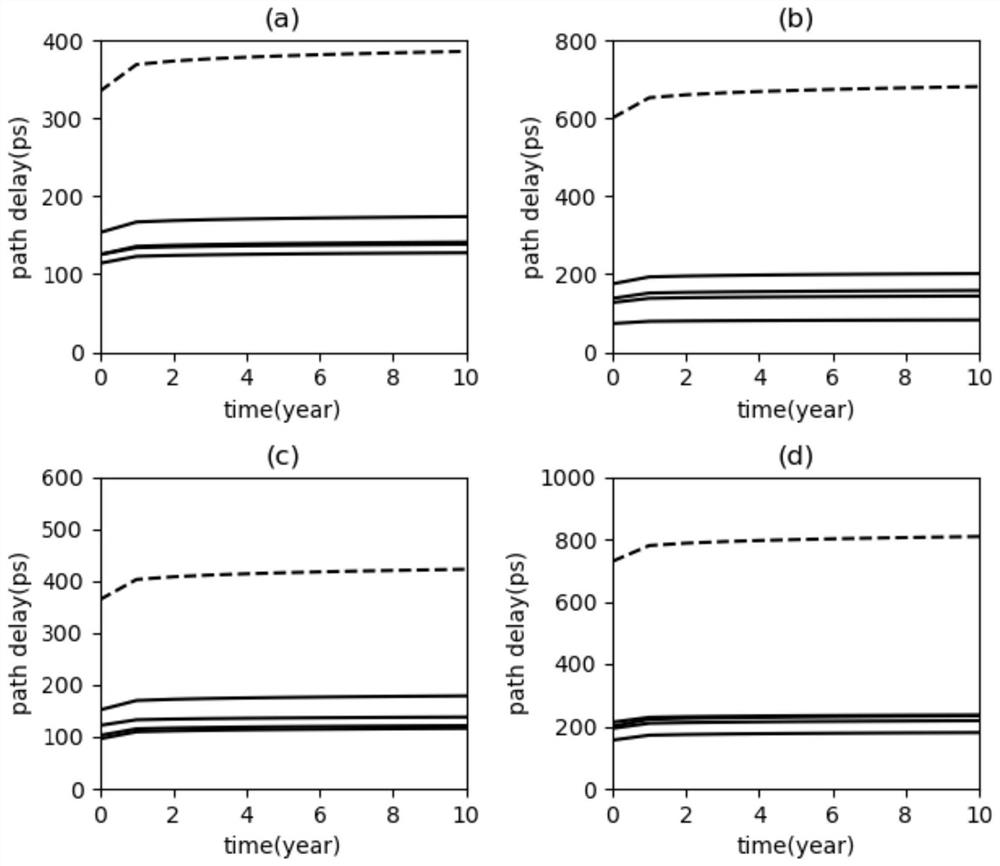

[0107] The training module is used to train the linear regression model using the training set. During the training process, the input of the model is the aging delay data of the 0th and 1st years of the key subcircuit, and the output of the model is the second year of the key subcircuit. The aging delay data to the Nth year, N is a positive integer greater than 2;

[0108] The verification module is used to verify the trained linear regression model using the test set after the training is completed. During the verification process, the input of the model is the aging delay data of the 0th and 1st years of the critical path, and the output of the model is the key The aging delay data of the trail from year 2 to year ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More